# ADA USER JOURNAL

# Volume 35 Number 4 December 2014

# Contents

|                                                                                                                                                     | Page              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                               | 210               |

| Editorial                                                                                                                                           | 211               |

| Quarterly News Digest                                                                                                                               | 212               |

| Conference Calendar                                                                                                                                 | 234               |

| Forthcoming Events                                                                                                                                  | 240               |

| Articles from the Industrial Track of Ada-Europe 2014                                                                                               |                   |

| R. Cholay<br>"AdDoc (beyond a document generator)"                                                                                                  | 246               |

| Proceedings of the "Workshop on Challenges and New Approaches for Dependable an<br>Cyber-Physical System Engineering" of Ada-Europe 2014            | d<br>249          |

| D. Cancila and J-L. Gerstenmayer<br><i>"Editorial"</i>                                                                                              | 250               |

| K. Attwood, P. Conmy and T. Kelly<br>"The Use of Controlled Vocabularies and Structured Expressions in the Assurance                                | of CPS" 251       |

| V. David, A. Barbot and D. Chabrol<br>"Dependable Real-Time System and Mixed Criticality: Seeking Safety, Flexibility a<br>Efficiency with Kron-OS" | nd<br>259         |

| S. Nakajima and M. Toyoshima<br>"Behavioral Contracts for Energy Consumption"                                                                       | 266               |

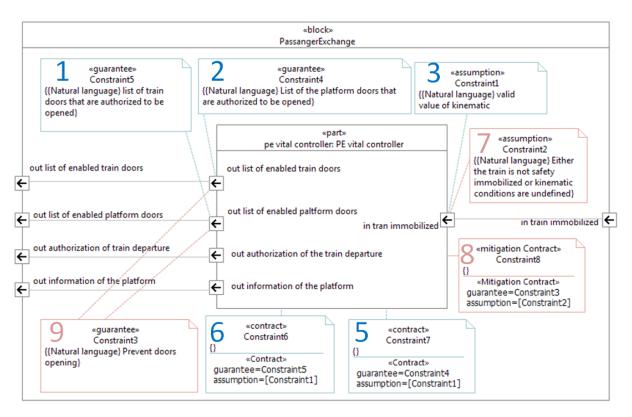

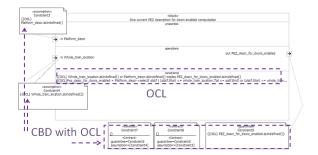

| D. Cancila, E. Soubiran and R. Passerone<br>"Feasibility Study in the Use of Contract-Based Approaches to Deal with Safety-Re<br>Properties in CPS" | elated<br>272     |

| D. Cancila, J-L. Gerstenmayer, C. Robinson and L. Rioux "Round Table"                                                                               | 278               |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                           | 280               |

| Ada-Europe Sponsors                                                                                                                                 | Inside Back Cover |

|                                                                                                                                                     |                   |

# Editorial Policy for Ada User Journal

## Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

## Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj.*

#### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

#### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

#### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

#### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### Announcements and Reports

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### Submission Guidelines

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

This last issue of 2014 publishes the Proceedings of the "Workshop on Challenges and New Approaches for Dependable and Cyber-Physical System Engineering", which took place June 23, co-located with Ada-Europe 2014. This workshop brought together industry and research participants, for a full-day discussion on dependability and critical issues of Cyber-Physical Systems (CPS), a good complement to the already rich program of the conference.

The workshop program included 2 technical sessions with papers from academia and industry, an invited speech by Charles Robinson, of Thales, France, a focused session, and a roundtable discussion. The proceedings reflect part of this rich content, starting with an Editorial by Daniela Cancila and Jean-Louis Gerstenmayer, from CEA LIST, France, followed by a set of technical papers. The first workshop paper, from a group of authors from the University of York and Rapita Systems, UK, which discusses the use of controlled vocabulary and structured expressions for CPS in the automotive domain, to improve understanding between the different teams involved in the development process. The next paper, by authors from Krono-Safe, France, presenting Kron-OS, a real-time kernel, and the associated set of tools, which targets the development of safe mixed-criticality applications. Afterwards, authors from the National Institute of Informatics and DENSO Corporation, Japan, which presents a formal model of energy consumption behavior in mobile platforms, which can be used form contract-based analysis method to detect and remove energy-related bugs. Finally, the last workshop paper from authors from CEA LIST, Technological Research Institute SystemX – Alstom Transport, France, and the University of Trento, Italy, presents a feasibility study feasibility study on the use of contract-based approaches for enforcing safety-related properties in CPS. The proceedings close with a report on the round-table discussion that took place at the workshop.

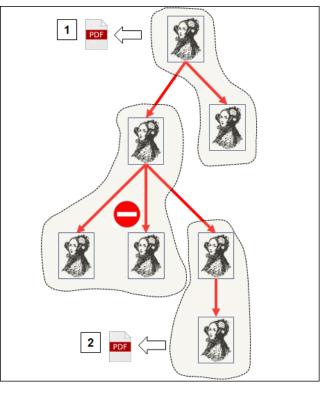

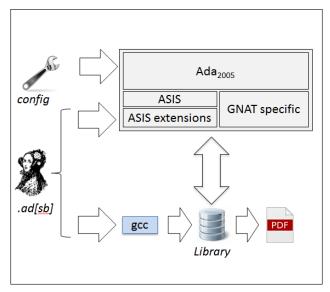

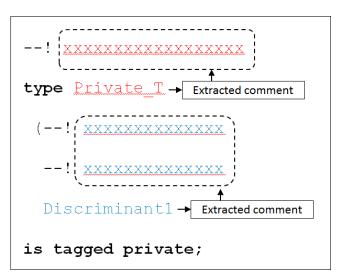

The issue also continues the publication of the contents of the industrial track of Ada-Europe 2014, with a paper by Robert Cholay, describing the AdDoc tool, which was built both to generate documentation and also to check conformance to commenting rules, and that also provides a good example of the use of ASIS.

Finally, and as usual, the issue provides the News Digest, Calendar and Forthcoming Events sections, provided by the News and Events Editors, respectively Jacob Sparre Andersen and Dirk Craeynest. A special mention to the forthcoming events section, with information about the Ada Developer Room at FOSDEM 2015, 31 January 2015, Brussels, Belgium (I take the opportunity to congratulate Ada-Belgium for the important work on promoting Ada within the open source community), the always important International Real-Time Ada Workshop (IRTAW 2015) which will be held in Vermont, USA, April 2015; and obviously Ada-Europe 2015, which will take place at the Universidad Politécnica de Madrid, Spain, 22-26 June 2015: the deadline for submissions is around the corner.

Luís Miguel Pinho Porto December 2014 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

212

212

214

215

221

221

222

223

224

## Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

# Contents

| Ada and Operating Systems<br>References to Publications<br>Ada Inside | Ada-related Organisations<br>Ada-related Events<br>Ada-related Resources<br>Ada-related Tools<br>Ada-related Products |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Ada in Context                                                        | Ada and Operating Systems<br>References to Publications<br>Ada Inside                                                 |  |

# Ada-related Organisations

# Please Submit Contract Assertion Tests to ACATS

From: Randy Brukardt <randy@rrsoftware.com> Date: Tue, 13 May 2014 16:26:37 -0500 Subject: Re: Dynamic\_Predicate failure -> Assertion\_Error? Newsgroups: comp.lang.ada

#### [...]

Well, as this is a weird compiler bug and not an outright mistake in the implementation (since it depends solely on the bounds of the loop - it works properly when no loop is involved), it's not a good candidate for the ACATS. Especially as it seems to be more likely an exception processing problem rather than an assertion problem.

Moreover, AI12-0054-2 and AI12-0071-1 extensively changed the rules in this area (they were much too loose for practical usability). There will need to be tests for those AIs, but they have to wait until AI12-0071-1 is approved by WG 9 (expected in June).

That said, we'd love to have more tests for Ada 2012's contract assertions. A variety of programming styles helps the quality of the ACATS. Contact me at agent@adaauth.org if you need more information, or see Annex E in the ACATS documentation (http://www.adaauth.org/acats-files/3.1/docs/UG-E.HTM).

# Ada-related Events

[To give an idea about the many Adarelated events organised by local groups, some information is included here. If you are organising such an event feel free to inform us as soon as possible. If you attended one please consider writing a small report for the Ada User Journal. —sparre]

# Ada-Europe 2015

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Wed, 2 Jul 2014 21:41:26 +0000 Subject: CfP 20th Conf. Reliable Software Technologies, Ada-Europe 2015 Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

Preliminary Call for Papers

20th International Conference on Reliable Software Technologies Ada-Europe 2015

22-26 June 2015, Madrid, Spain

http://www.ada-europe.org/ conference2015

Organized by Ada-Spain on behalf of Ada-Europe, in cooperation (requests pending) with ACM SIGAda, SIGBED, SIGPLAN and the Ada Resource Association (ARA)

\*\*\* CfP in HTML/PDF on web site \*\*\*

Ada-Europe organizes annual international conferences since the early 80's. This is the 20th event in the Reliable Software Technologies series, previous ones being held at Montreux, Switzerland ('96), London, UK ('97), Uppsala, Sweden ('98), Santander, Spain ('99), Potsdam, Germany ('00), Leuven, Belgium ('01), Vienna, Austria ('02), Toulouse, France ('03), Palma de Mallorca, Spain ('04), York, UK ('05), Porto, Portugal ('06), Geneva, Switzerland ('07), Venice, Italy ('08), Brest, France ('09), Valencia, Spain ('10), Edinburgh, UK ('11), Stockholm, Sweden ('12), Berlin, Germany ('13), and Paris, France ('14).

#### **General Information**

The 20th International Conference on Reliable Software Technologies - Ada-Europe 2015 will take place in Madrid, Spain. Following its traditional style, the conference will span a full week, including a three-day technical program and vendor exhibition from Tuesday to Thursday, along with parallel tutorials and workshops on Monday and Friday.

#### Schedule

11 January 2015: Submission of regular papers, tutorial and workshop proposals

25 January 2015: Submission of industrial presentation proposals

1 March 2015: Notification of acceptance to all authors

29 March 2015: Camera-ready version of regular papers required

12 April 2015: Industrial presentation abstracts required

17 May 2015: Tutorial and workshop materials required

#### **Topics**

The conference has over the years become a leading international forum for providers, practitioners and researchers in reliable software technologies. The conference presentations will illustrate current work in the theory and practice of the design, development and maintenance of long-lived, high-quality software systems for a challenging variety of application domains. The program will allow ample time for keynotes, Q&A sessions and discussions, and social events. Participants include practitioners and researchers representing industry, academia and government organizations active in the promotion and development of reliable software technologies.

Topics of interest to this edition of the conference include but are not limited to:

- Multicore and Manycore Programming: Predictable Programming Approaches for Multicore and Manycore Systems, Parallel Programming Models, Scheduling Analysis Techniques.

- Real-Time and Embedded Systems: Real-Time Scheduling, Design Methods and Techniques, Architecture Modelling, HW/SW Co-Design, Reliability and Performance Analysis.

- Mixed-Criticality Systems: Scheduling methods, Mixed-Criticality Architectures, Design Methods, Analysis Methods.

- Theory and Practice of High-Integrity Systems: Medium to Large-Scale Distribution, Fault Tolerance, Security, Reliability, Trust and Safety, Languages Vulnerabilities.

- Software Architectures: Design Patterns, Frameworks, Architecture-Centred Development, Component-based Design and Development.

- Methods and Techniques for Software Development and Maintenance: Requirements Engineering, Modeldriven Architecture and Engineering,

Formal Methods, Re-engineering and Reverse Engineering, Reuse, Software Management Issues, Compilers, Libraries, Support Tools.

- Software Quality: Quality Management and Assurance, Risk Analysis, Program Analysis, Verification, Validation, Testing of Software Systems.

- Mainstream and Emerging Applications: Manufacturing, Robotics, Avionics, Space, Health Care, Transportation, Cloud Environments, Smart Energy systems, Serious Games, etc.

- Experience Reports in Reliable System Development: Case Studies and Comparative Assessments, Management Approaches, Qualitative and Quantitative Metrics.

- Experiences with Ada and its Future: Reviews of the Ada 2012 new language features, implementation and use issues, positioning in the market and in the software engineering curriculum, lessons learned on Ada Education and Training Activities with bearing on any of the conference topics.

#### Call for Regular Papers

Authors of regular papers which are to undergo peer review for acceptance are invited to submit original contributions. Paper submissions shall not exceed 14 LNCS-style pages in length. Authors shall submit their work via EasyChair following the relevant link on the conference web site. The format for submission is solely PDF.

#### Proceedings

The conference proceedings will be published in the Lecture Notes in Computer Science (LNCS) series by Springer, and will be available at the start of the conference. The authors of accepted regular papers shall prepare camera-ready submissions in full conformance with the LNCS style, not exceeding 14 pages and strictly by March 29, 2015. For format and style guidelines authors should refer to http://www.springer.de/comp/lncs/authors .html. Failure to comply and to register for the conference by that date will prevent the paper from appearing in the proceedings.

The CiteSeerX Venue Impact Factor has the Conference in the top quarter. Microsoft Academic Search has it in the top third for conferences on programming languages by number of citations in the last 10 years. The conference is listed in DBLP, SCOPUS and Web of Science Conference Proceedings Citation index, among others.

#### Awards

Ada-Europe will offer honorary awards for the best regular paper and the best presentation.

#### Call for Industrial Presentations

The conference seeks industrial presentations which deliver value and insight but may not fit the selection process for regular papers. Authors are invited to submit a presentation outline of exactly 1 page in length by January 25, 2015. Submissions shall be made via EasyChair following the relevant link on the conference web site. The Industrial Committee will review the submissions and make the selection. The authors of selected presentations shall prepare a final short abstract and submit it by April 12, 2015, aiming at a 20-minute talk. The authors of accepted presentations will be invited to submit corresponding articles for publication in the Ada User Journal (http://www.ada-europe.org/auj/), which will host the proceedings of the Industrial Program of the Conference. For any further information please contact the Industrial Chair directly.

#### Call for Tutorials

Tutorials should address subjects that fall within the scope of the conference and may be proposed as either half- or fullday events. Proposals should include a title, an abstract, a description of the topic, a detailed outline of the presentation, a description of the presenter's lecturing expertise in general and with the proposed topic in particular, the proposed duration (half day or full day), the intended level of the tutorial (introductory, intermediate, or advanced), the recommended audience experience and background, and a statement of the reasons for attending. Proposals should be submitted by e-mail to the Tutorial Chair. The authors of accepted full-day tutorials will receive a complimentary conference registration as well as a fee for every paying participant in excess of 5; for halfday tutorials, these benefits will be accordingly halved. The Ada User Journal will offer space for the publication of summaries of the accepted tutorials.

#### Call for Workshops

Workshops on themes that fall within the conference scope may be proposed. Proposals may be submitted for half- or full-day events, to be scheduled at either end of the conference week. Workshop proposals should be submitted to the Conference Chair. The workshop organizer shall also commit to preparing proceedings for timely publication in the Ada User Journal.

#### Call for Exhibitors

The commercial exhibition will span the three days of the main conference. Vendors and providers of software products and services should contact the Exhibition Chair for information and for allowing suitable planning of the exhibition space and time

#### Grants for Reduced Student Fees

A limited number of sponsored grants for reduced fees is expected to be available for students who would like to attend the conference or tutorials. Contact the Conference Chair for details.

#### Organizing Committee

See CFP in Forthcoming Events section (pg. 243).

#### Enabling Safety Certification in ARM-based Systems

#### URL: https://event.on24.com

/eventRegistration/EventLobbyServlet? target=registration.jsp&eventid=846366 &sessionid=1&key=818DF79D54BFD1 A3F14610A7B20BF1C8&partnerref=ad acore

Enabling Safety Certification in ARMbased Systems

#### October 8, 2014 2:00 PM EDT

Processor technology from ARM has become a game changer for multiple industries, delivering high-performanceper-watt processing and high levels of integration to enable system on a chip (SoC) capability in a low-power device. This combination has been ideal for small form factor systems in avionics, automotive, and medical applications. Now embedded designers in these markets are looking at ways to take advantage of ARM technology to enable safety certification via standards such as FAA DO-178C for avionics systems and MISRA for automotive systems. This webcast of industry experts will look at how ARM-based solutions can not only reduce power but easily utilize the integrated peripherals in safety certification solutions across different industries.

Sponsors:

#### AdaCore, DDC-I

#### Moderator:

John McHale, OpenSystems Media

# Linux Day 2014 in Cagliari

From: Jacob Sparre Andersen

<jacob@jacob-sparre.dk>

Date: Fri, 24 Oct 2014 17:55:07 +0200

Subject: Ada 2012 talk in Cagliari

tomorrow

Newsgroups: comp.lang.ada

The Linux user group in Cagliari (GULCh) has invited me to give a talk on contract-based programming at the "Linux Day" conference tomorrow (http://linuxday.gulch.it/2014/).

I have promised to make the talk accessible to anybody with programming experience, but the examples and practical possibilities I will discuss are all based on Ada 2012 (with a single SPARK 2014 exception ;-).

Everybody are welcome!

From: Martyn Pike

<usenet@embeddedconsultinguk.com> Date: Sun, 26 Oct 2014 11:31:12 +0000 Subject: Re: Ada 2012 talk in Cagliari tomorrow

Newsgroups: comp.lang.ada

>[...]

How many people attended this talk that you gave ?

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Sun, 26 Oct 2014 18:21:54 +0100 Subject: Re: Ada 2012 talk in Cagliari tomorrow

Newsgroups: comp.lang.ada

>[...]

I think it was somewhere between 30 and 40 people. [Confirmed by the organisers. —sparre]

I've definitely had a more crowded auditorium for an Ada talk in Cagliari, but that was ten years ago, and a possibly more attractive subject (GUI programming).

# FOSDEM 2015

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Sun, 2 Nov 2014 11:13:21 +0000 Subject: CfP - Ada Developer Room at FOSDEM 2015, Brussels, Belgium Newsgroups: comp.lang.ada, fr.comp.lang.ada

Call for Presentations

6th Ada Developer Room at FOSDEM 2015

Saturday 31 January 2015, Brussels, Belgium

http://www.cs.kuleuven.be/~dirk/adabelgium/events/15/150131-fosdem.html

Organized in cooperation with Ada-Europe

Ada-Belgium [1] is pleased to announce that there will be a one-day Ada Developer Room on Saturday 31 January 2015 at FOSDEM 2015 in Brussels, Belgium. This Ada DevRoom is once more organized in cooperation with Ada-Europe [2].

#### General Information

FOSDEM [3], the Free and Open source Software Developers' European Meeting, is a free and non-commercial two-day weekend event organized early each year in Brussels, Belgium. It is highly developer-oriented and brings together 5000+ participants from all over the world. No registration is necessary. The goal is to provide open source developers and communities a place to meet with other developers and projects, to be informed about the latest developments in the open source world, to attend interesting talks and presentations on various topics by open source project leaders and committers, and to promote the development and the benefits of open source solutions.

#### Ada Developer Room

At previous FOSDEM events, Ada-Belgium has organized very well attended Ada Developer Rooms, offering a full day program in 2006 [4], a two-day program in 2009 [5], and full day programs in 2012 [6], 2013 [7] and 2014 [8]. An important goal is to present exciting Ada technology and projects also to people outside the traditional Ada community.

Our proposal for another dedicated Ada DevRoom was accepted, and now work continues to prepare the detailed program. We most probably will have a total of 8 schedulable hours between 10:00 and 18:00 in a room which holds some 60 participants. More information will be posted on the dedicated web-page on the Ada-Belgium site [9], and final announcements will of course also be sent to various forums, lists and newsgroups.

#### Call for Presentations

Ada-Belgium calls on you to:

- inform us at ada-belgiumboard@cs.kuleuven.be about specific presentations you would like to see in this Ada DevRoom;

- for bonus points, subscribe to the Ada-FOSDEM mailing list [9] to discuss and help organize the details;

- for more bonus points, be a speaker: the Ada-FOSDEM mailing list is the place to be!

- Do you have a talk you want to give?

Do you have a project you would like to present?

Would you like to get more people involved with your project? We're inviting proposals that are related to Ada software development, and include a technical oriented discussion. You're not limited to slide presentations, of course. Be creative. Propose something fun to share with people so they might feel some of your enthusiasm for Ada!

Speaking slots are 25 or 50 minutes, including Q&A. Depending on interest, we might also have a session with lightning presentations (e.g. 5 minutes each).

We'd like to put together a draft schedule early December. So, please act ASAP, and definitely by November 30, 2014 at the latest.

We look forward to lots of feedback and proposals!

Dirk Craeynest, FOSDEM Team of Ada-Belgium

Dirk.Craeynest@cs.kuleuven.be (for Ada-Belgium/-Europe/SIGAda/WG9 mail).

http://www.cs.kuleuven.be/~dirk/adabelgium

[2] http://www.ada-europe.org

[3] https://fosdem.org

[4] http://www.cs.kuleuven.be/~dirk/adabelgium/events/06/060226-fosdem.html

[5] http://www.cs.kuleuven.be/~dirk/adabelgium/events/09/090207-fosdem.html

[6] http://www.cs.kuleuven.be/~dirk/adabelgium/events/12/120204-fosdem.html

[7] http://www.cs.kuleuven.be/~dirk/adabelgium/events/13/130203-fosdem.html

[8] http://www.cs.kuleuven.be/~dirk/adabelgium/events/14/140201-fosdem.html

[9] http://www.cs.kuleuven.be/~dirk/adabelgium/events/15/150131-fosdem.html

[10] http://listserv.cc.kuleuven.be/ archives/adafosdem.html

# Ada-related Resources

# **Repositories of Open Source Software**

From: Jacob Sparre Andersen

<jacob@jacob-sparre.dk>

Date: Mon Nov 3 2014

Subject: Repositories of Open Source software

AdaForge: 8 repositories [1]

Bitbucket: 109 repositories [2]

16 developers [2]

Codelabs: 20+ repositories [3]

GitHub: 654 repositories [4]

126 developers [5]

Rosetta Code: 606 examples [6]

28 developers [7]

Sourceforge: 241 repositories [8]

[1] http://forge.ada-ru.org/adaforge

[2] http://edb.jacob-

sparre.dk/Ada/on\_bitbucket

[3] http://git.codelabs.ch/

[4] https://github.com/search?q=language %3AAda&type=Repositories

[5] https://github.com/search?q=language %3AAda&type=Users

[6] http://rosettacode.org/wiki/ Category:Ada

[7] http://rosettacode.org/wiki/ Category:Ada User

[8] http://sourceforge.net/directory/ language%3Aada/

[See also "Repositories of Open Source Software", AUJ 35-3, p. 153. —sparre]

# Ada on Social Media

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Wed Nov 5 2014 Subject: Ada on Social Media

Ada groups on various social media:

- LinkedIn[1]: 2\_052 members

- Reddit[2]: 726 readers

- Google+[3]: 348 members

- StackOverflow[4]: 264 followers

- Twitter[5]:1 twitter

[1] http://www.linkedin.com/groups? gid=114211

- [2] http://www.reddit.com/r/ada/

- [3] https://plus.google.com/communities/ 102688015980369378804

[4] http://stackoverflow.com/questions/ tagged/ada

[5] https://twitter.com/search?f=realtime &q=%23AdaProgramming

[See also "Social Media Sites", AUJ 34-2, p. 64. —sparre]

## **Open Source Build Server Status**

From: Tero Koskinen <tero.koskinen@iki.fi> Date: Thu Nov 6 2014 Subject: Jenkins URL: http://build.ada-language.com/ [Builds: —sparre]

- Ahven - Debian 7.0 - GNAT 4.6

- Ahven JNT

- Ahven Win7 GNAT2013

- Ahven Win7 ICCAda

- JD\_JNT

- Jdaughter Debian 7.0 GNAT 4.6

- Jdaughter\_Win7\_ICCAda

- Lace Win7 ICCAda

[Fails to build: --sparre]

- AVR-Ada Debian 7

- Strings Edit ICCAda

- UnzipAda Win7 GNAT2013

- UnzipAda\_Win7\_ICCAda

[See also "Experimental Continuous Integration System for Open Source Projects", AUJ 35-1, p. 6. —sparre]

# Ada-related Tools

# **Statistics Libraries**

From: Poul-Erik Andreasen <poulerik69@gmail.com> Date: Mon, 07 Apr 2014 16:34:27 +0200 Subject: Statistics Newsgroups: comp.lang.ada What do people here use when they need statistics. I am specially interested in Probability Kernel Density functions.

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Tue, 8 Apr 2014 14:34:55 -0700 Subject: Re: Statistics Newsgroups: comp.lang.ada

>[...]

You may want to have a look at MathPaqs:

http://sf.net/projects/mathpaqs/

there is a "samples" packages in the stats subdirectory. No KDE so far, though, just plain histograms. There are also some random simulation tools.

[See also "Excel Writer, GNAVI, Mathpaqs and Zip-Ada", AUJ 34-4, p. 200. —sparre]

From: Poul-Erik Andreasen <poulerik69@gmail.com> Date: Wed, 09 Apr 2014 02:24:54 +0200 Subject: Re: Statistics Newsgroups: comp.lang.ada

> [...]

That may be just what I need. I have decided to make the KDE myself. The math is not that awful. The formulas are on Wikipedia and most of what I need is in Ada.Numerics. I will take look at Mathpags to see if there is some useful stuff for me there.

From: Simon Wright <simon@pushface.org> Date: Wed, 09 Apr 2014 07:37:30 +0100 Subject: Re: Statistics Newsgroups: comp.lang.ada

#### >[...]

If you need asymmetric matrices, you might find Ada 2005 Math Extensions useful.

http://sourceforge.net/projects/ gnat-math-extn/

[See also "Ada 2005 Math Extensions", AUJ 34-3, p. 138. —sparre]

From: Poul-Erik Andreasen <poulerik69@gmail.com> Date: Wed, 09 Apr 2014 23:58:32 +0200 Subject: Re: Statistics Newsgroups: comp.lang.ada

>[...]

I will take a look at it. The vector types may be useful.

[See also "Mathematics and Statistics", AUJ 34-4, p. 203. —sparre]

# **PDF Writer**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Thu, 10 Apr 2014 22:33:00 +0200 Subject: Re: Writing PDF files Newsgroups: comp.lang.ada > [...] Gtk supports PDF surfaces in Cairo. For example:

http://www.dmitry-kazakov.de/ ada/aicwl.htm#12.6

does plotting, in particular, into PDF.

In general, whatever output generated by Cairo (Cairo is vector graphics library used in Gtk), it can be rendered on a PDF surface, i.e. in a PDF file.

From: Bill Findlay

<yaldnif.w@blueyonder.co.uk>

Date: Thu, 10 Apr 2014 22:47:05 +0100

Subject: Re: Writing PDF files

Newsgroups: comp.lang.ada

>[...]

I gave up on PDF and implemented a very small subset of Encapsulated PostScript that was good enough for my very simple requirements (emulating a Calcomp plotter of the early 19060s).

From: Gautier de Montmollin

<gautier.de.montmollin@gmail.com> Date: Sun, 13 Apr 2014 01:46:59 -0700 Subject: Re: Writing PDF files Newsgroups: comp.lang.ada

> soon a PDF with "hello world"...

http://sf.net/p/apdf/code/HEAD/tree/

More soon (or not soon) ...

# LZMA

From: Gautier de Montmollin

<gautier.de.montmollin@gmail.com> Date: Mon, 30 Jun 2014 07:43:21 -0700 Subject: Re: Q: LZMA in Ada ? Newsgroups: comp.lang.ada

Just to answer my own question ;-) : there are now \*two\* implementations for decoding LZMA. In chronological order, in the following libraries:

Matreshka: http://forge.ada-ru.org/ matreshka/browser/trunk/design/filters

[See also "Matreshka", AUJ 35-1, p. 8. —sparre]

- Zip-Ada: http://unzip-ada.sf.net

[See also "Zip-Ada", AUJ 35-3, p. 157. —sparre]

# STM32F4 Discovery

From: Roy Emmerich <roy.emmerich@gmail.com> Date: Tue, 26 Aug 2014 15:38:33 -0700 Subject: STM32F4 Discovery, communication and libraries

Newsgroups: comp.lang.ada

I discovered Ada 2 days ago, so stick with me.

I am starting a business which will focus on creating a cheap, modular, open source data logger/controller usable across multiple domains. At the moment I am in the prototyping stage, using the following hardware:

1. STM32F4 Discovery board

2. MikroElektronika STM32F4 Discovery shield (http://www.mikroe.com/stm32/ stm32f4-discovery-shield/)

3. Various MikroElektronika click boards (http://www.mikroe.com/click/):

\* GPS click board (ublox LEA-6S receiver)

- \* microSD

- \* RS485

- \* RS232

- \* Ethernet

I don't have experience in C/C++ but I do have a lot of experience in Java, python, structured text (read PLCs) and a few other bits and pieces. I REALLY don't want to develop in C. From what I can make out it looks like a nightmare once the code reaches any substantial size, which mine will. I've started quite a few beginner C books and never got very far before throwing in the towel. However what I've read about Ada has certainly caused me to sit up!

So far I have investigated the following high level language alternatives:

- 1. www.espruino.com (JavaScript)

- 2. www.micropython.org

- 3. www.eluaproject.net

At the moment I am forging ahead with Espruino because:

1. it is quick to get code on the processor as it is interpreted

2. interfacing with external hardware via SPI/I2C/UART is easy...except when you want to access on-chip functionality that isn't yet supported by the Espruino interpreter (which is aimed at STM32F1 powered Espruino board, partially ported to the STM32F4).

3. www.npmjs.org has so many libraries and examples of how to get things done (e.g. MODBUS RTU library...done) which translates to many willing hands/minds.

but I see dragons on the horizon. Here are a few:

1. It is not hard real-time

- 2. Although you can minify the code, I am uncertain whether everything will fit on when the code base grows.

- 3. JavaScript on microcontrollers has no track record.

In short, nice for tinkering/prototyping but probably not a wise choice for the long run.

Today I started chatting to Mike Silva over at EmbeddedRelated:

http://www.embeddedrelated.com/ showarticle/617.php

For Ada to be a viable option for my project, this is what I think I need [with Mike's comments]:

1. [IN PROGRESS] Easy communication: SPI, I2C, Serial, Ethernet,

[Mike] I know that AdaCore is working on comms libraries for the ARM Cortex M parts, but I don't know anything about the projected availability.

[Roy] If they want adopters then they'd better get a move on!

2. [UNSOLVED?] Libraries/examples: MODBUS RTU/Eth at the very least

I have yet to find a repository of libraries covering the major protocols (e.g. MODBUS, CAN, one-wire). There are quite a few in C. Would it be viable to just wrap these in Ada? It seems like a great short term solution but if we are using Ada to make things more stable, it hardly makes sense to use it merely to wrap (flakey) C libraries ;)

[Mike] It is also true that you can link to C code in Ada with either thin or thick wrappers. A thin wrapper just converts each C function to an equivalent Ada subprogram, while a thick wrapper adds one or more higher-level layers on top of the basic subprograms.

3. [SOLVED] Direct access to chip functionality: STM32F4 RTC, Precision Time Protocol capabilities on chip, etc. I read that binding in C code is fairly easy? That would allow me to directly call the STM32 C drivers provided by STM?

[Mike] In any case, you will have no problem accessing the chip hardware in Ada.

4. [SOLVED] Someone hosts an open forum to encourage the exchange of ideas, providing an alternative to the normally clandestine military/large corporate approach to code development. If Ada is going to grow then it needs to open up to your average Joe like me.

[Mike] comp.lang.ada!

I'd appreciate any further feedback from members of this list.

From: Luke A. Guest <laguest@archeia.com> Date: Wed, 27 Aug 2014 02:40:48 +0000 Subject: Re: STM32F4 Discovery, communication and libraries Newsgroups: comp.lang.ada

You might be interested in <https://github.com/rowsail/ AdaForMicrocontrollers> which is being discussed between some of us on LinkedIn in the Ada for micro controllers group.

From: Mike Silva <embeddedrelatedmike@scriptoriumdes igns.com> Date: Wed, 27 Aug 2014 09:17:24 -0700 Subject: Re: STM32F4 Discovery, communication and libraries

Newsgroups: comp.lang.ada

The problem with reuse is that it is hardly ever as clean and simple as one would hope. In my experience, by the time you find some code, determine if it meets your needs, identify the areas that will need to be changed, and figure out how to bind to it if in C, it would have been quicker to write the code from scratch (perhaps using the code you found as a general guide). I don't claim that's a universal, just my experience.

For example, on the MODBUS drivers, I've used such code in the past, and even though our company paid for custom drivers, we spent a lot of time fixing and adjusting them. I doubt we gained anything over writing from scratch (using whatever code we could have found as a guide).

Speaking of reuse, since you're just discovering Ada, you should read about the Ariane 5 reuse fiasco (which some people foolishly tried to blame on the use of Ada, but which is really about the perils of reuse of perfectly good code).

From: Jonathan

<johnscpg@googlemail.com> Date: Fri, 29 Aug 2014 12:36:09 -0700 Subject: Re: STM32F4 Discovery, communication and libraries

Newsgroups: comp.lang.ada

[GNATColl contains Ravenscar support packages.]

The code itself looks intimidating, but most of the .ads files have sample code that shows how to use them. Here's the list:

gnatcoll-ravenscar-utils.ads

gnatcoll-ravenscar-utils.adb

gnatcoll-ravenscar-timersone shot timer.ads

gnatcoll-ravenscar-timersone shot timer.adb

gnatcoll-ravenscar-timers.ads

gnatcoll-ravenscar-

timed\_out\_sporadic\_server.ads

gnatcoll-ravenscar-

timed\_out\_sporadic\_server.adb

gnatcoll-ravenscarsporadic\_server\_with\_callback.ads

gnatcoll-ravenscar-

$sporadic\_server\_with\_callback.adb$

gnatcoll-ravenscar-sporadic\_server.ads gnatcoll-ravenscar-sporadic\_server.adb

gnatcoll-ravenscar-

simple\_sporadic\_task.ads

gnatcoll-ravenscar-

simple\_sporadic\_task.adb

gnatcoll-ravenscar-simple\_cyclic\_task.ads

gnatcoll-ravenscarsimple\_cyclic\_task.adb

gnatcoll-ravenscar-

multiple\_queue\_sporadic\_server.ads

gnatcoll-ravenscarmultiple\_queue\_sporadic\_server.adb

gnatcoll-ravenscarmultiple\_queue\_cyclic\_server.ads

gnatcoll-ravenscarmultiple\_queue\_cyclic\_server.adb

gnatcoll-ravenscar.ads

Also <http://www.adacore.com/ adaanswers/gems/gem-89-codearchetypes-for-real-time-programmingpart-1/> might help.

# Deepend

From: Brad Moore

<brad.moore@shaw.ca> Date: Sun, 07 Sep 2014 19:27:26 -0600 Subject: ANN: Deepend 3.4 Storage Pools Newsgroups: comp.lang.ada

I am pleased to announce the availability of Deepend version 3.4.

Deepend is a suite of dynamic storage pools with subpool capabilities for Ada 95, Ada 2005, and Ada 2012. Bounded and unbounded storage pools types are provided. Storage pools with subpool capabilities allow all objects in a subpool to be reclaimed all at once, instead of requiring each object to be individually reclaimed one at a time. Deepend storage pools provides a more efficient and safer scheme for storage management than relying on the standard storage pool, and user calls to Unchecked Deallocation. In fact, Deepend can eliminate the need for Unchecked Deallocations. A Dynamic Pool may have any number of subpools.

Deepend can be downloaded from;

https://sourceforge.net/projects/ deepend/files/

Differences since last release include;

This is technically the first version of Deepend that compiles for Ada 2012 and the GNAT GPL 2014 version of the compiler. In particular,

- The Pool parameter of the System.Storage\_Pools.Subpools.Default \_Subpool\_For\_Pool function was finalized to be an in out parameter for the Ada 2012 standard. This requires changes to the Deepend pools, since they override this function. In addition, the Ada 2005 and Ada 95 versions of Deepend also were modified to reflect this change. In Ada 95 and Ada 2005, functions cannot have in out parameters, so instead, the parameters were changed to be access parameters, so that the Ada 95 and Ada 2005 version more closely matches the Ada 2012 version.

- In the Ada 2012 version, there were static\_predicates defined for private declarations, which in fact needed to be dynamic\_predicates. Since these were private declarations, the predicates were removed, since they weren't very useful since they were private declarations, and

the need for dynamic checks for this was deemed as worthwhile.

- Removed workarounds for GNAT compiler bugs that were fixed in the GNAT GPL 2014 version of the compiler. In particular, the storage pools have default discriminants which now can be left unspecified to use the defaults.

[See also "Deepend", AUJ 35-1, p. 7. —sparre]

## **GNAT for More ARM** Variants

From: gnlnops@gmail.com Date: Mon, 8 Sep 2014 14:25:29 -0700 Subject: Re: GNAT SPARK:Embedded ARM Ada Project doesn't run in STM32F429 Discovery Board

Newsgroups: comp.lang.ada

If you are interested I perform the port of Ada runtime library and the demo\_leds example. As Jerry wrote the RCC module is a little bit different on the STM32F42x and the origin of the problem came from the voltage scaling operation during initialization.

The main modifications were:

- PLL configuration,

- Add of the 9 new interrupt sources,

- Link command files,

- USART1 configuration update (from GPIOB to GPIOA).

For recall the pins are:

- LED3: PG13,

- LED4: PG14,

- USART1\_TX: PA9,

- USART2 RX: PA10.

The LEDs and user button work correctly but I do not test the USART1 yet because I have no  $TTL \leq RS232$  converter.

The files are available on GitHub:

https://github.com/gnlnops/gnatstm32f429i-disco

From: Brian Drummond

<brian@shapes.demon.co.uk>

Date: Sat, 11 Oct 2014 10:53:49 GMT

Subject: Re: Newcomers to comp.lang.ada:

welcome and how did you end up here ?

Newsgroups: comp.lang.ada

[...]

One piece of possibly good news: There's a LinkedIn thread where - just possibly - a critical mass of developers are getting together. Including Luke and others with some serious interest and past track record.

On this group, see the threads "Group development and porting of the RTS using GNAT GPL for ARM" and "http://www.AdaForMicrocontrollers.com now "Live". https://www.linkedin.com/groups?home= &gid=2188035&trk=anet\_ug\_hm

They reference a currently not-very-lively forum:

https://www.adaformicrocontrollers.com/

and a Github repo:

https://github.com/rowsail/ AdaForMicrocontrollers

[See also "Blog Entries on STM32F4 Programming", AUJ 35-3, p. 162. —sparre]

# **Simple Components**

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Tue, 16 Sep 2014 22:08:21 +0200 Subject: ANN: Simple Components for Ada v4.2

Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, multiple connections server designing tools. It grew out of needs and does not pretend to be universal. Tables management and strings editing are described in separate documents see Tables and Strings edit. The library is kept conform to the Ada 95, Ada 2005, Ada 2012 language standards.

http://www.dmitry-kazakov.de/ ada/components.htm

Changes to the previous version:

- Transactional block files provided by the package

- Persistent.Blocking\_Files.Transactional;

- Persistent.Memory\_Pool provides tasksafe access to the underlying container file;

- Persistent.Memory\_Pool.

Generic\_External\_B\_Tree is changed to support multiple trees on the same pool;

- Various bug fixes and code cleanup.

[See also "Simple Components", AUJ 35-3, p. 154. —sparre]

# **Persistent Memory Pools**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 17 Sep 2014 18:51:21 +0200 Subject: Ada vs SQLite3 benchmark Newsgroups: comp.lang.ada

I posted benchmark of Ada persistent Btree vs. SQLite3 at Ada Programming blog: http://ada-programming.blogspot.de/ 2014/09

The implementation of B-tree is based on Ada.Direct\_IO with a transaction layer, e.g. for safety against system failure.

From: Emmanuel Briot

<briot.emmanuel@gmail.com>

Date: Thu, 18 Sep 2014 01:08:46 -0700

Subject: Re: Ada vs SQLite3 benchmark

Newsgroups: comp.lang.ada

Why did you run the benchmarks without optimization? That seems inconsistent. If you are measuring performance, you should run with full optimization on I think.

Also, it would be interesting to use the following pragmas (combined or not) in SQLite, since they can impact performance significantly:

pragma journal\_mode=WAL;

pragma synchronous=OFF;

(unless the Ada code is also running fsync() regularly)

I think the latter in particular will significantly change the time measured for SQLite.

But I agree with your conclusion that Ada is a viable alternative here, thanks for the experiment!

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Thu, 18 Sep 2014 22:08:50 +0200 Subject: Re: Ada vs SQLite3 benchmark Newsgroups: comp.lang.ada

> Why did you run the benchmarks without optimization? [...]

Optimization could remove or rearrange parts of code which would not happen in a real-life case. For example doing something like

for I in 1..1000 loop N := I; end loop;

could be optimized to N := 1000.

IMO, not optimized code is a better measure for algorithmic complexity.

>[...]

> pragma journal\_mode=WAL;

> pragma synchronous=OFF;

>[...]

Thanks for pointing this out.

Regarding Ada, it was strictly Ada.Direct\_IO, nothing else. Ada.Direct\_IO does not have Flush[\*]. As far as I can tell GNAT's implementation of Ada.Direct\_IO.Write is fwrite not followed by fsync. So forcing SQLite to sync might be unfair. However, the intended use surely must sync upon commit.

[\*] Maybe it is worth an AI to add Flush to Direct\_IO.

## **Data-structure Benchmark**

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Wed, 17 Sep 2014 18:15:15 -0700 Subject: B-Tree v Skip-List Insertion Benchmark

Newsgroups: comp.lang.ada

I ran a quick comparison of the insertion times for Kazakov's Generic\_B\_Tree pkg against

PragmARC.Skip\_List\_Unbounded from the PragmAda Reusable Components.

Both data structures are used for similar purposes, allowing O(log N) look-up times. Insertion and deletion are expensive operations on balanced trees due to re-balancing, and one reason skip lists were invented was to have fast insertion and deletion times compared to balanced trees. I had never actually compared times, and Kazakov's recent post comparing DB times got me thinking about it.

A typical run inserting the same 1,000 items into both structures gives times of

1.484 ms for the B tree

0.709 ms for the skip list

(Divide by 1,000 for average per-insertion times.)

The trade off is similar to using heap sort or quick sort. Both are O(N log N), with quick sort usually being faster. Heap sort is always O(N log N), but in rare cases, however, quick sort has worst-case performance of O(N\*\*2).

A skip list is probabilistically balanced, and has a worst-case search time of O(N) in very rare circumstances, almost always for small N (< 256).

[See also "PragmAda Reusable Components", AUJ 35-3, p. 154. —sparre]

#### Gnoga

From: David Botton <david@botton.com> Date: Tue, 23 Sep 2014 11:20:39 -0700 Subject: Gnoga - The GNU Omnificent GUI for Ada

Newsgroups: comp.lang.ada

This is not an announcement of a 1.0 yet, but a progress report. It helps me stay focused and motivated along with a source for ideas and inspiration to post things, so here we go.

BTW, you can play the snake game running in Ada now over the internet, http://www.gnoga.com - NO JS and HTML that is done with Gnoga bindings to the Canvas and DOM.

I am busy working on the code at the moment so the documentation is mainly in the specs and samples for the moment and I have not had time to make a nice website for it yet, however http://www.gnoga.com is there and a link to the sourceforge site.

An introduction to what it is:

- 1. First and foremost the project goal is a cross platform GUI toolkit. but Instead of targeting Windows, X, Gtk or Qt, it targets the HTML5 browser. No not HTML or JS, the "browser". It acts like a "terminal" for Gnoga to render its magic. If you try and do a view source on the browser all you will get is the websocket code used to set up the communications. Long term you will be able to package a native app (.exe, .app, etc.)

- 2. Because the "browser" is the target it means that Gnoga applications can run local or remote. If you can get AWS running on your "board" you can use Gnoga for the front end. Yes you could write HTML and respond to HTTP requests etc using AWS, but with Gnoga your app is always connected and live in the browser back to the server. You can be showing real time stats, no Ajax, JSON, etc to worry about, oh yes and all of it is in Ada you don't have to touch those sick little braces { } pocked with ;;;;;

- 3. It just happens to be that Gnoga can also create great websites with dynamic content using HTML, CSS and Ada (that's right not JS)... It's a nice bonus.

- 4. In fact Gnoga comes already with a number of Ada on Rails like features. Including Active Record support with bindings to MySQL and SQLite and can easily be expanded to other SQL engines.

- 5. There is a whole lot there already but.. there is still a lot more to go. Don't pass judgment till at least all the components are in, 6-8 weeks.

- 6. With this you will get things like OpenGL programming via WebGL (coming), it already has a full canvas 2d binding, and any other techi goodness thrown at the web.

- 7. Multimedia bindings are not far behind for video, audio, etc.

- 8. You will get access to client side HTML5 goodness like local storage on the client browser, etc. it's all coming.

- 9. Gnoga can easily use now or be extended later to bind anything that can run in a browser, JS GUI toolkits, XUL for direct native apps, etc. etc.

- 10. While most of the world is fighting to get JS and HTML to run and do anything, Ada get's to sit back and enjoy the ride to every new tech as it comes and still have a solid language and the ability to create secure Web apps and services dispatched from solid systems.

It's tough to get the full vision in words and there are not too many pictures to see, but if I get you excited about Ada for application development, well than I'm getting somewhere and we will both arrive soon enough at the goal :)

From: David Botton <david@botton.com> Date: Sun, 28 Sep 2014 19:42:28 -0700 Subject: Re: Gnoga - The GNU Omnificent GUI for Ada

Newsgroups: comp.lang.ada

Today's update:

1) I have made numerous fixes to make sure the Ada code is compliant with my Ada coding standards.

2) I've made a number of bug fixes

3) I added a Console like View type with auto scrolling as elements added to bottom

4) I've added the first 2 tutorials on how to code in Gnoga: http://sourceforge.net/p/gnoga/code/ci/m aster/tree/tutorial/

5) I've made the audio and video types functional, although they need some more specific events and properties.

6) I added local client side storage support and session support based on sessionStorage.

From: David Botton <david@botton.com> Date: Mon, 29 Sep 2014 20:31:35 -0700 Subject: Re: Gnoga - The GNU Omnificent GUI for Ada

Newsgroups: comp.lang.ada

Today's Updates :)

1) 2 more Tutorials

2) Views will now deallocate dynamically created child objects on finalization

- 3) Moved Gnoga.Application.Multiuser to Gnoga.Application.Multi\_Connect

- 4) Modified how app data is set for connections to now use the Main\_Window, it will also deallocate it if dynamically created on finalization.

- 5) It is no longer necessary to use Connection.Hold unless desired for clean up on connection events.

In general as I am writing the tutorials I am doing as much as possible to simplify the API and make coding easier in Gnoga.

Here are a list of planned tutorials so far (the first 4 are now done and in the repo)

Tutorial-01 - Introduction to Gnoga applications

Tutorial-02 - Introduction to Event Handlers

Tutorial-03 - Introduction to Multi-Connection Apps

Tutorial-04 - Tasking and Gnoga

Tutorial-05 - Using the Canvas Control

Tutorial-06 - Popups windows, iFrames, and custom boot files with Gnoga

Tutorial-07 - Forms and Gnoga

Tutorial-08 - Database bindings and Schema Migrations using Gnoga Tutorial-09 - Active Record - Data modeling in Gnoga

Tutorial-10 - Creating MVC apps and Sessions management in Gnoga

In each tutorial directory there is a README that summarizes additional aspects of Gnoga learned in that tutorial. It is worth reading through the READMEs and sources in each tutorial in order as they build on each other. They also teach far more than just their subject line about things you can do with Gnoga.

From: David Botton <david@botton.com> Date: Tue, 30 Sep 2014 17:22:27 -0700 Subject: Re: Gnoga - The GNU Omnificent GUI for Ada

Newsgroups: comp.lang.ada

So far for today added:

1) Ability to remove event handlers by setting to null

2) Corrected some bugs

3) Added Tutorial 05 - A quick little canvas drawing application to demonstrate the canvas and mouse events.

From: David Botton <david@botton.com> Date: Sun, 12 Oct 2014 23:05:36 -0700 Subject: Re: Gnoga Latest Updates Newsgroups: comp.lang.ada

Tutorial 09 Added

Learn about:

1) Interactive Forms

2) Tabs and the Card View

3) Using the Docker view for layout

From: David Botton <david@botton.com> Date: Sat, 18 Oct 2014 21:40:02 -0700 Subject: Re: Gnoga Latest Updates Newsgroups: comp.lang.ada

Tutorial 10 added

Illustrates:

1) Database bindings in Gnoga

2) Use of database migrations

From: David Botton <david@botton.com> Date: Sun, 19 Oct 2014 16:02:39 -0700 Subject: Re: Gnoga Latest Updates Newsgroups: comp.lang.ada

As of this last update:

- 1) I have added a simple all Ada template parser (so now possible to use PHP, Python or a simple token replace for text parsing)

- 2) It is no long required that you cd in to the bin directory to execute a gnoga application

- 3) The executable can be in a bin subdirectory or at the application root directory

- 4) Any missing sub directories (/js, /img, /css) are assumed to be in /html, if /html is also missing all files are assumed to be in the applications root directory. (e.g. you could place the snake

executable and boot.html in the same directory and snake will run with no issue now)

From: David Botton <david@botton.com> Date: Sun, 19 Oct 2014 21:36:02 -0700 Subject: New Gnoga Tool - gnoga\_make Newsgroups: comp.lang.ada

It's now even easier to write Gnoga apps with a new tool that is part of Gnoga gnoga\_make

Gnoga\_Make works on Mac, Linux and Windows.

Gnoga\_Make currently creates only one type of scaffolding for Gnoga apps a multi\_connect app. There will be many more added before 1.0 in the next few weeks. (BTW, these scaffold apps also demonstrate good methods for developing Gnoga apps)

Example use:

Install Gnoga:

git clone git://git.code.sf.net/p/gnoga/code gnoga-code

cd gnoga-code

make install

(if on Mac / Unix and needed sudo make install)

This will build and install Gnoga as a standard gnat package and install gnoga\_make in gnat/bin

With gnat/bin on your command line:

gnoga\_make new My\_New\_App multi connect

This will create a directory called my\_new\_app and create all the need files for a gnoga multi\_connect application including makefiles, project files, etc.

cd my\_new\_app

make

bin/my\_new\_app

From: David Botton <david@botton.com> Date: Thu, 23 Oct 2014 23:07:31 -0700 Subject: Cairo Bindings now added to Gnoga

Newsgroups: comp.lang.ada

I've adopted the Cairo bindings from GtkAda for Gnoga.

This adds in a quick instant tons of functionality for vector graphics. This of course is a great fit since Cairo will produce SVG in addition to PNG and PDFs so a really great fit.

I'll be adding a thicker layer to it for easier use in general and for Gnoga.

Cairo libs are usually installed already on Linux, for Mac I use home brew - brew install cairo and brew install libsvg-cairo for Windows install GtkAda even though not dependant on it, it installs all the needed libs for cairo.

# **Permutation Generators**

From: jpwoodruff@gmail.com Date: Fri, 3 Oct 2014 11:50:30 -0700 Subject: Re: Permutation generator in ada library

Newsgroups: comp.lang.ada

- > Does Ada have a built-in function that given an integer N creates all possible permutations.

- > I found this <http://rosettacode.org/wiki/Permutatio ns#The\_generic\_package\_Generic\_Per m>, but was wondering if I can just call

a built-in function? I can address the original issue about permutation-generating Ada.

One is contained in the library Charles built by Matthew Heany: http://home.earthlink.net/ ~matthewjheaney/charles/index.html

His last update was in 2004. The materials are at: http://charles.tigris.org/source/browse/charles/src/

The second is by Mats Weber. My copy carries dates to 1990. Mats Weber's Ada Component Library, version 2.0: http://mats.weber.org/ada/ mw\_components.html

His document says:

Copyright (c) 1999 Mats Weber, Ch. du Grillon 10, 1007 Lausanne, Switzerland. These components were originally developed by Mats Weber at EPFL (Swiss Federal Institute of Technology, Computer Science Theory Laboratory and Software Engineering Laboratory) from 1985 to 1990

They carry the GNU General Public License.

My oldest holding is an archeological remnant from Simtel 20, built by Doug Bryan.

"This software is released to the Public Domain" but I don't know where there is a public copy. I'd be happy to share with anyone interested.

-- Unit name : Permutations\_Class

- -- Version : 1.0

- -- Author : Doug Bryan

- -- : Computer Systems Lab

- -- : Stanford University

- -- : Stanford CA, 94305

- -- DDN Address : bryan@su-sierra

- -- Copyright : (c) -none-

- -- Date created : 15 April 1985

- -- Release date : 15 April 1985

- -- Last update : 15 April 1985

- -- Machine/System Compiled/Run on :

- -- DG MV/10000 ADE 2.2

#### generic

package Permutations\_Class is

generic

with procedure Process (A\_Permutation : List\_Type); procedure Iterate\_Through\_Length\_ Factorial\_Permutations (Of\_Items : List\_Type);

- -- For an actual parameter for Of\_Items

- -- of length n, n! (n factorial) -- permutations will be produced.

- -- The procedure permutes the elements

- -- in the array ITEMS.

- -- actually it permutes their indicies and

- -- re-arranges the items within the list.

- -- The procedure does not care of any or all

- -- of the items in the list are equal

- -- (the same).

#### end Permutations\_Class;

From: Dirk Craeynest

<dirk@cs.kuleuven.be> Date: Sat, 4 Oct 2014 18:06:58 +0000 Subject: Re: Permutation generator in ada library

Newsgroups: comp.lang.ada

The code by Doug Bryan, that John mentions at the end of his posting, was included in the "Ada and Software Engineering Library Version 2 (ASE2)".

Numerous versions of the ASE library were put together by Richard Conn, the last one in October 2000. They were typically distributed on CDROM at the time, among others at various Ada events such as ACM SIGAda and Ada-Belgium conferences.

The last ASE2 version is still available on the Ada-Belgium site:

ftp://ftp.cs.kuleuven.be/pub/Ada-Belgium/ase/index.htmThe s.c. "asset" that includes the Permutations\_Class package is at: ftp://ftp.cs.kuleuven.be/pub/ Ada-Belgium/ase/support/cardcatx/ csparts.htm

The relevant source code is included in the files CSPARTS.SRC and CSPARTB2.SRC in the csparts.zip archive, retrievable via the above URL.

#### **JSON** Serialisation

From: Maxim Reznik

<reznikmm@gmail.com> Date: Fri, 24 Oct 2014 05:27:53 -0700 Subject: ANN: Serialization Ada objects into/from JSON

Newsgroups: comp.lang.ada

Now Matreshka provides support for serialization Ada objects into/from JSON format using 'Read/'Write attributes.

No magic involved. Conversion routines are provided by user with help of handy framework.

See an example http://forge.ada-ru.org/ matreshka/wiki/League/JSON/Streams [See also "Matreshka", AUJ 35-1, p. 8. —sparre]

# **SparForte**

From: Ken Burtch <koburtch@gmail.com> Date: Fri, 24 Oct 2014 04:18:42 -0700 Subject: ANN: Sparforte 1.5.1 Newsgroups: comp.lang.ada

This version fixes the fatal exception when loading include files ("with separate").

The source code is available on the website at

http://www.sparforte.com

[See also "SparForte", AUJ 35-3, p. 158. —sparre]

# Request: GNAT for OpenVMS/Alpha

From: Eugen Wintersberger

<eugen.wintersberger@gmail.com> Date: Sat, 25 Oct 2014 09:35:32 -0700 Subject: Ada on openvms for Alpha Newsgroups: comp.lang.ada

I have a rather unusual problem: I am looking for an Ada compiler for OpenVMS for Alpha. GNAT no longer supports OpenVMS for Alpha (a decision I Can entirely understand from an economical point of view). However, I Have a couple of Alpha boxes running OpenVMS and I would love to see them running Ada code.

Does anyone of you own a GNAT license for OpenVMS Alpha or knows someone who does and would be willing to give away this license or sell it to me?

Thanks in advance and best regards

# AVR-Ada

From: Rolf Ebert <rolf.ebert.gcc@gmx.de> Date: Sun, 26 Oct 2014 10:17:29 +0100 Subject: open issues for V1.3 Newsgroups: gmane.comp.hardware.

*avr.ada* [Preparations for AVR-Ada 1.3 release. —sparre]

I'd also like to include AvrX in a V1.3 and drop avr-threads, but I don't know when AvrX will be ready for AVR-Ada.

From: Tero Koskinen <tero.koskinen@iki.fi> Date: Fri, 31 Oct 2014 22:11:15 +0200 Subject: Re: open issues for V1.3 Newsgroups: gmane.comp.hardware .avr.ada

[...]

My very unofficial build service seems to be able to build the repository now:

http://build.ada-language.com/job/ AVR-Ada\_Debian\_7/

[See also "AVR-Ada", AUJ 34-2, p. 66. —sparre]

# Ada-related Products

## Status of Ada 2012 Implementations

From: Randy Brukardt <randy@rrsoftware.com> Date: Wed, 14 May 2014 16:37:39 -0500 Subject: Re: Safety of unprotected concurrent operations on constant objects

Newsgroups: comp.lang.ada

> Who else besides AdaCore is doing an Ada 2012 implementation?

Sadly, don't know of any. I've added a tiny amount of Ada 2012 stuff to Janus/Ada, but it will be a long time before much significant gets there.

From: Robert A Duff <bobduff@shell01.TheWorld.com> Date: Wed, 14 May 2014 17:56:33 -0400 Subject: Re: Safety of unprotected concurrent operations on constant objects

Newsgroups: comp.lang.ada

>[...]

I'd bet Atego and ICSC are working on it.

# CodePeer Earns Qualification for Software Verification in Avionics and Railway

From: AdaCore Press Center Date: Thu Oct 23 2014 Subject: AdaCore's CodePeer Static Analysis Tool Earns Oualification for

Analysis 1001 Earns Qualification for Software Verification in Avionics, Railway

URL: http://www.adacore.com/press/ codepeer-earns-qualification/

Automatic code review and validation tool meets rigorous industry software verification standards; provides trusted reliability for Ada developers in safetycritical applications

NEW YORK, PARIS and BRISTOL, October 23, 2014, High Integrity Software Conference, Bristol, UK --AdaCore today announced that its CodePeer advanced static analysis tool for the automated review and validation of Ada source code has been qualified as a software verification tool for developers in both avionics and railway industries.

CodePeer assesses the program before execution to find errors efficiently and early in the development life cycle. Using advanced mathematics, CodePeer analyzes every line of software, considering every possible input and every path through the program. It performs impact and vulnerability analysis when existing code is modified, and, using control-flow, data-flow and other advanced static analysis techniques, it detects problems that would otherwise require labor-intensive debugging.

"In safety-critical domains, developers need very strong assurances that the tool they're using to assess their code is reliable, can be trusted, and will substantially reduce the need for manual code review," says Arnaud Charlet, CodePeer Product Manager and Technical Director at AdaCore. "CodePeer has been through rigorous industry-specific tests for avionics and railway that fully affirm its value and reliability in these and other safety-critical development environments."

#### Avionics Qualification

CodePeer has been qualified as a verification tool for DO-178B, the software safety standard for commercial airborne systems. Certification authorities such as the FAA in the U.S. and EASA in Europe apply DO-178B to provide confidence that the software will meet its requirements.

Vulnerabilities detected by CodePeer analysis for avionics include following:

- Overflow on integer and floating point types

- Range violations on integer and floating point types

- Index violations on array operations

- Division by zero on integer and floating point types

- Uninitialized variables

- Underflow on floating point types

Where no potential error is reported, CodePeer guarantees that the code is exempt from these vulnerabilities

#### Railway Qualification

For railway applications, CodePeer has been used to verify code certified in accordance with CENELEC EN 50128:2011 SIL 4 --the highest safety integrity level.

In this context, CodePeer has been used for the following activities:

- Boundary value analysis: it detects attempts to dereference a pointer that could be null, to read values outside the bounds of an Ada type or subtype, and also detects buffer overflows, numeric overflow or wraparound, and division by zero.

- Control flow analysis: it detects suspicious and potentially incorrect control flows, such as unreachable code, redundant conditionals, loops that either run forever or fail to terminate normally, and subprograms that never return.

- Data flow analysis: it detects suspicious and potentially incorrect data flows, such as variables read before they are written (uninitialized variables), variables written more than once without

being read (redundant assignments), variables that are written but never read, and parameters with an incorrect mode (unread parameter, unassigned parameter).

CodePeer can be used in conjunction with AdaCore's GNAT Pro development environment where it is tightly integrated into AdaCore's GPS (GNAT Programming Studio) and GNATbench IDEs, or as a standalone product. It comes with a number of complementary static analysis tools common to the technology: a coding standard verification tool (GNATcheck), a source code metric generator (GNATmetric), a semantic analyzer and a document generator.

A demo highlighting the new features introduced in the latest version of CodePeer can be viewed at the following url: http://www.adacore.com/codepeer-2-3-demo/

[See also "CodePeer", AUJ 35-1, p. 10. —sparre]

# Ada and Operating Systems

# Fedora: GtkAda

From: Björn Persson

<br/>

For anyone who is interested: GTKada 3.8.2 is now packaged in Fedora. The package is named "GtkAda3".

Version 2.24.2 is still available as "GtkAda". The binary libraries are parallel-installable, so programs using GTKada 3 can coexist with programs using GTKada 2. The -devel packages conflict though, because they use the same filename in several cases, so you can develop for GTKada 2 or for GTKada 3, but not both simultaneously.

# MacOS X: XNAdaLib

From: Pascal Pignard <p.p11@orange.fr> Date: Mon, 08 Sep 2014 18:17:12 +0200 Subject: [ANN] XNAdaLib 2014 binaries for MacOS 10.9 including GTKAda 3.8 and more.

Newsgroups: comp.lang.ada

This is XNAdaLib 2014 built on MacOS X 10.9 Mavericks for Native Quartz including:

- GTK Ada 3.8.2 with GTK+ 3.10.7 complete for Quartz backend,

- Glade 3.16.1,

- GnatColl GPL 2014,

- Florist GPL 2014,

- AdaCurses 20110404 (http://invisibleisland.net/ncurses/ncurses-Ada95.html),

- Gate 3-04-b (http://sourceforge.net/projects/lorenz),

- AICWL 3.9 (http://www.dmitrykazakov.de/ada/aicwl.htm with Components 4.1 and gtksourceview 3.10.1),

to be installed (mandatory) at /usr/local:

\$ cd /usr/local

\$ sudo tar xzf xnadalib-gpl-2014-quartzx86\_64-apple-darwin13.3.0-bin.tgz

Update your PATH to include gtkadaconfig, glade, gate3.sh and other executables in it:

\$ PATH=/usr/local/xnadalib-2014/bin:\$PATH

Update your GPR\_PROJECT\_PATH to include gtkada.gpr, adacurses.gpr, florist.gpr, gnatcoll.gpr, gtkada\_aicwl.gpr and other projects in it:

\$ export

GPR\_PROJECT\_PATH=/usr/local/xnadal ib-2014/lib/gnat:\$GPR\_PROJECT\_PATH

Set XDG\_DATA\_DIRS for GNOME apps:

\$ export

XDG\_DATA\_DIRS=/usr/local/xnadalib-2014/share

Glade and GPS applications in apps directory must stay in this directory unless you modify the script inside apps.

Then see READMEs, documentation and examples in share directory and enjoy.

XNAdaLib binaries have been post on Source Forge:

http://sourceforge.net/projects/gnuada/ files/GNAT\_GPL%20Mac%20OS%20X/ 2014-mavericks/

The instructions for building XNAdaLib are here:

(French language)

http://blady.pagesperso-orange.fr/ telechargements/gtkada/ Install-GTKAda-Quartz.pdf

Feel free to send comments.

# **Debian: SQLite Interface**

From: Ludovic Brenta <ludovic@ludovic-brenta.org> Date: Tue, 07 Oct 2014 01:35:07 +0200 Subject: Re: Which database document for wheezy? Newsgroups: gmane.linux.debian.

packages.ada

>[...]

Yes, there is GNADE, the ancestor of gnatcoll for SQLite connectivity.

aptitude install libgnadesqlite3-2-dev

I'm afraid there is no textbook on how to use GNADE, you'll have to read the Ada specs.

# **Debian/Windows: GNAT**

From: Brian Drummond <brian@shapes.demon.co.uk> Date: Thu, 09 Oct 2014 18:04:30 GMT Subject: Re: Newcomers to comp.lang.ada: welcome and how did you end up here ? Newsgroups: comp.lang.ada

>[...]

On the subject of mingw, I don't know how many people know of this option, but I was a little surprised to see mingw packages, including FSF GNAT, available on Debian.

Turns out it's a cross-compiler. So having developed an Ada app on Debian, I can invoke the mingw crosscompiler and build a Windows executable. So far these have worked flawlessly, including interfacing between Ada and a C library talking to a USB device.

The executable is larger - typically 800k instead of 150k for native Linux executables. Haven't investigated why but I assume it's statically linked to eliminate dependencies, and I haven't had to install anything other than the exe on Windows machines so far.

One more option and probably the simplest way to use FSF GCC targetting Windows machines...

# **Raspbian: Gnoga**

From: Tony G. <tonythegair@gmail.com> Date: Wed, 22 Oct 2014 09:24:07 -0700 Subject: Gnoga, raspbian jessie and the PI Newsgroups: comp.lang.ada

I don't know if anyone else has tried, but I have just successfully built GNOGA and the tutorials successfully on a Raspberry Pi with the standard issued Debian packages AWS 3.2 and gnat (don't know the version).

Raspbian version is Jessie.

# Mac OS X: GCC

From: Simon Wright <simon@pushface.org> Date: Sat, 25 Oct 2014 20:30:07 +0100 Subject: ANN: GCC 4.9.1 for Mac OS X Mavericks and Yosemite

Newsgroups: gmane.comp.lang.ada.macosx

It occurs to me that I should probably have been making these announcements here as well as in c.l.a. Apologies to those of you who're already aware.

GCC 4.9.1 is available at https://source forge.net/projects/gnuada/files/ GNAT\_GCC%20Mac%20OS%20X/4.9.1

It was built on Mavericks and is compatible with Yosemite.

The README:

This is GCC 4.9.1 built for Mac OS X Mavericks (10.9.5, Darwin 13.5.0), with Xcode 6.0.1. gcc-4.9.1-x86\_64-apple-darwin13.tar.bz2

Compilers included: Ada, C, C++, Objective C, Objective C++, Fortran. Tools included:

Full GPL: ASIS, AUnit, GDB, GNATColl, and GPRbuild from GNAT GPL 2014.

GPL with Runtime Library Exception[1]:

- XMLAda from the public SVN repository[2] at revision 233185 (XMLAda-SVN for short).

- AWS from the public git repository[3] at commit e0d260e2d5dbbd935779493079 35848de2390818 (AWS-git for short).

Target: x86 64-apple-darwin13

Configured with: ../gcc-4.9.1/configure \

--prefix=/opt/gcc-4.9.1 \

--disable-multilib  $\ --disable-nls \$

--enable-languages=

c,c++,ada,fortran,objc,obj-c++  $\$

--host=x86\_64-apple-darwin13  $\$

--target=x86\_64-apple-darwin13 \

--build=x86\_64-apple-darwin13  $\$

--with-host-libstdcxx=-lstdc++

Thread model: posix

gcc version 4.9.1 (GCC)

MD5 (gcc-4.9.1-x86\_ 64-apple-darwin13.tar.bz2) =

f04d5d773174a4a58cdd2dd4871785a4

[1] http://www.gnu.org/licenses/gccexception-faq.html

[2] http://svn.eu.adacore.com/anonsvn/ Dev/trunk/xmlada

[3] http://forge.open-do.org/ anonscm/git/aws/aws.git

# **Debian: Adabrowse**

From: Ludovic Brenta <ludovic@ludovicbrenta.org>

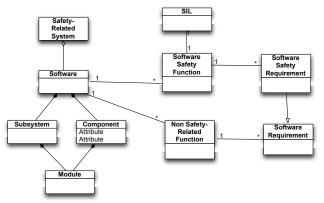

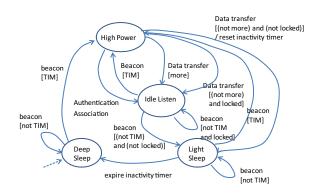

Date: Mon, 27 Oct 2014 00:32:30 +0100 Subject: Re: Upload of adabrowse Newsgroups: gmane.linux.debian. packages.ada