# ADA USER JOURNAL

# Volume 36 Number 4 December 2015

# Contents

|                                                                                                                                                                                                            | Page              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                                                                                      | 198               |

| Editorial                                                                                                                                                                                                  | 199               |

| Quarterly News Digest                                                                                                                                                                                      | 200               |

| Conference Calendar                                                                                                                                                                                        | 216               |

| Forthcoming Events                                                                                                                                                                                         | 221               |

| Bicentennial Ada Lovelace Articles                                                                                                                                                                         |                   |

| G. A. Rino Nesin<br>"The Ada Lovelace Symposium in Oxford"                                                                                                                                                 | 226               |

| J. G. P. Barnes<br>"From Byron to the Ada Language"                                                                                                                                                        | 231               |

| Article from the Industrial Track of Ada-Europe 2015                                                                                                                                                       |                   |

| B. Gallina and L. Provenzano<br>"Deriving Reusable Process-based Arguments from Process Models in the Contex.<br>Railway Safety Standards"                                                                 | <i>t of</i> 237   |

| Proceedings of the "Workshop on Challenges and New Approaches for Dependable a<br>Cyber-Physical System Engineering" of Ada-Europe 2015<br>D. Cancila and C. Robinson<br><i>"Editorial"</i>                | nd 243<br>244     |

| I. Quadri, A. Bagnato, E. Brosse and A. Sadovykh<br>"Modeling Methodologies for Cyber-Physical Systems: Research Field Study on Inherent<br>and Future Challenges"<br>A. Pawlak, J. Jezewski and K. Horoba | 246               |

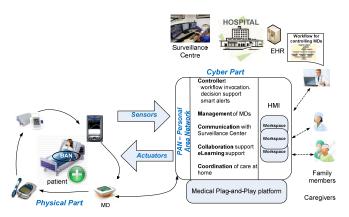

| "Dependable Medical Cyber-Physical System for Home Telecare of High-Risk Pregnancy"                                                                                                                        | 254               |

| P. Burgio, C. Alvarez, E. Ayguadé, A. Filgueras, D. Jiménez-González, X. Martorell,<br>N. Navarro and R. Giorgi<br>"Simulating Next-Generation Cyber-Physical Computing Platforms"                         | 259               |

| S.Mazzini<br>"The CONCERTO Project: an Open Source Methodology for Designing, Deploying,<br>and Operating Reliable and Safe CPS Systems"                                                                   | 264               |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                                                                                  | 268               |

| Ada-Europe Sponsors                                                                                                                                                                                        | Inside Back Cover |

# Editorial Policy for Ada User Journal

#### Publication

*Ada User Journal* — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

#### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

#### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

#### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

#### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

#### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

In this last issue of Volume 36, we conclude the celebration of the 200th anniversary of Ada Lovelace with two special contributions. In the first, Gabriela Rino Nesin, from the University of Oxford, UK, provides us a vivid and motivating description of the Ada Lovelace Symposium, one of the main bicentennial celebrating events, which took place 9-10 December 2015. Following that, John Barnes provides us with an overview of his speech at the symposium, which goes from Byron to the Ada language, concluding the special featured section of the Journal.

Organising this bicentennial special section featured in Volume 36 of the Ada User Journal has been indeed a very rewarding experience. I hope that the reader has both appreciated and learnt, as we did.

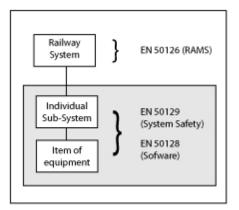

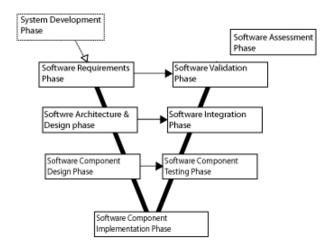

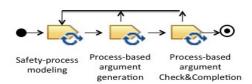

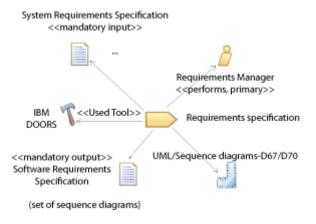

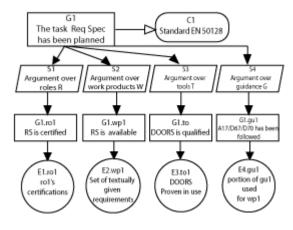

The issue then continues with a technical paper from the Ada-Europe 2016 industrial track, by Barbara Gallina, of Mälardalen University and Luciana Provenzano, of Bombardier Transportation, Sweden, on the application of a model-driven safety certification method in the domain of railway.

The issue also publishes the Proceedings of the "2nd Workshop on Challenges and New Approaches for Dependable and Cyber-Physical System Engineering", co-located with Ada-Europe 2015. This workshop brought together industry and research participants, for a full-day discussion on dependability and critical issues of Cyber-Physical Systems (CPS). The workshop editorial by Daniela Cancila, from CEA LIST, and Charles Robinson, from Thales, R&T, is followed by a set of technical papers, part of the workshop's program. In the first paper, authors from Softeam, France, present a study on the challenges put forward to the design of CPS, and how model-based design helps tackling those. Then, authors from the Silesian University of Technology and the Institute of Medical Technology and Equipment, Poland, describe an actual dependable medical CPS for telecare, as well as its challenges and requirements. In the third paper of the proceedings, authors from the University of Modena and Reggio Emilia, Italy, Barcelona Supercomputing Center, Spain, and University of Siena, Italy, present the view of the AXIOM project, on virtual platforms modelling for next-generation cyber-physical systems. Finally, in the last paper, Silvia Mazzini, from Intecs, Italy, describes the CONCERTO open source methodology for designing and deploying reliable and safe CPS.

As usual the issue also provides the News Digest, and Calendar and Forthcoming Events sections, prepared by the respective Editors, Jacob Sparre Andersen and Dirk Craeynest. The forthcoming events include information on the 7th Ada Developer Room at the Free and Open source Software Developers' European Meeting (FOSDEM 2016), the 2016 International Real-Time Ada Workshop (IRTAW), which will take place in Benicássim, near Valencia, Spain, April 11-13 2016, and last, but definitely not least, the Ada-Europe 2016 conference, which will take place in Pisa, Italy, in the week of 13-17 June, 2016. These are important events for the community, and that require active contribution from each one of us!

Luís Miguel Pinho Porto December 2015 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

### Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

# Contents

| Ada-related Events         | 200 |

|----------------------------|-----|

| Ada-related Resources      | 201 |

| Ada-related Tools          | 202 |

| Ada-related Products       | 203 |

| Ada and Operating Systems  | 204 |

| References to Publications | 206 |

| Ada Inside                 | 207 |

| Ada in Context             | 208 |

# Ada-related Events

[To give an idea about the many Adarelated events organised by local groups, some information is included here. If you are organising such an event feel free to inform us as soon as possible. If you attended one please consider writing a small report for the Ada User Journal. —sparre]

#### Ada Augusta Lovelace Bicentennial

From: Tom Moran <tmoran@acm.org> Date: Tue, 15 Sep 2015 17:55:08 +0000 Subject: Ada Lovelace Bicentennial Newsgroups: comp.lang.ada

I see the Computer History Museum and ACM will have an exhibit in early December to celebrate the bicentennial of Ada Lovelace.

#### From: Simon Wright

<simon@pushface.org> Date: Tue, 15 Sep 2015 20:23:27 +0100 Subject: Re: Ada Lovelace Bicentennial Newsgroups: comp.lang.ada

>[...]

There's also a UK programme [1]; I've booked myself in to the Symposium [2].

- [1] http://blogs.bodleian.ox.ac.uk/ adalovelace/events/

- [2] http://blogs.bodleian.ox.ac.uk/ adalovelace/symposium/

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Tue, 24 Nov 2015 18:30:28 +0100 Subject: Ada Augusta Lovelaces 200-års fødselsdag

To: Ada in Denmark members

[Translated summary: —sparre]

December 10 it is the 200 years birthday of Ada Augusta Lovelace. We're going to meet to celebrate the first programmer in the world (and the best programming language in the world :-).

### Ada-Europe 2016 in Pisa

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Sun, 18 Oct 2015 06:32:16 +0000 Subject: CfP 21st Conf. Reliable Software Technologies, Ada-Europe 2016 Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

[CfP is included in the Forthcoming Events Section —sparre]

### **FOSDEM 2016**

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Wed, 4 Nov 2015 07:10:24 -0000 Subject: CfP - Ada Developer Room at FOSDEM 2016, Brussels, Belgium Newsgroups: comp.lang.ada, fr.comp.lang.ada

#### Call for Presentations

7th Ada Developer Room at FOSDEM 2016

Saturday 30 January 2016, Brussels, Belgium

http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/16/ 160130-fosdem.html

Organized in cooperation with Ada-Europe

Ada-Belgium [1] is pleased to announce that there will be a one-day Ada Developer Room on Saturday 30 January 2016 at FOSDEM 2016 in Brussels, Belgium. This Ada DevRoom is once more organized in cooperation with Ada-Europe [2].

#### General Information

FOSDEM [3], the Free and Open source Software Developers' European Meeting, is a free and non-commercial two-day weekend event organized early each year in Brussels, Belgium. It is highly developer-oriented and brings together 5000+ participants from all over the world. No registration is necessary.

The goal is to provide open source developers and communities a place to meet with other developers and projects, to be informed about the latest developments in the open source world, to attend interesting talks and presentations on various topics by open source project leaders and committers, and to promote the development and the benefits of open source solutions.

#### Ada Developer Room

At previous FOSDEM events, Ada-Belgium has organized very well attended Ada Developer Rooms, offering a full day program in 2006 [4], a two-day program in 2009 [5], and full day programs in 2012 [6], 2013 [7], 2014 [8], and 2015 [9]. An important goal is to present exciting Ada technology and projects also to people outside the traditional Ada community.

Our proposal for another dedicated Ada DevRoom was accepted, and now work continues to prepare the detailed program. We most probably will have a total of 8 schedulable hours between 11:00 and 19:00 in a room which accommodates 60 participants. More information will be posted on the dedicated web-page on the Ada-Belgium site [10], and final announcements will of course also be sent to various forums, lists and newsgroups.

#### Call for Presentations

Ada-Belgium calls on you to:

- inform us at ada-belgiumboard@cs.kuleuven.be about specific presentations you would like to hear in this Ada DevRoom;

- for bonus points, subscribe to the Ada-FOSDEM mailing list [11] to discuss and help organize the details;

- for more bonus points, be a speaker: the Ada-FOSDEM mailing list is the place to be!

Do you have a talk you want to give?

Do you have a project you would like to present?

Would you like to get more people involved with your project?

We're inviting proposals that are related to Ada software development, and include a technical oriented discussion. You're not limited to slide presentations, of course. Be creative. Propose something fun to share with people so they might feel some of your enthusiasm for Ada!

Speaking slots are 20 or 45 minutes, plus 5 minutes for Q&A. Depending on interest, we might also have a session with lightning presentations (e.g. 5 minutes each).

We'd like to put together a draft schedule early December. So, please act ASAP, and definitely by November 29, 2015 at the latest. We look forward to lots of feedback and proposals!

Dirk Craeynest, FOSDEM Team of Ada-Belgium

Dirk.Craeynest@cs.kuleuven.be (for Ada-Belgium/-Europe/SIGAda/WG9 mail)

- [1] http://www.cs.kuleuven.be/~dirk/ ada-belgium

- [2] http://www.ada-europe.org

- [3] https://fosdem.org

- [4] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/06/ 060226-fosdem.html

- [5] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/09/ 090207-fosdem.html

- [6] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/12/ 120204-fosdem.html

- [7] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/13/ 130203-fosdem.html

- [8] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/14/ 140201-fosdem.html

- [9] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/15/ 150131-fosdem.html

- [10] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/16/ 160130-fosdem.html

- [11] http://listserv.cc.kuleuven.be/ archives/adafosdem.html

# Ada-Belgium Celebration of 200th birthday Ada Lovelace

From: Dirk Craeynest <Dirk.Craeynest@cs.kuleuven.be> Date: Sat, 5 Dec 2015 21:33:53 +0100 Subject: Ada-Belgium Celebrates 200th Birthday Ada Lovelace 10 Dec 2015

To: ada-belgium-info@cs.kuleuven.be

The Computer Science Department of the KU Leuven and the Ada-Belgium organization are pleased to announce a celebration of the

\_\_\_\_\_

200th Birthday of Ada Lovelace

on Thursday, December 10, 2015, 20:00 at the KU Leuven, Department of Computer Science, Auditorium

Celestijnenlaan 200A, B-3001 Leuven (Heverlee), Belgium

www.cs.kuleuven.be/~dirk/ada-belgium/ events/15/151210-ab-ada200.html

On the occasion of Ada Lovelace's 200th birthday, the Computer Science Department of the KU Leuven together with Ada-Belgium organize a small celebration, featuring a screening of the "To Dream Tomorrow" documentary on Ada Lovelace.

#### Synopsis:

"To Dream Tomorrow" is the story of Ada Byron Lovelace and her contributions to computing, over a hundred years before the time usually thought to be the start of the Computer Age.

Daughter of a mathematically gifted, social activist mother and the "mad, bad and dangerous to know" poet Lord Byron, Ada was 17 when she began studying a prototype mechanical calculator designed by mathematician Charles Babbage.

By the time she was 27, she had moved even beyond her famous contemporaries to describe universal computing much as we understand it today.

(Language: English; Duration: 52 min.)

This event will be held at the Computer Science Department of the KU Leuven in Leuven (Heverlee), on Thursday, December 10, 2015.

Starting time is 20:00, and the program consists of a short introduction, a screening of the documentary, and an informal drink to socialize and network.

#### Context

10 December 2015 is the 200th anniversary of the birth of Ada Lovelace.

She is seen by many as the first programmer due to her work on Charles Babbage's Analytical Engine, a mechanical general-purpose computer he designed but didn't manage to build.

The Ada programming language is named after Ada Lovelace. It is an evolving state-of-the-art programming language especially suitable for large, long-lived applications where safety, security, reliability, and efficiency are critical.

Current application areas include air traffic control and management, airplane engines and systems, railway signalling and transportation, space missions, banking and financial systems, industrial command and control systems, etc. Due to its approach of detecting errors as soon as possible its use offers valuable advantages, even for less demanding applications.

Ada-Belgium is a non-profit organization that aims to be a forum for persons and organizations interested in the Ada programming language, in its applications and in Ada related technologies such as software engineering methods, environments and tools.

#### Participation

Everyone is welcome, and participation is free, but for practical reasons we'd appreciate if you could inform us of your intent to be there. Please provide your name, email address and affiliation, by email to <ada-belgium-board@cs.kuleuven.be>.

For directions to the Computer Science Department of the KU Leuven, see <http://wms.cs.kuleuven.be/cs/english/ about/directions>.

# **Ada-related Resources**

# Ada on Social Media

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Wed Nov 18 2015

Subject: Ada on Social Media

- Ada groups on various social media:

- LinkedIn[1]: 2\_329 members

- Reddit[2]: 850 readers

- Google+[3]: 546 members

- StackOverflow[4]: 327 followers

- Twitter[5]: 5 tweeters

[1] https://www.linkedin.com/ groups?gid=114211

[2] http://www.reddit.com/r/ada/

[3] https://plus.google.com/communities/ 102688015980369378804

[4] http://stackoverflow.com/questions/ tagged/ada

[5] https://twitter.com/search?f=realtime &q=%23AdaProgramming

[See also "Ada on Social Media", AUJ 36-3, p. 121. —sparre]

# **Repositories of Open Source Software**

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Wed Nov 18 2015 Subject: Repositories of Open Source software

GitHub: 1\_064 repositories [1]

280 developers [1]

Rosetta Code: 624 examples [2]

30 developers [3]

Sourceforge: 244 repositories [4]

BlackDuck OpenHUB: 213 projects [5]

Bitbucket: 188 repositories [6]

OpenDO Forge: 23 projects [7]

466 developers [7]

Codelabs: 20+ repositories [8]

AdaForge: 8 repositories [9]

Assembla: 6 projects [10]

https://github.com/search?

q=language%3AAda&type=Repositories

http://rosettacode.org/wiki/ Category:Ada [3] http://rosettacode.org/wiki/ Category:Ada\_User

[4] http://sourceforge.net/directory/ language%3Aada/

[5] https://www.openhub.net/ tags?names=ada

[6] https://bitbucket.org/repo/ all?name=ada

[7] https://forge.open-do.org/

[8] http://git.codelabs.ch/

[9] http://forge.ada-ru.org/adaforge

[10] https://www.assembla.com/tag/ada [See also "Repositories of Open Source Software", AUJ 36-3, p. 121. —sparre]

# Ada-related Tools

# ZanyBlue

From: Michael Rohan <michael@zanyblue.com> Date: Sun, 13 Sep 2015 14:30:32 -0700 Subject: ANN: ZanyBlue v1.2.1 Beta Available

Newsgroups: comp.lang.ada

A new release of ZanyBlue is now available: 1.2.1 Beta. This is an Ada library currently targeting localization support for Ada (along the lines of Java properties) with supporting message formatting and built-in localization for about 20 locales. The properties files are compiled into Ada sources built with your application and use to access application messages at run-time. The run-time locale is used to select localized messages, if they are available.

The changes for this release are

- Updates for building with GNAT 2015 (major driver for this release).

- Updated CLDR to release 26 from release 24.

Please see the project page on Source Forge for download links, documentation, etc,

http://zanyblue.sourceforge.net

This project is licensed under a simple BSD style license.

[See also "ZanyBlue", AUJ 35-2, p. 75. —sparre]

# GtkAda

From: Nicolas Setton

<setton@adacore.com> Date: Tue, 6 Oct 2015 13:31:25 -0400 Subject: the GtkAda repository is now on github

Newsgroups: gmane.comp.gnome.gtk+.ada To: gtkada@lists.adacore.com

GtkAda is now on github, at:

https://github.com/AdaCore/gtkada

We hope this will make everyone's workflows easier and collaboration simpler!

If you have any question, don't hesitate to ask on this list.

In addition to this list, I noticed that people are answering GtkAda questions on stackoverflow.com, and also on comp.lang.ada - many thanks to them!

# RAPID

From: Oliver Kellogg

<okellogg@users.sourceforge.net>

Date: Sat, 10 Oct 2015 07:07:40 -0700

Subject: Re: RAPID 3.3 is released

Newsgroups: comp.lang.ada

Sadly, I have not been finding time for further work on RAPID.

On the upside, I have made a perl script that translates the RAPID GUI file format to Gtk's Glade-3 Builder UI format, see

http://svn.savannah.nongnu.org/viewvc/ \*checkout\*/trunk/gtk\_bin/rapid2glade.pl? root=rapid

Recently, I have extended the script to generate Ada support code which eases the transition from RAPID to GtkAda.Builder.

[See also "RAPID 3.3", AUJ 32-2, p. 85. —sparre]

# **Simple Components**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Mon, 19 Oct 2015 18:49:45 +0200 Subject: ANN: Simple components 4.10 released

Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, multiple connections server/client designing tools.

http://www.dmitry-kazakov.de/ada/ components.htm

Changes to the previous version:

- ELV/e-Q3 MAX! client wall thermostat support added;

- ELV/e-Q3 MAX! device data available through Get\_Device\_Data;

- ELV/e-Q3 MAX! interface calls querying topology, device parameters and data are task-safe;

- Socket\_Error 11004 workaround added.

[See also "Simple Components", AUJ 36-3, p. 122. —sparre]

# **GtkAda Contributions**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Tue, 20 Oct 2015 18:23:34 +0200 Subject: ANN: GtkAda contributions v3.14 released

Newsgroups: comp.lang.ada

The library extends GtkAda 3.8.3/4. It deals with the following issues:

- Tasking support;

- Custom models for tree view widget;

- Custom cell renderers for tree view widget;

- Multi-columned derived model;

- Extension derived model (to add columns to an existing model);

- Abstract caching model for directorylike data;

- Tree view and list view widgets for navigational browsing of abstract caching models;

- File system navigation widgets with wildcard filtering;

- Resource styles;

- Capturing resources of a widget;

- Embeddable images;

- Some missing subprograms and bug fixes;

- Measurement unit selection widget and dialogs;

- Improved hue-luminance-saturation color model;

- Simplified image buttons and buttons customizable by style properties;

- Controlled Ada types for GTK+ strong and weak references;

- Simplified means to create lists of strings;

- Spawning processes synchronously and asynchronously with pipes;

- Capturing asynchronous process standard I/O by Ada tasks and by text buffers;

- Source view widget support.

http://www.dmitry-kazakov.de/ada/ gtkada\_contributions.htm

- Changes to previous version:

- Minor bug fixes;

- GTK 3.10 compatibility issues.

[See also "GtkAda Contributions", AUJ 36-3, p. 125. —sparre]

# Industrial Control Widget Library

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Wed, 21 Oct 2015 18:54:22 +0200 Subject: ANN: Ada industrial control widget library v3.12 released

#### Newsgroups: comp.lang.ada

The library is provided for design highquality industrial control widgets for Ada applications. The software is based on GtkAda, Ada bindings to Gtk+ and Cairo. The key features of the library:

- Widgets composed of transparent layers drawn by cairo; - Fully scalable graphics;

- Support of time controlled refresh policy for real-time and heavy-duty applications;

- Caching graphical operations;

- Stream I/O support for serialization and deserialization;

- Ready-to-use gauge, meter, oscilloscope widgets;

- Editor widget for WYSIWYG design of complex dashboards.

- http://www.dmitry-kazakov.de/ada/ aicwl.htm

The new version is adapted to GNAT 5 now available for Debian.

[See also "Industrial Control Widget Library", AUJ 35-3, p. 157. —sparre]

# **PragmAda Reusable** Components

From: PragmAda Software Engineering <pragmada@

pragmada.x10hosting.com> Date: Tue, 20 Oct 2015 15:09:38 -0700 Subject: New Release of PragmAda

Reusable Components Beta Version Newsgroups: comp.lang.ada

A new release of the beta version of the PragmARCs for compilers that support ISO/IEC 8652:2007 is now available at

https://pragmada.x10hosting.com/ pragmarc.htm

The main change is an improved interface for the REM neural network component, and the ability to use multiple tasks to run a network.

[See also "PragmAda Reusable Components", AUJ 35-3, p. 154. —sparre]

# AdaControl

From: Jean-Pierre Rosen <rosen@adalog.fr>

Date: Fri, 6 Nov 2015 17:39:09 +0100 Subject: [Ann] AdaControl 1.17r3 released Newsgroups: comp.lang.ada

Adalog is happy to announce the release of version 1.17r3 of AdaControl.

This version brings its usual load of improvements and new (sub)rules, but the most important improvements are in better support of Ada 2005/2012 constructs... especially in the handling of (#!?GRR...) anonymous access types that were overlooked in previous versions.

As usual, it can be downloaded from the AdaControl page on

#### http://www.adalog.fr

Remember: if you are a professional user, a great support contract is available from Adalog. Don't hesitate to get in touch.

[See also "AdaControl", AUJ 36-1, p. 13. -sparre]

### **GNAT: Ada.Strings.\*** Omissions

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Thu, 12 Nov 2015 15:33:40 -0700 Subject: Re: Unicode string comparison functions Newsgroups: comp.lang.ada

- >...Wide Wide Equal Case Insensitive --- Testing it out, the compiler's giving me an error saying

- ""Ada.Strings.Wide\_Wide\_Equal\_Case Insensitive" is not a predefined library unit", which is good in that it saves me from feeling \*\*REALLY\*\* stupid.

ARM A.4.8 clearly indicates that there should be such a library function, similar to Ada.Strings.Equal\_Case\_Insensitive from A.4.10 for String.

They were added by Ada 2012, so if you're using a compiler for an earlier version they probably won't exist. If you are using an Ada 2012 compiler, you should probably complain.

From: Randy Brukardt <randy@rrsoftware.com> Date: Thu, 12 Nov 2015 18:10:32 -0600 Subject: Re: Unicode string comparison functions

Newsgroups: comp.lang.ada

>[...]

Right, assuming you spelled it right (with the Wide Wide madness, spelling it wrong isn't that uncommon!).

From: Simon Wright <simon@pushface.org> Date: Fri, 13 Nov 2015 08:22:07 +0000 Subject: Re: Unicode string comparison functions Newsgroups: comp.lang.ada > [...]

GNAT GPL 2015 provides Equal Case Insensitive only in plain Strings, Bounded, Fixed, Unbounded.

# Limited Bounded Strings

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Thu, 12 Nov 2015 18:01:21 -0700 Subject: Re: Bounded String question Newsgroups: comp.lang.ada

If anyone's interested, there's now a bounded-string pkg in the PragmAda Reusable Components for ISO/IEC

8652:2007, based on Duff's suggestion [see "Discriminants with Default Values -Limited Types" later in this issue. sparre]. It's pretty much untested, but feel free to play with it.

https://pragmada.x10hosting.com/ pragmarc.htm

[See also "PragmAda Reusable Components" earlier in this section. --sparre]

# **Ada-related Products**

### **GNAT GPL for Raspberry** Pi 2

From: AdaCore Press Center Date: Tue Sep 1 2015

- Subject: AdaCore Introduces GNAT GPL 2015 for the Raspberry Pi 2

- URL: http://www.adacore.com/press/ adacore-introduces-gnat-gpl-2015-forthe-raspberry-pi-2/

Latest version of AdaCore crossdevelopment environment targets students and other developers of nonproprietary software

NEW YORK and PARIS, Sep 1, 2015 -AdaCore, the leading provider of commercial software solutions for the Ada programming language, today released a freely downloadable version of its GNAT GPL Ada cross-development environment for the Raspberry Pi 2 micro-PC running Embedded Linux. With this new cross-development environment, professors, students, hobbyists and others can take advantage of Ada 2012's reliability, safety and security benefits for their Raspberry Pi 2 applications.

GNAT GPL provides a complete Ada 2012 development environment, including a comprehensive tool-chain as well as AdaCore's flagship GNAT Programming Studio (GPS) Integrated Development Environment (IDE). GNAT GPL implements the Ada 2012 language standard by default, which includes these important language features:

- Contract-based programming (preconditions, post-conditions, and type invariants) including support for the Liskov Substitution Principle in Object-Oriented Programming

- More general expressions (conditional expressions, quantified expressions, expression functions)

- Enhanced multiprocessor support (multiprocessor affinity and barriers)

- Enhanced integration of concurrency and OOP

- Additional language-defined libraries (vector/matrix libraries)

"With more than 5 million units sold to date, Raspberry Pi is one of the world's most popular single-board computers for young computer innovators and

#### Ada and Operating Systems

hobbyists," said Jamie Ayre, Marketing Director of AdaCore. "By providing Raspberry Pi 2 users access to the very robust, high-integrity development environment of Ada, we're opening the door to some really creative solutions and the next generation of Ada programmers."

With the release of GNAT GPL for Bare Board ARM in 2014, an implementation on the Raspberry Pi 2 running Linux on ARM was a natural follow-up. It reflects AdaCore's ongoing commitment to the Ada community to provide freely available Ada implementations for developers of nonproprietary software. Fully featured releases of this GNAT technology are also available for GNU Linux, Mac OS X, Bare Board ARM, and Windows.

#### About Raspberry Pi 2

The Raspberry Pi 2 Model B is the second generation Raspberry Pi, released in February 2015. The 900MHz quad-core ARM Cortex-A7 CPU increases the performance almost 6 times, and the 1GB LPDDR2 SDRAM accommodates larger and faster systems.

The Raspberry Pi 2 Model B retains the various interfaces of its predecessor, such as 4 USB ports, 40 GPIO pins, a full HDMI port, and an Ethernet port. With its low cost / high performance advantages, the Raspberry Pi 2 is an attractive choice in many kinds of systems including Internet of Things (IoT) applications.

[...]

# **Rapita Verification Suite**

From: Rapita Systems

Date: Wed Oct 21 2015 Subject: Rapita Systems launches the latest version of RVS at the MCM ITP

Conference, Brighton 2015 URL: https://www.rapitasystems.com/ news/rapita-systems-launches-latestversion-rvs-mcm-itp-conferencebrighton-2015

The latest version of RVS, version 3.4, brings several new features to the table as part of the ongoing tool suite development. Justifications workflow, incremental coverage and livemaps are all part of the latest release bringing a variety of advantages and benefits to customers of Rapita Systems.

Dr Andrew Coombes, Head of Marketing and Product Development at Rapita Systems, describes RVS 3.4 as 'an exciting development in the RVS product line. We've listened to our customers and these are several of the features they have been asking for. We are very confident that the latest features will benefit our current customers as well as our future customers as we continue to strive for product excellence and build strong relationships with the people who use our tools. ' RVS 3.4 will be launched on October 22, 2015 and more details of the latest features can be found on Rapita Systems website [1].

[1] https://www.rapitasystems.com/rvs34

[See also "Rapita Verification Suite", AUJ 36-2, p. 66. —sparre]

#### InterCOM DDS

From: Egil Harald Høvik <egil.harald.hoevik@kongsberg.com> IRC-network: Freenode IRC-channel: #Ada Date: Thu Nov 19 2015

- < egilhh\_> hmmm... I'm doing C right now...

- < egilhh\_> at least I'm generating Ada :)

- < egilhh\_> sparre: I would like to do that, but I'm expanding an existing codebase...

- < Visaoni> egilhh: You have C generating Ada?

- < egilhh\_> Visaoni: yup

- < Visaoni> Interesting. Can you say what for, generally?

- < egilhh\_> Visaoni: Ada support for http://www.kongsberggallium.com/pro ducts/intercom-dds

- < sparre> egilhh: Doesn't sound like a bad task, even if you have to write some C to do it.

- < Visaoni> egilhh: Nice. Looks cool

< egilhh\_> it's pretty interesting

[See http://www.kongsberggallium.com/ docs/intercom\_dds\_datasheet.pdf for information about the currently available version. —sparre]

# Ada and Operating Systems

### Mac OS X: XNAdaLib

From: Pascal Pignard <p.p11@orange.fr> Date: Thu, 03 Sep 2015 21:12:06 +0200 Subject: [ANN] XNAdaLib 2015 binaries for MacOS 10.9 including GTKAda GPL 2015 and more.

Newsgroups: comp.lang.ada

This is XNAdaLib 2015 built on MacOS 10.9 Mavericks for Native Quartz including:

- GTK Ada GPL 2015 with GTK+ 3.16.0 complete,

- Glade 3.18.3,

- GnatColl GPL 2015,

- Florist GPL 2015,

- AdaCurses 20110404,

- Gate 3-04-b,

- AICWL 3.11 (with Components 4.8 and gtksourceview 3.14.3),

- GNOGA 1.1a,

to be installed for instance at /usr/local:

\$ cd /usr/local \$ sudo tar xzf xnadalib-gpl-2015-quartzx86\_64-apple-darwin13.4.0-bin.tgz

Update your PATH to include gtkadaconfig, glade, gate3.sh and other executables in it:

\$ PATH=/usr/local/xadalib-2015/bin:\$PATH

Update your GPR\_PROJECT\_PATH to include gtkada.gpr, adacurses.gpr, florist.gpr, gnatcoll.gpr, gnoga.gpr and other projects in it:

\$ export GPR\_PROJECT\_PATH=/usr/local/ xnadalib-2015/lib/gnat:/usr/local/ xnadalib-2015/share/ gpr:\$GPR\_PROJECT\_PATH

Set XDG\_DATA\_DIRS for GNOME apps:

\$ export XDG\_DATA\_DIRS=/usr/local/ xnadalib-2015/share

Glade and GPS applications in apps directory must stay in this directory unless you modify the script inside apps.

Then see documentation and examples in share directory and enjoy.

Here is the instructions I used to build XNAdaLib on MacOS:

(French language)

http://blady.pagesperso-orange.fr/ telechargements/gtkada/ Install-GTKAda-Quartz wf.pdf

Here is the modifications I made:

http://blady.pagesperso-orange.fr/ telechargements/gtkada/ xadalib-2015-diff.tgz

XAdaLib binaries have been post on Source Forge:

http://sourceforge.net/projects/gnuada/ files/GNAT\_GPL%20Mac%20OS%20X/ 2015-mavericks/

[See also "MacOS X: XNAdaLib", AUJ 35-4, p. 221. —sparre]

### Mac OS X: GtkAda

From: Ahlan Marriott

<ahlan@marriott.org> Date: Sat, 5 Sep 2015 12:50:07 -0700 Subject: Re: Gtkada on Mac using Quartz Newsgroups: comp.lang.ada

In case anyone is interested, I managed to get my non-trivial GUI test program, written using GNAT-GPL-2015 and GPL-2015 GtkAda to work without any source changes on all three of my selected targets, namely Windows (XP), Linux (Ubuntu) and OS X (Yosemite).

Yosemite was the biggest challenge because AdaCore for some reason didn't provide a GtkAda installation as they did for Windows and Linux. Which meant that I had to get and compile Gtk myself. Fortunately the linux installation worked after rewriting my GUI package to use the main thread, the program ran on all platforms. Which, I think, is rather cool!

### Windows XP: Working GtkAda Versions

From: Ahlan Marriott <ahlan@marriott.org> Date: Fri, 18 Sep 2015 08:44:09 -0700 Subject: Gtk 3.8.4 (and after) do not fully support WinXp Newsgroups: comp.lang.ada

An Ada program that uses GTK for its GUI fails if it references a DLL written in Ada. A Visual C++ Runtime Library popup is raised with the cryptic verse "This application has requested to terminate it in an unusual way". This piece of nonsense actually means that the C runtime has raised an exception that is never caught which results in the abort function being called. The problem here is that it doesn't give us much clue as to what the exception is. However I believe that this error message is produced when a missing function is called from a system DLL. I.e. it can't find the entry point within the DLL.

The prime candidate for this is LibGlib-2.0-0.Dll which references

GetTickCount64 and InitializeSRWLock from Kernel32.dll. Unfortunately these routines are not present in versions prior to V6 which only came with Windows Vista.

Therefore GTK 3.8.4 provided as part of the AdaCore GtkAda release for GPL 2015 does not fully support Windows XP.

Which is very odd as support of XP was only officially dropped with GTK 3.17.1

However Gnome seem to have broken it already in v3.8.4

For full Windows XP support it is therefore better to revert to v3.8.2 that came bundled with the GtkAda release for GPL 2014.

It is hard to find out what exactly changed between 3.8.2 and 3.8.4 but the numbering seems to indicate that there were no major changes or enhancements. Except dropping XP that is!

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Fri, 18 Sep 2015 18:02:46 +0200 Subject: Re: Gtk 3.8.4 (and after) do not fully support WinXp Newgroups: comp lang ada

Newsgroups: comp.lang.ada

[...] GTK maintainers do not care about backward compatibility. There is a lot of stuff that ceases to work with each new GTK version. I tracked most of that to make GtkAda 3.8.3 working with GTK 3.10.x. I don't have 3.8.4, so I cannot tell, but my GtkAda applications work under both Windows and fully updated Linux. OK on OS X. The other problem is that on Yosemite the Gtk thread has to be the Major offenders are dialog boxes and stock items. They should generate warnings but actually they tend to crash the application. Other things are Get\_String and Set\_String of the tree and, possibly, of the list model. These corrupt stack and memory pool after several calls. The pixbuff cell renderer works no more because they are going to kill stock items. And so on. Some workarounds I did are here:

http://www.dmitry-kazakov.de/ada/ gtkada\_contributions.htm

In all cases fill your application with tracing output to localize the problem.

# Android: GNAT?

From: Cleverson Casarin Uliana <clcaul@live.com> Date: Sat, 19 Sep 2015 08:38:01 -0700 Subject: Can I make native Android apps with Ada?

Newsgroups: comp.lang.ada

I'm new to Ada and was already able to make basic programs for Windows. Now I'm looking to see if it was possible to make Android apps. I found a press release - http://www.adaic.org/press/ gnat-pro-for-android/

It appears I have to get the GNAT GPL (since I want to build my own free app), but I'm unable to find any basic documentation on how to do it, e.g., what's the correct software pieces to get, what dependencies it requires to build Android apps on Windows, some general steps for building an Android app, etc. Can you help please?

From: Luke A. Guest

<laguest@archeia.com> Date: Sat, 19 Sep 2015 20:50:44 +0000 Subject: Re: Can I make native Android apps with Ada?

Newsgroups: comp.lang.ada

>[...]

You can build GNAT for Android so you don't have to use the GPL version. There are no bindings afaik to any API.

From: David Botton <david@botton.com> Date: Sun, 20 Sep 2015 06:30:38 -0700 Subject: Re: Can I make native Android apps with Ada?

Newsgroups: comp.lang.ada

The current best way is to use Gnoga (http://gnoga.com) for Ada to develop any mobile / cloud apps. You can easily create a native Android/iOS app that wraps accessing the Gnoga server side if selling on the stores needed, but sadly there are no currently solutions for running client side. (Not exactly true, the .NET version could be used and the result passed through a .NET to ASM.js compiler available on the net, but licensing encumbrances placed on that version main thread. This restriction does not apply for Windows and Ubuntu. However damper any real interest to pursue solutions with it.)

# **Debian: SPARK: Request** for Adoption

From: Євгеній Мещеряков <eugen-8fîUuRrzOP0dnm+yROfE0A@public.gm ane.org>

Date: Tue, 27 Oct 2015 21:47:59 +0100 Subject: Bug#803195: RFA: spark --

Subject. Bug#805195. KFA. spark --SPARK programming language toolset Newsgroups: gmane.linux.debian. packages.ada

I request an adopter for the spark package.

The current upstream version of the package will not be updated. There is a new version of Spark, but it is very different from this one, see also https://bugs.debian.org/cgi-bin/ bugreport.cgi?bug=713928

The package description is:

SPARK is a formally-defined computer programming language based on the Ada programming language, intended to be secure and to support the development of high integrity software used in applications and systems where predictable and highly reliable operation is essential either for reasons of safety or for business integrity.

This package contains the tools necessary for checking if programs adhere to the SPARK rules and the tools to show freedom of runtime exceptions in those programs. To compile SPARK programs use any standards-compliant Ada compiler, such as GNAT.

# Windows (64 bit): GNAT

From: David Botton <david@botton.com> Date: Wed, 11 Nov 2015 07:11:00 -0800 Subject: One stop Win 64bit Ada Dev Newsgroups: comp.lang.ada

I was very pleased today to see that the Git for Windows SDK includes GNAT 5.2

So with one install you get a full MSYS2 64 bit development environment including Ada

https://github.com/git-for-windows/ build-extra/releases/tag/git-sdk-1.0.1

# Windows 10: Universal Apps

From: David Botton <david@botton.com> Date: Tue, 17 Nov 2015 19:11:55 -0800 Subject: Building Windows 10 Universal Apps with Ada

Newsgroups: comp.lang.ada

With Gnoga (http://gnoga.com) it is possible to build "modern" Windows apps with Ada. Until some day we have a working up to date (non GPL encumbered) .NET compiler or LLVM backend part of your code will need to be executed either on a server or the local machine as an older Win64 or Win32 service, but you can take full advantage of the platform and run the client side on an XBox, Windows PC, Phone, etc. (event submit to the app store).

Essentially the steps are:

- 1. Create a new VisualStudio JS Windows Universal App project.

- 2. Copy boot.js and jquery.min.js from gnoga/js to your\_project/js

- 3. Modify default.html to include the two js files.

- 4. Modify boot.js to hard code the server location (ws://snake.gnoga.com:8080/ gnoga for example).

Done.

You can use any Windows APIs, etc. by simply binding them like other JS script. If there is interest perhaps I'll bind some of the basics in the future. For those not familiar this solution is very different than serving out web pages, your Ada code will have direct interactive control of every element of the Windows app.

# Mac OS X: GCC

From: Simon Wright <simon@pushface.org> Date: Tue, 24 Nov 2015 17:42:12 +0000 Subject: ANN: GCC 5.2.0 for OS X El Capitan

Newsgroups: comp.lang.ada

This compiler (native only at time of writing) is on Sourceforge[1].

There's not a lot of added Ada goodness compared to 5.1.0, but the El Capitanrelated problem that David Botton recently encountered (see [2]) is fixed.

If you need PR66509 fixed and also armeabi support, put this compiler on your PATH before the 5.1.0 compiler (e.g. PATH=/opt/gcc-5.2.0/bin:/opt/gcc-5.1.0/bin:/the/rest/of/your/path)

I don't have a computer with Yosemite installed, any brave soul care to give it a try?

- [1] https://sourceforge.net/projects/ gnuada/files/GNAT\_GCC%20Mac%20 OS%20X/5.2.0/

- [2] https://gcc.gnu.org/bugzilla/ show\_bug.cgi?id=66509

# References to Publications

# **Comparing with C#**

From: Stefan Lucks <stefan.lucks@uniweimar.de>

Date: Wed, 2 Sep 2015 12:59:40 +0200 Subject: Top 10 Worst C# Features Newsgroups: comp.lang.ada Eric Lippert from the C# design team has an interesting article on the ten worst features of C#. At least eight of these have been solved in Ada. Did Jean I. time-travel into the future and learned from the C# mistakes, when designing Ada?

Lean back and enjoy!

http://www.informit.com/articles/ article.aspx?p=2425867

BTW, the two issues that are, to some degree, applicable to Ada are

#9 Comparison operators for your own arithmetic (e.g., for your own rational numbers).

In Ada, the "/="-operator is automatically the negation of "=". Which is great. But given "=", "<", and ">", why does one have to implement "<=" and ">=", as well. (Five Operators, where three would suffice.) (\*)

The situation with C# is even worse. You need to define/override at least nine methods.

#2 Finaliz(ers) are fragile

In Ada, the finalize procedure for an object can be called more than once, Finalize should rather not raise an exception, ... apparently, C# finalizers suffer from similar problems: "any time a finalizer runs, you could argue that the program either has a bug or is in a dangerous state, such as being shut down unexpectedly via a thread abort".

The remaining eight C# issues have been solved in Ada.

(\*) One might argue that two operators, e.g., "=" and "<" would suffice, rather than three. If neither A=B nor A<B, then A>B is obvious, isn't it?

But not all sorts of "arithmetic", where you want to take comparisons, have the property that either of A=B, A>B, A<B is true:

- Arithmetic with "special values", such as "Not a Number" for floating point operations. If A is NaN, then neither A=B nor A>B nor A<B would hold, even if B is also NaN.

- Another example would be sets: A<B would indicate "A is a proper subset of B. If, e.g., A={1} and B={2,3}, then neither A=B nor A<B nor A>B.

On the other hand, A <= B should never mean anything different from

(A < B) or (A = B)!

Similarly for  $A \ge B$ .

From: Randy Brukardt <randy@rrsoftware.com> Date: Wed, 2 Sep 2015 14:39:39 -0500 Subject: Re: Top 10 Worst C# Features Newsgroups: comp.lang.ada

> #2 Finaliz(ers) are fragile [...]

Based on the article, the situation in Ada

is far less bad than the C# one. His description of C++ finalizers apply to Ada's as well: "[they] run deterministically, run on the current thread, and never run on partially constructed objects." Moreover, they always run when objects are destroyed, while apparently in C# they don't run for explicit calls to Dispose.

Ada's issues come from two things: extremely rare cases involving exceptions where a finalizer might start twice, and the fact that someone can explicitly call it on an object. If one has control over the entire system, neither of these cases need happen; a program like AdaControl can enforce appropriate style rules to avoid problems.

If not, it's relatively easy to make Finalize callable multiple times (you just need a "Valid" bit in the object, which is turned off by Finalize; if it's off, Finalize does nothing).

Of course, Ada gets this by not supporting garbage collection on objects that have non-trivial finalization (such an object cannot be garbage collected until the finalization has run, meaning they have to exist until they go out of scope, meaning no useful garbage collection can happen. Fixing that would probably introduce more problems (although if the points at which garbage collection could happen were appropriately limited it would not be a huge issue; if this issue is ever addressed in Ada, which would have to be the case).

In any case, Ada's situation is nothing like the asynchronous mess he describes for C#. It may not be perfect, but it's a heck of a lot better than C#.

# **Building High Integrity Applications with SPARK**

From: Roderick Chapman

<roderick.chapman@googlemail.com> Date: Thu, 3 Sep 2015 01:10:33 -0700 Subject: New SPARK book is published today

Newsgroups: comp.lang.ada

I'm pleased to say that the all-new SPARK book by John McCormick and Peter Chapin is published today. It covers the SPARK 2014 language and tools in some detail. Available for order on Amazon and all the usual places now. For example:

http://www.amazon.com/ Building-High-Integrity-Applications-SPARK/dp/1107656842/ref=sr\_1\_1?ie=U TF8&qid=1441267363&sr=8-1&keywords=mccormick+chapin+spark

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Thu, 3 Sep 2015 10:08:59 +0000 Subject: Re: New SPARK book is published today Newsgroups: comp.lang.ada

> [...] Some information is available on the publisher's web-page for the book. See the tab "Contents" on: <http://www.cambridge.org/us/academic/ subjects/computer-science/programminglanguages-and-applied-logic/buildinghigh-integrity-applications-spark> From: Georg Bauhaus <bauhaus@futureapps.de> Date: Fri, 18 Sep 2015 16:06:46 +0200 Subject: Re: New SPARK book is published todav Newsgroups: comp.lang.ada A Kindle "sample" may now be received from Amazon; it includes the Preface, with chapter outlines, some of the introductory chapter, and also this TOC: Preface 1 Introduction and Overview 1.1 Obtaining Software Quality 1.2 What Is SPARK? 1.3 SPARK Tools 1.4 SPARK Example Summary Exercises 2 The Basic SPARK Language 2.1 Control Structures 2.2 Subprograms 2.3 Data Types 2.4 Subprograms, More Options Summary Exercises 3 Programming in the Large 3.1 Definition Packages 3.2 Utility Packages 3.3 Type Packages 3.4 Variable Packages 3.5 Child Packages 3.6 Elaboration Summary Exercises 4 Dependency Contracts 4.1 Data Dependency Contracts 4.2 Flow Dependency Contracts 4.3 Managing State 4.4 Default Initialization 4.5 Synthesis of Dependency Contracts Summary Exercises 5 Mathematical Background 5.1 Propositional Logic 5.2 Logical Equivalence 5.3 Arguments and Inference 5.4 Predicate Logic Summary

Exercises 6 Proof 6.1 Runtime Errors 6.2 Contracts 6.3 Assert and Assume 6.4 Loop Invariants 6.5 Loop Variants 6.6 Discriminants 6.7 Generics 6.8 Suppression of Checks Summary Exercises 7 Interfacing with SPARK 7.1 SPARK and Ada 7.2 SPARK and C 7.3 External Subsystems Summary Exercises 8 Software Engineering with SPARK 8.1 Conversion of SPARK 2005 8.2 Legacy Ada Software 8.3 Creating New Software 8.4 Proof and Testing 8.5 Case Study: Time Stamp Server Summary 9 Advanced Techniques 9.1 Ghost Entities 9.2 Proof of Transitive Properties 9.3 Proof Debugging 9.4 SPARK Internals Notes References Index **Comparing SPARK and Ada** From: Claire Dross, AdaCore Date: Thu Nov 19 2015 Subject: What's the Difference Between Ada and SPARK? URL: http://electronicdesign.com/ dev-tools/what-s-difference-betweenada-and-spark Ada is a general-purpose language, like

Ada is a general-purpose language, like C++ or Java, supporting the usual features of modern programming languages, such as data encapsulation, object orientation, templates (called "generics"), exceptions, and tasking. Originally defined in 1983, it has undergone several revisions, the latest in 2012. What sets Ada apart from other general-purpose languages is that it was designed from the start with reliability, safety, and security in mind. Not surprisingly, Ada is used in domains where the correctness of software is critical: space, avionics, air-traffic control, railway, and military.

SPARK is a specialized subset of Ada designed to facilitate the use of formal methods, so that correctness of software or other program properties can be guaranteed with mathematics-based assurance. Therefore, SPARK is used in the same domains as Ada, by those who value the strong guarantees offered by formal methods.

[...]

# Ada Inside

### **MAX! Home Automation**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Mon, 24 Aug 2015 18:53:55 +0200 Subject: ANN: MAX! home automation v1.0 released Newsgroups: comp.lang.ada

MAX! home automation is a GTK+ application to manage ELV/eQ-3 MAX! cubes. A cube is a gateway to a network of radiator thermostats, shutter contacts etc.

http://www.dmitry-kazakov.de/ada/ max\_home\_automation.htm

# LinXtris

From: Pascal Pignard <p.p11@orange.fr> Date: Wed, 16 Sep 2015 18:47:02 +0200 Subject: LinXtris for GTKAda 3. Newsgroups: gmane.comp.gnome.gtk+.ada

I've ported LinXtris (http://linxtris.sourceforge.net) from GTKAda 2 to GTKAda 3.

[...]

# What's "Outside" the Ada Inside?

From: Tero Koskinen <tero.koskinen@iki.fi> Date: Wed, 7 Oct 2015 22:42:50 +0300 Subject: Re: what does your Ada + hardware look like? Newsgroups: comp.lang.ada

> What sorts of hardware are you using with Ada? What sort of CPU, is it on a custom PCBs or off the shelf?

Gallery of my 8-bit AVR hardware can be found at https://www.flickr.com/photos/ terokoskinen/albums/ 72157625466664467

All of these run AVR-Ada. [...]

> Has anyone used IC2 or SPI from a desktop to control circuits that don't have a C firmware?

Desktop PCs rarely have I2C or SPI pins exposed. You better use some microcontroller between the I2C/SPI IC and the desktop.

http://arduino.ada-language.com/tag/ i2c.html should give you some idea. For example, I once used Arduino and Ada to read my (father's) laptop's I2C EEPROM contents:

http://arduino.ada-language.com/ recovering-ibm-thinkpad-t42-biospassword-with-avr-ada-and-arduino.html

# Natural Language Processing Tools

# From: Matteo Grella

<matteogrella@gmail.com> Date: Fri, 16 Oct 2015 05:47:00 -0700 Subject: Natural Language Processing with Ada 2012

Newsgroups: comp.lang.ada

I'm glad to inform you that at the GitHub links below, you'll find Ada 2012 used for Natural Language Processing and more in general for Artificial Intelligence/ Machine Learning.

#### Ada Dependency Parser (AdaDP)

AdaDP is a very basic multilingual statistical dependency parser written in pure Ada that I use to experiment some ideas. It is based on a shift-reduce transition-based system that produces dependency parse trees for natural language sentences using parsing model learned from annotated corpora.

https://github.com/matteo-grella/ mg-research/tree/master/ADADP

#### NLPColl Deep Parser

NLPColl Deep Parser is a dependency parser written in Ada 2012 that use Deep Learning/Word Embedding algorithms. This project derives from Stanford CoreNLP tools (see https://github.com/ stanfordnlp/CoreNLP).

https://github.com/MGMN/NLPColl/tree/ master/DeepParser

#### Machine Learning

Ada 2012 implementations of Multi-layer Perceptron and Averaged Perceptron.

https://github.com/MGMN/ ada-relax-component-collection/tree/ master/src/arcoll/machine learning

# **KDF9** Emulator

From: Bill Findlay

<yaldnif.w@blueyonder.co.uk>

Date: Fri, 6 Nov 2015 03:11:50 +0000

Subject: ee9 V2.0, the GNU Ada KDF9

emulator

Newsgroups: alt.folklore.computers, comp.lang.ada

.. is now available for OSX, Windows, Linux 32 & 64 bit, and Raspberry Pi, at:

http://www.findlayw.plus.com/ KDF9/#Emulator

Both GPL source code and systemspecific binaries are provided, along with KDF9 sample programs and data, including the famous Whetstone benchmark.

This version is written in Ada 2005; I expect the next to be in Ada 2012.

[See also "The GNU Ada KDF9 emulator, now on Raspberry Pi", AUJ 33-4, p. 244. —sparre]

# Indirect Information on Ada Usage

[Extracts from and translations of job-ads and other postings illustrating Ada usage around the world. —sparre]

Job offer [Finland] System Engineer

#### [...]

In short, Atlas-Elektronik is looking for System Engineer who knows C++, Java, Ada or Python. Location is Tampere, Finland.

The last time I was chatting with them, they had pretty big amount of Ada code in their hands. I guess the other languages are there to get more applicants. I also assume that Finnish language knowledge is not needed if you know Ada well enough.

Job offer [England]

[at Finmeccanica]

# Ada in Context

### **Returning Variable-sized Results**

From: Hadrien Grasland <hadrien.grasland@gmail.com> Date: Fri, 21 Aug 2015 01:37:22 -0700 Subject: How do typical Ada calling conventions work?

Newsgroups: comp.lang.ada

I am currently having fun reimplementing some of Numerical Recipes' code snippets in Ada. Since this is just a personal project, I do not care about scaling to very large matrices/vectors, so I chose to keep things simple by allocating arrays on the stack, rather than on the heap. But then I suddenly found myself wondering what kind of implementation magic made my code work at all.

Let me elaborate: in the C family, as far as I know, programming language rules enforce that the size of almost any variable, including function results, must be known at compile-time, with C99 VLAs as a notable exception.

This makes it easy for implementations to devise calling conventions: the caller can allocate as much space as needed for the return value in registers or on the stack frame, right before pushing parameters. Upon function return, the caller will find the result where it would expect it. However, as far as I can tell, Ada does not offer this guarantee: if I write this code, for example...

type Unconstrained\_Array is array (Positive range <>) of Integer; function Make\_Array return

Unconstrained\_Array;

...there is no way for a caller of Make\_Array to tell, in advance, how big the function's result will be. So only the callee knows enough to allocate space for its return value.

Does someone know how typical Ada implementations manage to cope with this, and if it varies a lot from one implementation to another?

From: Markus Schöpflin

Date: Fri, 21 Aug 2015 12:41:01 +0200 Subject: Re: How do typical Ada calling conventions work?

Newsgroups: comp.lang.ada

>[...]

GNAT allocates such objects on the secondary stack. Quote from the user guide:

`-Dnn[k|m]'

This switch can be used to change the default secondary stack size value to a specified size nn, which is expressed in bytes by default, or in kilobytes when suffixed with k or in megabytes when suffixed with m.

The secondary stack is used to deal with functions that return a variable sized result, for example a function returning an unconstrained String. There are two ways in which this secondary stack is allocated.

For most targets, the secondary stack is growing on demand and is allocated as a chain of blocks in the heap. The -D option is not very relevant. It only give some control over the size of the allocated blocks (whose size is the minimum of the default secondary stack size value, and the actual size needed for the current allocation request).

For certain targets, notably VxWorks 653, the secondary stack is allocated by carving off a fixed ratio chunk of the primary task stack. The -D option is used to define the size of the environment task's secondary stack.

From: Niklas Holsti

<niklas.holsti@tidorum.fi> Date: Fri, 21 Aug 2015 15:47:04 +0300 Subject: Re: How do typical Ada calling conventions work?

Newsgroups: comp.lang.ada

>[...]

I stumbled across an interesting, old discussion about GNAT's approach (it seems a secondary stack was not the initial choice) with references to some other compilers: http://computerprogramming-forum.com/ 44-ada/2227f74c82f45451.htm

#### From: Randy Brukardt

<randy@rrsoftware.com> Date: Mon, 24 Aug 2015 17:03:55 -0500 Subject: Re: How do typical Ada calling conventions work?

Newsgroups: comp.lang.ada

> I'm glad the secondary stack approach won in the end for GNAT, it sounds more efficient, clean and scalable than what they were attempting in the beginning.

I doubt that. The scheme Janus/Ada uses is much simpler: the memory is allocated off of a special storage pool and it is then freed using the same mechanism that does other finalization (indeed, the memory management [which we used in Ada 83] was repurposed to do finalization, rather than the other way around).

This is probably not as efficient as the secondary stack approach, but I find that irrelevant in 99.9% of programs. All functions that return non-elementary types are somewhat more expensive than the similar parameter passing, so if efficiency is a primary concern, one must use procedures rather than functions. The cases where function return by secondary stack would be efficient enough but function return by heap is not efficient enough are going to be quite rare [in the vast majority of cases either both are good enough or neither are] -- thus there are better things to spend effort on.

### Advice from Compiler Writers?

From: Luke A. Guest

<laguest@archeia.com> Date: Sun, 23 Aug 2015 11:16:00 -0700 Subject: Requesting advice from compiler writers

Newsgroups: comp.lang.ada

I'm one of the people considering a new Ada compiler, I would like to ask the people here who have actually done it, what their advice would be. i.e. what to aim for, what to avoid doing, etc?

I personally am aiming for a library based multi-backend system. Basically, I'd like to see a full Ada compiler frontend with an Ada backend, but with the ability to poach other backends, specifically LLVM. My initial targets are unusual, Z80, MIPS and x86 (16-bit -> 64-bit) and JVM bytecode.

From: Brian Drummond

<br/>

Newsgroups: comp.lang.ada

#### >[...]

I've mentioned before: I'd suggest looking at Gela-Asis as the front end. Natasha forked it to her Github last year, (https:// github.com/faelys/gela-asis) and (around the same time) I saw some activity on the original repo (which I can't currently see at http://gela.ada-ru.org/gela\_asis) to bring it up to date with Ada-2012.

Then I would take a good look at the GHDL project for several reasons: https://sourceforge.net/projects/ghdl-updates/?source=navbar

- It is the only example I know of, of a complex language compiler successfully developed by a single individual. (Tristan Gingold, who now works for Adacore. Before deciding to use anything from GHDL, it would be worth asking him if he's comfortable that there's no conflict of interest.)

- It supports VHDL and therefore has quite a bit in common with Ada, including explicit parallelism (though a different model to Ada tasking)

- It is written entirely in Ada up to the intermediate representation, an intermediate language called "ortho" (which I believe is Tristan's own).

- It has one back-end also written in Ada this is a JIT compiler, from "ortho" currently limited to 32-bit x86, and actually performs quite well.

- It also has backends from ortho to both gcc and LLVM, which between them cover a lot of targets, but are clearly not in Ada. (And some debugging facilities to save ortho, replay it through a backend, and to print/examine it.)

I had considered writing a layer between Gela-Asis and ortho, using the GHDL compiler as an example of how to generate ortho. And I'm still considering it...

From: Brian Drummond

<br/>

Newsgroups: comp.lang.ada

[gela-asis]

see https://www.openhub.net/p/11234

This seems to be active.

# A Limitation of Ada.Text\_IO

From: Randy Brukardt <randy@rrsoftware.com> Date: Mon, 24 Aug 2015 17:22:38 -0500 Subject: Re: Creating an empty file with Ada.Text\_IO Newsgroups: comp.lang.ada

[...]

More generally, Text\_IO is for processing files in an implementation-determined format. (And that's true to some extent for Sequential\_IO and Direct\_IO as well.) If you actually care about the bits in the file (as you might when writing a file for some other program), only Stream\_IO gives the needed control.

For example, the Janus/Ada compiler only uses our in-house Basic\_IO package for file I/O (we invented Basic\_IO for Ada 83; if we were starting today we'd use Stream\_IO which has essentially the same capabilities). The standard I/O packages just didn't work for our needs, even though we implemented them ourselves. They had too much overhead and too little control.

### SPARK: Case Coverage Rules

From: Maciej Sobczak <maciej@msobczak.com> Date: Fri, 9 Oct 2015 04:38:32 -0700 Subject: SPARK: missing case value Newsgroups: comp.lang.ada

Consider:

type Enum is (A, B, C); procedure Test (E : in Enum) with Pre => E /= C is

begin

```

case E is

when A => null;

when B => null;

end case;

end Test:

```

The Pre contract says that C is never used as a value for E. Still, GNATProve complains about missing case value C in the case statement. The compiler complains, too.

An appropriate subtype (subtype SEnum is Enum range A .. B) can solve this, but it shows some asymmetry between subtypes and contracts, where I would expect that the same subsetting effect can be achieved in both ways. Apparently (and according to AARM), the case statement does not take contracts into account, but my understanding of the rules is that it would not be against the spirit of "covering values that satisfy the predicate".

On the other hand, SPARK is supposed to be a subset of Ada, so even if the above is feasible from the SPARK point of view, it should compile as regular Ada as well and compilers are not required to do this level of static analysis. So, SPARK does not do it, because Ada might not be able to keep the pace.

What are your thoughts on this?

From: Mark Lorenzen

<mark.lorenzen@gmail.com> Date: Fri, 9 Oct 2015 05:35:03 -0700 Subject: Re: SPARK: missing case value Newsgroups: comp.lang.ada

>[...]

I think it is logical and correct. How would a compiler be able to determine the

range of E if your precondition was more complex?

I would change the case statement into something like this:

```

case E is

when A => null;

when B => null;

when C => raise Impossible;

-- or maybe Pragma Assert (False)

end case;

```

Note that you can use raise statements in SPARK as long as the program is still in SPARK i.e. the raise statement will never be executed.

From: Bob Duff <bobduff@theworld.com> Date: Fri, 09 Oct 2015 10:39:01 -0400 Subject: Re: SPARK: missing case value Newsgroups: comp.lang.ada

>[...]

That's illegal Ada, as you noted. And illegal SPARK.

But this works:

type Enum is (A, B, C); subtype A\_C is Enum with Predicate => A\_C /= B;

procedure Test (E : in A\_C) is

begin

case E is

when A => null;

-- "when B" is not needed.

when C => null;

end case;

end Test;

And that has the advantage that A\_C need not be a subrange; it can have holes.

I find that predicates are often better than preconditions, because the same precondition often applies to many parameters, and also to local variables. The predicate allows you to avoid repetition.

("Predicate =>" is a GNAT-specific extension. In Ada, you need to say "Static\_Predicate =>". IMHO the "Static\_" part is just noise, but I couldn't convince the rest of ARG.)

# Futures/Chained Function Calls?

From: Alejandro R. Mosteo <alejandro@mosteo.com> Date: Wed, 14 Oct 2015 16:30:08 +0200 Subject: Musings on RxAda Newsgroups: comp.lang.ada

Having been recently working on Java/Android apps, I have been exposed to the ReactiveX framework [1]. I think it originated on C# though.

Anyway, the gist of it is that you chain function calls (operators in their jargon) to process data asynchronously. This, in Java, with lambda functions and parameter inference leads to extremely compact, legible code that may notably simplify multithreading code.

[...]

For simplicity, I'm going to concentrate on the "map" operator, as seen on this Java example:

Observable.just("Hello, world!") .map(s -> s + " -Dan") .map(s -> s.hashCode()) .map(i -> Integer.toString(i)) .subscribe(s -> System.out.println(s));

Basically, the map operation takes some input, changes it somehow and outputs another type. The chain begins at an Observable (some data generator) and ends at a subscriber (which does something with the result). The above example takes a string, appends a signature, hashes it, and outputs the hash as a string. This does not necessarily has to happen at the moment of declaration; in general, observables emit data asynchronously.

Moving into Ada, we need an Observable type able to take different map implementations. That could be (not compiled, bear with my mistakes. Allow for 2012 syntax):

type Observable is [limited?] tagged record;

type Datum is abstract interface; -- or maybe tagged null record;

function Map (This : in out Observable; Map : access function (X : Datum'Class) return Datum'Class) return Observable;

-- or access Observable if limited

Here the 'Class are needed to avoid multiple dispatch, I think. Then you'll have to declare beforehand any mappings you need (which is more verbose and, lacking lambdas, would somehow defeat the purpose of having the logic in the chain declaration, but I see no way around it, unless the new simple expression functions can appear in-place?). Also, the need for 'Class parameters will force explicit casts in the user mappings, which I find ugly and leaves the type checks to runtime.

I guess an implementation of "RxAda" could provide many Map profile overloads for basic Ada types (from String to String and so on), but still that's a poor's man attempt.

That's as far as I've got, which is not much, but I'm a bit rusty on Ada right now. I can think of even more contrived ways using tagged types plus generics but I'm not sure they lead anywhere. I think it boils down to Ada not having lambda functions nor implicit template types a-la C++.

[1] http://reactivex.io/

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 21 Oct 2015 18:47:35 +0200 Subject: Re: Musings on RxAda

Newsgroups: comp.lang.ada

[...]

Pipeline is just a method of buffered exchange. As such it is blocking (publisher) when the subscriber is unable to process all published data.

Moreover it is unsuitable for 1-n communications. If you are OK with blocking the publisher, then no buffering is ever needed. Buffering (marshaling) is required by non-blocking but not ensures it.

And no mediator task is needed anyway, not even a protected object. 1-1 FIFO requires none of Ada's synchronization primitives.

From: Hadrien Grasland <hadrien.grasland@gmail.com> Date: Wed, 21 Oct 2015 12:09:58 -0700 Subject: Re: Musings on RxAda Newsgroups: comp.lang.ada

So you would essentially store a pipeline of data and operations in some container, then perform all of them on the same thread when the output of the pipeline is requested?

This seems much more complex to implement to me, since your operation queue needs to be able to store data of any type and operation function pointers, all in a type-safe way. As far as I can tell, you cannot use streams for that because a stream requires you to know what you are reading from it.

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Wed, 21 Oct 2015 21:35:17 +0200 Subject: Re: Musings on RxAda Newsgroups: comp.lang.ada

> So you would essentially store a pipeline of data and operations in some

> container, [...]

I don't know your requirements. In a FIFO scenario, yes, the publisher pushes the object. The subscriber pulls it out. In a blackboard scenario (non-blocking) the publisher pushes the object and the subscribers scan the blackboard for updates.

Of course in a modern typed language like Ada you would not mess with "data and operations." There are objects for that. The type of the object determines the operations.

>[...]

That is because you are trying to think about it in terms of C. Ada is not C, luckily. It is quite straightforward to marshal T'Class objects with a dispatching operation Do\_It. And yes, it is as much easy to marshal handles to reference-counted objects if objects are expected large (and you have shared memory).