# ADA USER JOURNAL

## Volume 37 Number 4 December 2016

## Contents

|                                                                                                                                                                                                  | Page              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                                                                            | 182               |

| Editorial                                                                                                                                                                                        | 183               |

| Quarterly News Digest                                                                                                                                                                            | 185               |

| Conference Calendar                                                                                                                                                                              | 197               |

| Forthcoming Events                                                                                                                                                                               | 203               |

| Article from the Industrial Track of Ada-Europe 2016                                                                                                                                             |                   |

| V. Monfort<br>"Middleware for a Distributed and Hot-Redundant Software in Ada 2012"                                                                                                              | 207               |

| Proceedings of the "Workshop on Challenges and New Approaches for Dependable ar<br>Cyber-Physical System Engineering" of Ada-Europe 2016                                                         | nd 212            |

| S. Mazzini, D. Cancila, A. Bagnato, P. R. Conmy and L. Rioux " <i>Editorial</i> "                                                                                                                | 213               |

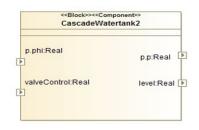

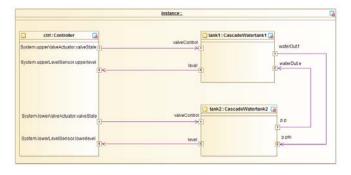

| A. Bagnato, E. Brosse, I. Quadri and A. Sadovykh<br>"SysML for Modeling Co-simulation Orchestration over FMI: the INTO-CPS Appr                                                                  | coach" 215        |

| S. Ali, T. Yue and M. Zhang<br>"Tackling Uncertainty in Cyber-Physical Systems with Automated Testing"                                                                                           | 219               |

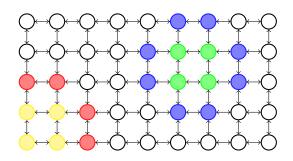

| V. Ciancia, D. Latella, M. Loreti and M. Massink<br>"Spatio-temporal Model-Checking for Collective Adaptive Systems in QUANTICO.                                                                 | <i>L</i> " 223    |

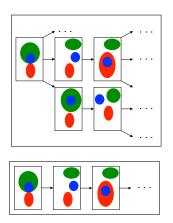

| R. Giorgi, S. Mazumdar, S. Viola, P. Gai, S. Garzarella, B. Morelli, D. Pnevmatika<br>D. Theodoropoulos, C. Álvarez, E. Ayguadé, J. Bueno, A. Filgueras,<br>D. Jiménez-González and X. Martorell | tos,              |

| "Modeling Multi-board Communication in the AXIOM Cyber-Physical System"                                                                                                                          | 228               |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                                                                        | 236               |

| Ada-Europe Sponsors                                                                                                                                                                              | Inside Back Cover |

## Editorial Policy for Ada User Journal

#### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

## **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

## **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

## **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

### Announcements and Reports

We are happy to publicise and report on events that may be of interest to our readers.

## Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### Submission Guidelines

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

## Editorial

This issue of the Ada User Journal publishes the Proceedings of the "Workshop on Challenges and New Approaches for Dependable and Cyber-Physical System Engineering", which took place June 17, co-located with Ada-Europe 2016, in Pisa, Italy. This workshop brought together industry and research participants, for a full-day discussion on dependability and critical issues of Cyber-Physical Systems (CPS), a good complement to the already rich program of the Ada-Europe conference.

The workshop program included presentations from academia and industry, as well as a panel discussion. The proceedings reflect part of this rich content, starting with an Editorial by the organizers, followed by a set of technical papers. The first workshop paper, from a group of authors from Softeam, France, discusses the use of model-based design of CPS in the INTO-CPS European project. The next paper, by authors from Simula Research Laboratory and University of Oslo, Norway, present the approach of the U-Test-EU project for testing CPSs considering uncertainty. Afterwards, authors from CNR and Università di Firenze, Italy, explain the issues on model-checking of spatial and temporal properties of CPS, a work being done in the FET QUANTICOL project. Closing the proceedings, authors from University of Siena and Evidence, Italy, FORTH, Crete and BSC, Spain, present the main choices in the design of the interconnect of the AXIOM CPS board.

The issue also continues the publication of the contents of the industrial track of Ada-Europe 2016, with a paper by Vincent Monfort, of Systerel, France, describing a new Ada 2012 middleware for distributed hot-redundant software for railway control systems.

Finally, and as usual, the issue provides the News Digest, Calendar and Forthcoming Events sections, provided by the News and Events Editors, respectively Jacob Sparre Andersen and Dirk Craeynest. A special mention to Ada-Europe 2017, which will take place at the Palais Eschenbach, in the heart of Vienna, Austria, 12-16 June 2017: we are looking forward to see the Ada community gathering there for the usual high-quality Ada-Europe week.

Luís Miguel Pinho Porto December 2016 Email: AUJ\_Editor@Ada-Europe.org

## Proven Test Solutions for Reliable Embedded Software

"VectorCAST is unique in that it provides us with the ability to increase the reliability and quality of our flight software."

vectorcast.com

VectorCAST is a TÜV SÜD Certified Software Tool for Safety Related Development

Vector Software, Inc.

Golden Cross House | 8 Duncannon Street | London WC2N 4JF UK | +44 203 603 0120 | sales@vectorcast.com

## Quarterly News Digest

## Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

## Contents

| Ada-related Events         | 185 |

|----------------------------|-----|

| Ada-related Resources      | 185 |

| Ada-related Tools          | 186 |

| Ada and Operating Systems  | 191 |

| References to Publications | 192 |

| Ada Inside                 | 193 |

| Ada in Context             | 194 |

|                            |     |

## Ada-related Events

[To give an idea about the many Adarelated events organised by local groups, some information is included here. If you are organising such an event feel free to inform us as soon as possible. If you attended one please consider writing a small report for the Ada User Journal. —sparre]

## High Integrity Software Conference

From: AdaCore Press Center Date: Tue 20 Sep 2016 Subject: AdaCore and Altran to sponsor

- High Integrity Software Conference URL: http://www.adacore.com/press/

- adacore-altran-high-integrity-softwareconference/

AdaCore and Altran have announced their renewed sponsorship of the annual High Integrity Software Conference, which takes place in Bristol on 1 November 2016.

Following a successful conference in 2014 and 2015, organisers the University of Newcastle, AdaCore and Altran have once again compiled a complete technical programme (available at www.his-2016.co.uk/programme) to be delivered by prominent academic and industrial experts, covering topics including security, autonomy, standards and techniques & tools. This programme will be complemented by keynote talks discussing two of the high-integrity software community's most debated topics: Reasoning with Big Code from Dr Dino Stefano of Facebook and An Alternative Approach to DO-178 from Duncan Brown of Rolls-Royce.

The conference has gone from strength to strength since its inauguration in 2014. As well as the sponsorship of organisers AdaCore and Altran, this year it will benefit from the additional official support of key players BAE Systems and Jaguar Land Rover – a vote of confidence in the conference's important objective of sharing best practice in the context of today's increasing reliance on software in performing critical industrial tasks.

"HIS is one of the best conferences we attend globally due to the quality of the programme, the relevance of the exhibitors and the industries represented by the attendees," says Jamie Ayre, Commercial Team Lead at AdaCore. "We hope that the conference continues to grow from strength to strength with each edition."

Stuart Matthews, SPARK Product Manager at Altran UK, said: "We are delighted once again to be involved in this key annual conference for the software industry. This year, support has been added by two major UK companies – BAE Systems and Jaguar Land Rover – reinforcing the position of the conference as a focus for sharing experience and innovations in the field of trustworthy software development."

To find out more and register, visit www.his-2016.co.uk.

## FOSDEM 2017

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Wed, 5 Oct 2016 21:55:57 +0200 Subject: \*No\* Ada DevRoom at FOSDEM 2017!

To: ADAFOSDEM@LS.KULEUVEN.BE

[...]

I am most disappointed to inform you that our proposal for an Ada DevRoom was \*not\* selected.

The FOSDEM organizers gave the following rationale: "[...] We also left out some long time participants to give other projects a chance as well this year." So unfortunately, no 8th Ada DevRoom at FOSDEM 2017...

[...]

[See also "FOSDEM 2017", AUJ 37-3, p. 125. —sparre]

## **Ada-related Resources**

## Ada on Social Media

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Mon Nov 7 2016 Subject: Ada on Social Media Ada groups on various social media:

- LinkedIn: 2\_528 members [1]

- Reddit: 937 readers [2]

- Google+: 708 members [3]

- StackOverflow: 633 followers [4]

- Freenode 81 participants [5]

- Twitter: 9 tweeters [6]

[1] https://www.linkedin.com/ groups?gid=114211

[2] http://www.reddit.com/r/ada/

[3] https://plus.google.com/communities/ 102688015980369378804

[4] http://stackoverflow.com/questions/ tagged/ada

[5] #Ada on irc.freenode.net

[6] https://twitter.com/search?f=realtime &q=%23AdaProgramming

[See also "Ada on Social Media", AUJ 37-3, p. 125. —sparre]

## **Repositories of Open Source** Software

| From: Jacob Sparre Andersen<br><jacob@jacob-sparre.dk></jacob@jacob-sparre.dk> |      |  |

|--------------------------------------------------------------------------------|------|--|

| Date: Mon Nov 7 2016                                                           |      |  |

| Subject: Repositories of Open Source software                                  |      |  |

| GitHub: 1_022 repositories                                                     | [1]  |  |

| 359 developers                                                                 | [1]  |  |

| 1_335 issues                                                                   | [1]  |  |

| Rosetta Code: 629 examples                                                     | [2]  |  |

| 30 developers                                                                  | [3]  |  |

| 1 issue                                                                        | [4]  |  |

| Sourceforge: 252 repositories                                                  | [5]  |  |

| BlackDuck OpenHUB: 211 projects                                                | [6]  |  |

| Bitbucket: 89 repositories                                                     | [7]  |  |

| OpenDO Forge: 24 projects                                                      | [8]  |  |

| 500 developers                                                                 | [8]  |  |

| Codelabs: 21 repositories                                                      | [9]  |  |

| AdaForge: 8 repositories                                                       | [10] |  |

| [1] https://github.com/search?q=language<br>%3AAda&type=Repositories           |      |  |

| [2] http://rosettacode.org/wiki/<br>Category:Ada                               |      |  |

| [3] http://rosettacode.org/wiki/<br>Category:Ada_User                          |      |  |

| [4] http://rosettacode.org/wiki/Categ                                          | orv. |  |

[4] http://rosettacode.org/wiki/Category: Ada\_examples\_needing\_attention [5] http://sourceforge.net/directory/ language%3Aada/

[6] https://www.openhub.net/tags? names=ada

[7] https://bitbucket.org/repo/all? name=ada&language=ada

[8] https://forge.open-do.org/

[9] http://git.codelabs.ch/

[10] http://forge.ada-ru.org/adaforge

[See also "Repositories of Open Source Software", AUJ 37-3, p. 125. —sparre]

## **Ada-related Tools**

## Libkeccak (SHA3)

From: Daniel King

<damaki.gh@gmail.com> Date: Mon Aug 22 2016 Subject: Keccak and SHA3 algorithms in SPARK/Ada

URL: https://github.com/damaki/libkeccak

#### Libkeccak

This project implements the Keccak family of sponge functions and related constructions using the SPARK 2014 programming language.

libkeccak implements the following constructions:

- The Keccak-p permutation for state sizes of 25, 50, 100, 200, 400, 800, and 1600 bits (see [1] and [2]).

- The Sponge construction

- The Duplex construction

- Hash functions based on the Sponge construction

- eXtendable Output Functions (XOF) based on the Sponge construction

libkeccak also provides concrete implementations for the hash functions and XOFs described in NIST FIPS 202 (see [1]):

- Hash functions:

- o SHA3-224

- o SHA3-256

- o SHA3-384

- o SHA3-512

- XOFs:

- o SHAKE128

- o SHAKE256

- o RawSHAKE128

#### o RawSHAKE256

Hash function configurations are also provided for the hash functions defined by the Keccak team which were submitted in the SHA-3 competition:

- Keccak-224

- Keccak-256

- Keccak-384

- Keccak-512

These hash functions differ from the final SHA-3 hash functions only in that the SHA-3 functions append two additional bits to each message, whereas the Keccak hash functions do not.

#### Example

Here's an example of calculating the SHA3-256 hash of a byte array (array of type Interfaces.Unsigned\_8):

with Keccak.Types;

```

with SHA3;

```

function Compute\_Hash(Data : in Keccak.Types.Byte\_Array) return SHA3.SHA3\_256.Digest\_Type

is Ctu

Ctx : SHA3.SHA3\_256.Context; Digest : SHA3.SHA3\_256.Digest\_Type; begin

SHA3.SHA3\_256.Init (Ctx); SHA3.SHA3\_256.Update (Ctx, Data); SHA3.SHA3\_256.Final (Ctx, Digest); return Digest;

end Compute\_Hash;

#### License

Libkeccak is licensed under the 3-clause BSD license.

#### [...]

Formal Verification

SPARK 2014 and GNATprove are used to provide proof that the implementation is free of errors such as: integer overflows, buffer overruns, use of uninitialized variables, and that all loops terminate. Nothing is provided currently to prove that the library correctly implements the algorithms according to the specifications. However, there are tests to provide assurances of the correctness of the algorithms with the Known Answer Tests. It is intended at some point to add proof that the algorithms correctly implement the specification.

#### Testing

Correctness of the algorithms is demonstrated using a combination of unit testing and Known Answer Tests (KAT). The Known Answer Tests comprise the bulk of the tests and they provide assurance that the algorithms are implemented correctly.

The unit tests aim to cover the cases that are not covered by the KAT, such as boundary conditions. As the project moves forwards I will experiment with replacing tests with proof.

#### <u>References</u>

[1] NIST FIPS PUB 202 - SHA-3 Standard: Permutation-Based Hash and Extendable output Functions. August 2015 http://nvlpubs.nist.gov/nistpubs/ FIPS/NIST.FIPS.202.pdf [2] The Keccak Reference Version 3.0. January 2011 http://keccak.noekeon.org/ Keccak-reference-3.0.pdf

[3] Cryptographic Sponge Functions Version 0.1. January 2011 http://sponge.noekeon.org/CSF-0.1.pdf

## **Request: Scanner** Library/Binding

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Sun, 18 Sep 2016 13:25:57 -0700 Subject: Scanner library Ada binding? Newsgroups: comp.lang.ada

I'm scanning all the liner notes from my CDs (several hundred).

I've been using some old Epson software, but it's tedious. There are only 3 sizes of paper I need to scan, but the software doesn't provide for saving the sizes, so I have to "preview" and "drag the rect" for each change in size.

So I'd like to write some code to do that.

I found a Python TWAIN module, but the binary distribution is not compatible with any binary Python I could find, and compiling it from source requires MSVC (which I don't have).

So I'm looking for an Ada solution. A web search for "Ada TWAIN" didn't find anything relevant.

Does anyone have an Ada binding to the Windows TWAIN interface? I'm on 64 bit Windows 8.1, GNAT GPL 2016 (32 bit).

Or I could try Linux; I've got VMWare installed (haven't tried to see if that can see the scanner).

## Random Fixed Point Numbers

From: Robert I. Eachus <rieachus@comcast.net> Date: Mon, 19 Sep 2016 12:07:19 -0700 Subject: Re: Ada.Numerics.Float\_Random. Generator question

Newsgroups: comp.lang.ada

> [...]

[...] First, what you seem to be asking for is a PRNG that selects from a uniform distribution of fixed point values. To do this take the generic discrete random package, and redeclare it with a fixed point type:

#### generic

type Result\_Subtype is delta <>;

package My\_Fixed\_Random is

-- Basic facilities

type Generator is limited private; function Random (Gen : Generator) return Result\_Subtype; procedure Reset (Gen : in Generator; Initiator : in Integer); procedure Reset (Gen : in Generator); -- Advanced facilities

type State is private;

procedure Save (Gen : in Generator; To\_State : out State);

procedure Reset (Gen : in Generator; From\_State : in State);

Max\_Image\_Width : **constant** :=

implementation-defined integer value; function Image (Of\_State : State)

return String; function Value (Coded\_State : String)

return State;

#### private

[...]

end My\_Fixed\_Random;

Now in the body, put an instance of generic discrete random fit to your fixed point type:

package body My\_Fixed\_Random is

type Hidden is range Int64 (Result\_Subtype'First / Result\_Subtype'Small) .. Int64 (Result\_Subtype'Last / Result\_Subtype'Small);

#### package Hidden\_Pkg is new Ada. Numerics.Discrete\_Random(Hidden);

Complete with the operations from My\_Fixed\_Random, multiplying by 'Small and converting to Result\_Subtype where needed. All done. ;-) I wish I had gotten this package added to the Numerics section, as you can see it is about a page of very easy code. But there were lots of other issues that needed resolving, and not enough time to resolve them all.

Now for the evils that I hope you never meet. With this package, you should generate only numbers that are multiples of 'Small, and each legal value for Result\_Subtype should occur with equal probability. You might have an issue with a value next below 'First, but usually if you have a fixed point type that officially has 2<sup>n</sup> - 1 values, you will know what to do to avoid Constraint\_Error. More troubling is that the language rules allow for fixed point types where the specified 'Small or 'Delta does not evenly divide one. I do think that permission is right-but if you use it, you had better know a lot about numerics.

## GLOBE\_3D

From: Gautier de Montmollin

<gautier.de.montmollin@gmail.com>

Date: Mon Sep 26 2016

Subject: GLOBE\_3D - a GL 3D engine in Ada

URL: http://globe3d.sourceforge.net/ Features:

- unconditionally portable sources (one set of sources for all platforms)

- real-time rendering; fast with a 3D hardware-accelerated graphics card

- full eye movements and rotations

- displays combinations of colours, materials, textures

- transparency

- multitexturing (diffuse + specular) [NEW]

- multiple area rendering with the portal technique, e.g. for inner scenes

- collision detection

- binary space partition (BSP)

- input-output of 3D objects or groups of objects linked to each other by portals

- easy management of resources like textures (.bmp, .tga, .jpg, .gif, .png), BSP trees and objects, stored in .zip files

- screenshots (.bmp) and video captures (.avi)

- multi-view support

- vectorized geometry support

Goodies:

- randomly extruded surface generator Tools:

- Export from Blender through Wavefront (.obj / .mtl) models and the o2g tool [NEW]

- VRML virtual world compiler, through the wrl2ada translator

- GMax / 3D Studio Max scene exporter & compiler, through the max2ada translator

- Compilation of game maps or levels from the Doom 3, Quake 4 or GTK Radiant level editors through the d3a (to Ada) translator or the d3g (to .g3d) tool.

[See also "GLOBE\_3D", AUJ 37-3, p. 126. —sparre]

## Zip-Ada

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Sat, 8 Oct 2016 04:56:14 -0700 Subject: Ann: Zip-Ada v.52 Newsgroups: comp.lang.ada

Changes in '52', 08-Oct-2016:

- UnZip.Streams: all procedures have an additional (optional) Ignore\_Directory parameter.

- Zip.Compress has the following new methods with improved compression: LZMA\_3, Preselection\_1 (replaces Preselection), Preselection\_2.

Preselection methods use now entry name extension and size for improving compression, while remaining 1-pass methods.

For those interested about what's happening "under the hood", LZMA.Encoding now computes an estimation of the predicted probabilities of some alternative encodings and chooses the most probable one - it gives an immediate better local compression. Sometimes the repetition of such a repeated short-run improvement has a long-run positive effect, but sometimes not - that's where it's beginning to be fun...

URL: https://sf.net/projects/unzip-ada/ [See also "Zip-Ada", AUJ 37-3, p. 127. —sparre]

## ADHCP

From: codelabs.ch Date: Wed Oct 12 Subject: ADHCP URL: https://codelabs.ch/adhcp/

[Version 0.4.2 —sparre]

ADHCP is an implementation of the DHCP protocol in Ada. Currently the project provides client services for DHCPv4, DHCPv6 and relay services for DHCPv4.

The ADHCP DHCPv4/DHCPv6 clients are D-Bus aware and can be used on most modern Linux distributions as replacement for other clients such as ISC's dhclient or busybox's udhcpc.

#### Licence

Copyright (C) 2011-2016 secunet Security Networks AG

Copyright (C) 2011-2016 Reto Buerki <reet@codelabs.ch>

Copyright (C) 2011-2016 Adrian-Ken Rueegsegger <ken@codelabs.ch>

Free use of this software is granted under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or (at your option) any later version.

#### Download

Release version

The current release version of ADHCP is available at

https://www.codelabs.ch/download/.

#### Verify a Release

To verify the integrity and authenticity of the distribution tarball, import the key https://www.codelabs.ch/keys/0xBB7938 15pub.asc and type the following command:

\$ gpg --verify adhcp- version}.tar.bz2.sig

The key fingerprint of the public key (0xBB793815) is:

Key fingerprint = A2FB FF56 83FB 67D8 017B C50C F8C5 F8B5 BB79 3815

Development version

The current development version of ADHCP is available through its git repository:

\$ git clone https://git.codelabs.ch/git/adhcp.git

A browsable version of the repository is also available here:

<sup>[...]</sup>

https://git.codelabs.ch/?p=adhcp.git

#### Build

To compile ADHCP on your system, you need to have the following software installed:

- GNAT compiler: https://www.gnu.org/software/gnat/ gnat.html

- Anet: https://www.codelabs.ch/anet/

- Alog: https://www.codelabs.ch/alog/

- D\_Bus/Ada: https://www.codelabs.ch/dbus-ada/

If you want to run the unit tests before installation of ADHCP (which is recommended) you furthermore need to have the following installed:

- Ahven (Test-Framework):

http://ahven.stronglytyped.org/

#### **Testing**

Before you install ADHCP services on your system, you might want to test if everything works as expected. ADHCP contains a unit test suite which can be run by entering the following command:

#### \$ make tests

All tests should be marked with PASS behind the test name.

#### **Installation**

To install ADHCP on your system, type the following:

\$ make DESTDIR=/ install

If DESTDIR is not specified, /usr/local is used.

Using adhcp\_client on a Linux Desktop

This section describes the steps needed to use adhcp\_client as DHCPv4 client on a Linux Desktop with NetworkManager. Since NetworkManager does not (yet) support ADHCP directly, an additional symlink and the adhcp\_client\_wrapper binary are needed.

The following procedure has been tested on Debian squeeze and testing:

- # cd /sbin

- # dpkg-divert --add --rename --divert /sbin/dhclient.real /sbin/dhclient

- # In -s /usr/local/sbin/adhcp\_client\_wrapper dhclient

If you choose another installation DESTDIR which is not in PATH add the following symlinks in /usr/local/sbin:

- # In -s \$DESTDIR/sbin/adhcp\_client adhcp\_client

- # In -s \$DESTDIR/sbin/adhcp\_notify\_dbus adhcp\_notify\_dbus

Then re-activate a NetworkManager connection which uses DHCP. If it does not work check syslog for error messages.

### RFC conformity

The ADHCP implementation is designed to be simple and supports only essential features while still conforming to the related DHCP RFCs. The RFC compliance of the DHCPv4 implementation is documented here.

The RFC compliance of the DHCPv6 implementation is tested using the TAHI DHCPv6 Conformance Test Suite. The results can be found here.

#### Manual Pages

For more information about a specific ADHCP service or binary consult the manual pages:

- adhcp\_client(8)

- adhcp\_notify\_dbus(8)

- adhcp\_notify\_simple(8)

- adhcp\_client6(8)

- adhcp\_notify6\_dbus(8)

- adhcp\_notify6\_isc\_script(8)

- adhcp\_client\_wrapper(8)

- adhcp\_relay(8)

## **Simple Components**

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Thu, 13 Oct 2016 18:54:34 +0200 Subject: ANN: Simple Components for Ada v 4.16

Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, multiple connections server/client designing tools.

http://www.dmitry-kazakov.de/ada/ components.htm

This version fixes a bug in GNAT.Sockets.Server. The bug caused Constraint\_Error in upon stopping a client after it failed to connect.

[See also "Simple Components (et al.)", AUJ 37-3, p. 126. —sparre]

## AdaSubst and AdaDep

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Tue, 18 Oct 2016 10:26:57 +0200 Subject: [Ann] New versions of AdaSubst and AdaDep Newsgroups: comp.lang.ada Two utilities offered by Adalog (GMGPL of course), that have been updated and improved after a period of (hmm) sleep. Executable versions are provided for use with Gnat GPL 2016.

### AdaSubst:

A tool for making semantic substitution in Ada code. Provided functions include:

- Translate: Change identifiers projectwide, including when you move elements from one package to another. Adjusts the code considering all visibility rules, updates with and use clauses as necessary. Great for reorganizing projects.

- Unuse: remove use clauses, and turns all identifiers that were visible due to the use clauses to full names. Great if you like use clauses, but your clients don't!

- Unrepresent: remove all representation clauses from Ada code. Useful if you want to check your code with a different compiler, but representation clauses are incompatible.

## AdaDep:

A tool for analysing dependencies. AdaDep tells you, for each withed unit, which elements are actually used.

Both can be downloaded from Adalog's components page:

http://www.adalog.fr/en/components.html Enjoy!

## Ada Security

From: Stephane Carrez <Stephane.Carrez@gmail.com> Date: Sat Oct 29 2016 Subject: stcarrez/ada-security: Ada Security URL: https://github.com/stcarrez/

#### Ada Security Library

ada-security

[Implementation of RFC 6749 is under way.]

This Ada05 library provides some security frameworks needed by some Web applications. It allows a web application to integrate easily with Google, Yahoo!, Facebook and Google+ authentication systems. The library includes:

- An OpenID client authentication,

- An OAuth 2.0 client authentication,

- An OpenID Connect authentication framework,

- A policy based security framework to protect the resources

[...

The package provides a simple AWS server that illustrates the OpenID and OpenConnect authentication. [...]

Before launching the demo server, you must update the 'samples.properties' file

and change the lines that contain PUT-HERE-YOUR-FACEBOOK-xxx and PUT-HERE-GOOGLE-xxx with your client ID and client secrets. These two changes are required by the OAuth and OpenID Connect framework only. [...]

Documentation:

The Ada Security sources as well as a wiki documentation is provided on: https://github.com/stcarrez/ada-security

[See also "Ada Web Application", AUJ 35-3, p. 158. —sparre]

## **Emacs Ada Mode**

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Tue, 1 Nov 2016 14:14:26 -0700 Subject: Emacs Ada mode 5.2.1 now available Newsgroups: comp.lang.ada

Emacs Ada mode 5.2.1 is now available in Gnu ELPA

https://savannah.nongnu.org/projects/ ada-mode

http://www.nongnu.org/ada-mode/

[See also "Emacs Ada Mode", AUJ 37-3, p. 127. —sparre]

## **Microsimulation Model** Library

From: Graham Stark

<graham.stark@virtual-worlds.biz> Date: Tue Nov 01 2016

Subject: grahamstark/tax\_benefit\_model\_ components: Code used to build microsimulation models, mostly in the Ada language

URL: https://github.com/grahamstark/ tax\_benefit\_model\_components

#### Microsimulation Model Components

This is a moderately large collection of code used to build microsimulation models, mostly in the Ada language.

#### It includes:

Several specialist tabulators

- An implementation of a Piecewise Linear Budget Constraint generator (see: http://www.ifs.org.uk/publications/2063)

- Interfaces to various large scale sample survey datasets;

- Utilities for building web interfaces;

- Affordability Indexes;

- Inequality Measures;

- Data Re-Weighting routines

- Tax Calculators; and

- Optimisation Routines.

There is also an experimental complete South African tax benefit model, and some, but not all, of the code required for a UK Tax Benefit model.

We've taken the liberty of bundling four useful libraries with this code. We're very grateful to the original authors:

- Strings Edit by Dmitry A.Kazakov (http://www.dmitry-kazakov.de); see http://www.dmitrykazakov.de/ada/strings\_edit.htm

- Zip-Ada by Gautier de Montmollin

- (http://sourceforge.net/users/gdemont/); see http://unzip-ada.sourceforge.net/

- Numeric IO by John P Woodruff (mailto:jpwoodruff@irisinternet.net); see http://www.dmitrykazakov.de/reusable\_code.htm

- XIA (XPath In Ada) by Marc A. Criley (mailto:mc@mckae.com); see http://www.mckae.com/xia.html

Contact: Graham Stark (graham.stark@virtual-worlds.biz)

See: http://virtual-worlds-research.com

## Natools

- From: Natasha Porté

- <lithiumcat@instinctive.eu>

- Date: Tue Nov 1 2016

- Subject: faelys/natools: Miscellaneous small utilities in Ada, gathered in one shared library

- URL: https://github.com/faelys/natools

### Natools

This library gather all reusable packages written by Natasha Kerensikova that are too small to fit in a project by themselves.

It contains the following package hierarchy:

- Accumulators: an interface for string accumulator objects and stacks of accumulators

o String Accumulator Linked Lists: a basic implementation of an accumulator stack using a reference accumulator

- Chunked\_Strings: an implementation of unbounded strings backed by noncontiguous fixed-size chunks of memory

- Constant\_Indefinite\_Ordered\_Maps: task-safe ordered maps with immutable mapping

- Cron: a simple low-precision service of periodic events

- File\_Streams: wrapper around Stream\_IO files implementing stream interface

- Getopt\_Long: command-line argument processing similar to C getopt\_long

- GNAT\_HMAC: instances of HMAC using GNAT hash primitives

- HMAC: generic HMAC implementation using a formal hash function

- Indefinite\_Holders: simple Ada 2005 implementation of the Ada 2012 container

- References: generic simple referencecounter implementation

o Pools: task-safe pool of referencesjj

- S-expressions: library for dealing with S-expressions

o Atom\_Buffers: dynamic buffer for Sexpression atoms

o Atom Ref Constructors: helper constructors for atom references

o Atom\_Refs: common referencecounted atoms

o Conditionals: S-expression boolean expressions about some object

+ Generic\_Evaluate: Generic boolean expression evaluation framework

+ Strings: Boolean expressions on standard strings

o Dynamic\_Interpreters: S-expression interpreter with mutable commands and callbacks

o Encodings: translators to and from official S-expression encodings

o Enumeration\_IO: tools to help I/O of enumerations in S-expressions

o File\_Readers: objects reading a file to an atom or a S-expression

o File\_Writers: file-backed S-expression printer

o Generic\_Caches: memory container for S-expressions

o Interpeter\_Loop: inner loop of Sexpression interpreters, typically used in static interpreters

o Interpreters: callback-based Sexpressions interpreter

o Lockable: interface for S-expressions descriptors that can be temporarily restricted to a given nesting level

o Parsers: S-expression descriptor from a byte stream

o Printers: interface for objects to which S-expressions are written

+ Pretty: human-friendly S-expression pretty printer

+ Config: serialization and deserialization of pretty printer parameters to and from S-expressions

o Replayable: interface for S-expression descriptors whose state can be stored and replayed

o Special\_Descriptors: always-empty and always-in-error descriptors

o Templates: S-expression template renderers

+ Dates: rendering of Ada.Calendar.Time values

+ Generic Discrete Render: rendering of enumeration values

+ Generic\_Integers: rendering of integer values

+ Integers: instance of Generic\_Integers for standard integers

- Static\_Hash\_Maps: code generator around GNAT Perfect\_Hash\_Generators to build a static hash map

- o S\_Expressions: read S-expression description of static hash map

- Storage\_Pools: helper objects with dynamic memory management

- String\_Slices: objects hold slices of reference-counted shared strings

- o Slice\_Sets: sets of aforementioned slices

- Tests: very simple test framework

- o Text\_IO: test output using standard Ada.Text\_IO

- Time\_IO: conversions between time values and strings

- o Human: human-readable fuzzy formats

- o RFC\_3339: time format described by RFC-3339

- Time\_Keys: short printable string serialization of time that is consistent with lexicographical order

- Time\_Statistics: accumulator for (run)time statistics

- o Coarse\_Timers: instance of Generic\_Timers with standard calendar time

- o Fine\_Timers: instance of Generic\_Timers using real-time annex

- o Generic\_Timers: timer objects to provide data to accumulators

## AdaControl

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Thu, 3 Nov 2016 16:36:05 +0100 Subject: [Ann] AdaControl 1.18r8 released Newsgroups: comp.lang.ada

A new version of AdaControl has been released at the usual place:

http://www.adalog.fr/en/adacontrol.html

The count goes up to 68 rules and 532 subrules!

Most awaited, AdaControl accepts now directly .gpr files, and the executable versions use GNAT-GPL-2016.

See the file HISTORY for a detailed list of new features.

#### Enjoy!

[See also "AdaControl", AUJ 36-1, p. 13. —sparre]

From: John Marino

<dragonlace.cla@marino.st> Date: Tue, 8 Nov 2016 07:56:49 -0800 Subject: Re: [Ann] AdaControl 1.18r8 released

Newsgroups: comp.lang.ada

#### >[...]

Can you confirm that gnatcoll is a now a build requirement for AdaControl?

Gnatcoll has a ton of dependencies, most of the them likely unused by AdaControl. It will be quite unfortunately if the dependency tree of AdaControl has exploded since version 17.

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Tue, 8 Nov 2016 17:55:45 +0100 Subject: Re: [Ann] AdaControl 1.18r8 released

Newsgroups: comp.lang.ada

#### >[...]

Gnatcoll is only needed for Gnatcoll. projects (which needs gnatcoll.vfs). How do you think AdaControl is able to process project files now ;-) ?

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Thu, 10 Nov 2016 12:40:59 +0100 Subject: [Ann] AdaControl 1.18r9 released Newsgroups: comp.lang.ada

#### [...]

This is a very minor release, just a small rearrangement of the sources to make it easier to compile AdaControl without Gnatcoll (but of course, you lose support of .gpr projects).

There is no change in functionality, so if you are happy with gnatcoll, there is no need to download this version.

Enjoy!

## **GPRBuild - A Discussion**

From: Olivier Henley <olivier.henley@gmail.com> Date: Thu, 3 Nov 2016 08:32:21 -0700 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

Dmitry A. Kazakov wrote:

> BTW, gprbuild can C. Granted, gprbuild is a big step back from gnatmake, but still miles ahead of make.

Why do say gprbuild is a big step back from gnatmake? I don't have enough knowledge of both to evaluate your saying.

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Thu, 3 Nov 2016 17:10:46 +0100 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

#### > [...]

Because in my opinion it is built upon an inferior technology. It uses XML, it is not self-contained (has a mess of semi-hidden supplementary files spread all around the system). It is very easy and common to have gprbuild not working where gnatmake never had any problem. The biggest danger is turning it into yet another "configure" / CMake. From: Simon Wright

<simon@pushface.org> Date: Thu, 03 Nov 2016 17:50:46 +0000 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

> [...]

Unless you go out of your way, the configuration files are all under \$prefix/share/gprconfig/

When things work, all is fine. When they don't, it can be tricky; the way the configuration files specify commands to run and grepping the output for particular patterns is challenging:

On the Mac, GCC 5 and 6 generate shared libraries with names like libgnat-6.dylib; GCC 4, names like libgnat-4.8.dylib. gnatls reports itself as e.g. GNATLS 6.1.0. The original share/gprconfig/compilers.xml file looked for the first 2 fields of the version:

for the first 2 fields of the version; libgnat-6.1.dylib wasn't found. The fix was (cut back not to bore you):

#### <version>

<external>\${PREFIX}gnatls -v --version</external>

- <grep regexp="^GNATLS.+?(\d+(\.\d+)?)" group="1"></grep>

- + <grep regexp="^GNATLS.+?(\d+)" group="1"></grep>

</version>I'm very pleased that, since GPRBUILD 2016, I can use e.g.

for Target use "arm-eabi"; for Runtime ("ada") use "ravenscar-sfp-stm32f4";

in the GPR instead of having to specify on the command line.

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Fri, 4 Nov 2016 17:08:49 +0100 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

>[...]

You misunderstood the discussion. It was not GPR I complained about.

GPR is a language that describes an object language(s) project. I have little against it. At least it is has Ada-like syntax.

The discussion was about another language that would describe rules how to interpret a GPR file when it refers to some object language X (e.g. Ada or C). Roughly it is the language gprconfig uses.

My point was that this knowledge better be an integral part of gprbuild as it was of gnatmake. Georg suggested that somebody outside AdaCore could interested in keeping it elsewhere as grpbuild attempts to do.

[...]

### Ada and Operating Systems

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Fri, 4 Nov 2016 09:37:25 -0700 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

> [...]

Every Ada compiler includes a tool for building a system based on the dependency information in the code.

This information is one of Ada's major strengths. One has to learn the parameters to this tool, of course, but then building becomes one line, easily stored somewhere, such as a script.

So what does a program such as gprbuild buy you? You have to tell gnatmake where to find other things used in the system (-A\*), but you do the same with gprbuild, in the form of paths in the withed projects. You have to supply the compiler switches, but you do the same with gprbuild, in the Switches declarations. You don't have to write the one-line script, but instead write a manyline project file.

Personally, I don't see that gprbuild adds any value; in fact, it seems to subtract value: You supply the same information and have to have the same knowledge, but you have to know the syntax of a project file as well, so the effort is increased. For this reason, I never voluntarily use gprbuild for my projects (which are always all Ada), and don't understand why anyone would think it an advantage to do so.

(Similar arguments apply against make.)

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Mon, 07 Nov 2016 09:39:15 +0100

Subject: Re: Building Matreshka on Windows Newsgroups: comp.lang.ada

Jeffrey R. Carter wrote:

[about all Ada projects]

> [...], easily stored somewhere, such as a script.

Yes. But don't you need to have two versions of that script, one for Microsoft hosted compilers, and one for Unix hosted compilers? Using GNAT project files, you can typically get away with having only one.

> So what does a program such as gprbuild buy you?

If your projects only contain Ada sources - nothing that "gnatmake" didn't have as well.

Since I typically work on multi-language projects (Ada, Mercurial/Subversion, Macks, C), "gprbuild" makes a big difference for me.

But I'm not at all fond of "gprconfig". I'm in the middle of figuring out how I can avoid "gprconfig", and provide ready to use ".cgpr" files instead of providing XML files for "gprconfig", which have to be installed before the project can be built.

From: Simon Wright <simon@pushface.org> Date: Mon, 07 Nov 2016 08:50:35 +0000 Subject: Re: Building Matreshka on Windows

Newsgroups: comp.lang.ada

> [...] instead of providing XML files for "gprconfig", which have to be installed before the project can be built.

They don't have to be "installed", at any rate not in the default location. gprbuild has a --db switch:

- --db dir Parse dir as an additional knowledge base

- --db- Do not load the standard knowledge base

## Deepend

From: Brad Moore

<bmoore.ada@gmail.com>

Date: Sun Nov 6 2016

Subject: Deepend URL: https://sourceforge.net/projects/ deepend/

Deepend is a storage pool with subpool capabilities for Ada 2005.

[...]

Released /deepend-3.5.tgz [See also "Deepend", AUJ 35-4, p. 217. —sparre]

## Ada and Operating Systems

## **Linux: Joystick API**

From: Artium Nihamkin <artium@nihamkin.com> Date: Mon, 3 Oct 2016 08:54:15 -0700 Subject: ANN: Thick bindings for the Linux joystick API Newsgroups: comp.lang.ada

Thick bindings for the Linux joystick API are available at: https://github.com/alkhimey/

Ada\_Joystick

The highlight are typed axes/buttons:

#### type

Logiteck\_Extreme\_3D\_Pro\_Axis\_Type is

(STICK\_X, STICK\_Y, STICK\_Z, THROTTLE, HAT\_X, HAT\_Y);

type

Logiteck\_Extreme\_3D\_Pro\_Button\_Type is

(BUTTON\_01, BUTTON\_02, BUTTON\_03, BUTTON\_04, BUTTON\_05, BUTTON\_06, BUTTON\_07, BUTTON\_08, BUTTON\_09, BUTTON\_10, BUTTON\_11, BUTTON\_12); package L3D is new Linux\_Joystick

(Button\_Type =>

Logiteck\_Extreme\_3D\_Pro\_Button\_Type, Axis\_Type =>

Logiteck\_Extreme\_3D\_Pro\_Axis\_Type);

I wrote this as an exercise, no specific use cases in mind.

If you are developing graphic application, the framework you use (GLUT, GLFW etc.) might already have joystick input functionality that is cross platform.

## Mac OS X: XNAdaLib

From: Pascal Pignard <p.p11@orange.fr> Date: Mon, 10 Oct 2016 12:37:40 -0700 Subject: [ANN] XNAdaLib 2016 binaries. Newsgroups: comp.lang.ada

This is XNAdaLib 2016 built on Mac OS 10.11 (El Capitan) for Native Quartz including:

- GTKAda GPL 2016 with GTK+ 3.20.3 complete,

- Glade 3.18.3,

- GnatColl GPL 2016,

- Florist GPL 2016,

- AdaCurses 20110404,

- Gate 3-05-b,

- Components 4.15,

- AICWL 3.15,

- Zanyblue 1.3.0b, (new)

- PragmARC 07-2016-09, (new)

- GNOGA 1.2-beta,

- AdaControl 1.18b4, (new)

- AdaDep 1.3r3 (new)

- and as side libraries:

- Template Parser,

- gtksourceview 3.14.3,

- GNUTLS 3.3.12, (new)

- ASIS GPL 2016. (new)

XNAdaLib binaries have been post on Source Forge:

https://sourceforge.net/projects/gnuada/fil es/GNAT\_GPL%20Mac%20OS%20X/20 16-el-capitan/

Feel free to send comments.

From: Pascal Pignard <p.p11@orange.fr> Date: Tue, 11 Oct 2016 12:16:34 -0700 Subject: Re: [ANN] XNAdaLib 2016 binaries.

Newsgroups: comp.lang.ada

>[...]

XNAdaLib stands for extended native Ada libraries prebuilt for Mac OS.

When AdaCore set up the libre site with GPL binaries for various platforms, GTKAda was not (and is still not) shipped for Mac OS.

So I built GTKAda from source for macOS. GTKAda is based on

GTK+.Building GTK+ is long, needs lot of patches and many times I need help, so I provide the result to the community.

The library is becoming richer from year to year with AdaCore's GNATColl, Florist and many others from various contributors.

The library needs only GNAT GPL installed on macOS.

I haven't not so much feedbacks if it helps but I hope so.

[See also "Mac OS X: XNAdaLib", AUJ 37-3, p. 128. —sparre]

## Linux: Writing Kernel Modules

From: Artium Nihamkin

<artium@nihamkin.com> Date: Sun, 23 Oct 2016 06:49:14 -0700 Subject: Writing Linux Kernel Modules in Ada

Newsgroups: comp.lang.ada

I am experimenting with writing Linux kernel modules in Ada and document my attempts.

Thought some here would be interested to read about this:

http://www.nihamkin.com/2016/11/23/ writing-linux-modules-in-ada-part-1/

https://github.com/alkhimey/ Ada\_Kernel\_Module\_Toolkit

Any kind of criticism is welcomed.

From: Artium Nihamkin <artium@nihamkin.com> Date: Sat, 5 Nov 2016 15:31:01 -0700 Subject: Re: Writing Linux Kernel Modules

in Ada Newsgroups: comp.lang.ada

[...]

Part 2, incorporating the secondary stack into the run time.

http://www.nihamkin.com/2016/11/05/ writing-linux-modules-in-ada-part-2/

From: Simon Wright

<simon@pushface.org> Date: Sun, 06 Nov 2016 09:39:58 +0000 Subject: Re: Writing Linux Kernel Modules in Ada

Newsgroups: comp.lang.ada

> [...]

Interesting!

What about elaboration? Have you considered the restriction No\_Elaboration\_Code? (would it help?)

## Mac OS X: AdaSubst and AdaDep

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Tue, 25 Oct 2016 14:06:19 +0200 Subject: Adasubst and Adadep for macOS Newsgroups: comp.lang.ada Thanks to Pascal Pignard, a Mac OS X distribution of AdaSubst and AdaDep is available from Adalog's components page:

http://adalog.fr/en/components.html

AdaControl? will be with the next release, (hopefully) coming soon.

[See also "AdaSubst and AdaDep", earlier in this issue. —sparre]

## Windows: Compilers

From: jack <anon@example.com> Date: Thu, 10 Nov 2016 12:50:40 -0000 Subject: Ada wanted for win7 Newsgroups: comp.lang.ada

Is there a free ada environment I can download to use on a win7-64 system?

If not I'd welcome suggestions for a low cost version.

Purpose is to learn/and evaluate Ada basics.

From: Georg Bauhaus <bauhaus@futureapps.de> Date: Thu, 10 Nov 2016 14:30:21 +0100 Subject: Re: Ada wanted for win7

Newsgroups: comp.lang.ada

> [...]

- http://www.getadanow.com/

- http://libre.adacore.com/

- http://www.adaic.org/

- http://www.rrsoftware.com/

GNAT (FSF or GPL), ObjectAda, and Janus/Ada 95 are lowest cost, TTBOMK.

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Thu, 10 Nov 2016 10:50:24 -0700 Subject: Re: Ada wanted for win7 Newsgroups: comp.lang.ada

[...]

Not addressed by others is the version of Ada you'd like to learn/evaluate. The most recent version, ISO/IEC 8652:2012, is only supported by one compiler, GNAT. Free versions of GNAT are available. GNAT also supports earlier versions of Ada.

If you want a language supported by multiple compilers you'll need to use an earlier version of Ada. The next most recent version, ISO/IEC 8652:2007, is supported by multiple vendors, but GNAT is the only free compiler that supports it.

The version of Ada before ISO/IEC 8652:2007 is ISO/IEC 8652:1995 (Ada 95), which is supported by multiple vendors. There is a free version of ObjectAda for Ada 95 that can be found on line. It has limitations as to the size of programs that it can compile, but they should not be an issue for your purposes. RR Software provides a low-cost compiler and may provide a free evaluation compiler for Ada 95.

## Fedora: AVR-Ada

From: Tero Koskinen <tero.koskinen@iki.fi> Date: Fri, 11 Nov 2016 18:35:44 +0200 Subject: AVR-Ada 1.2.2 binary rpm for Fedora 25

Newsgroups: comp.lang.ada

I created AVR-Ada 1.2.2[1] rpm for Fedora 25 (x86\_64).

You can get it from my fedora.adalanguage.com server, by creating a new /etc/yum.repos.d/fedora-adalanguage.repo with following contents:

[fedora-adalanguage]

name=Tero's Fedora RPM repository for Ada packages

baseurl=http://fedora.adalanguage.com/repo/\$releasever/\$basearch

enabled=1

You can install the rpm with command:

sudo dnf install avr-ada --nogpgcheck

The rpm package is completely unofficial (not endorsed by Fedora or AVR-Ada projects), but since creating it isn't that easy, I every now and then try to provide new version.

The binaries are installed to /opt/avr-avr-122 and are usable out of the boxFor example, try:

export PATH=/opt/avr-avr-122/bin:\$PATH hg clone

https://bitbucket.org/tkoskine/arduino-blog cd arduino-blog/examples/hello-uart

make

After "make", you will have hello.hex in the current directory and you can upload it to Arduino with avrdude (not part of the package):

sudo avrdude -c arduino -p atmega328p -P /dev/ttyACM0 \

-b 115200 -U flash:w:hello.hex

PS. Fedora 25 is not yet released, I used beta version.

[1] Well, actually the latest git version, but it is almost same.

## References to Publications

## Ada in Coreboot

From: Jean-Pierre Rosen

<rosen@adalog.fr> Date: Mon, 19 Sep 2016 16:36:56 +0200 Subject: Ada supported in Coreboot Newsgroups: comp.lang.ada

And as "first class citizen"!

http://www.phoronix.com/scan.php? page=news\_item&px= Ada-Coreboot-First-Class From: onox <denkpadje@gmail.com> Date: Wed, 28 Sep 2016 06:43:24 -0700 Subject: Re: Ada supported in Coreboot Newsgroups: comp.lang.ada

#### > [...]

Nice to see Ada being added to coreboot. AFAIK the Google Chromebooks use coreboot. Much leaner than Intel's UEFI, which is slow and unreliable (personal experience) IMO.

In the coreboot mailing list message that actually mention they are using SPARK. Not clear though whether that is SPARK 2014 or an older version.

From: Adrian-Ken Rueegsegger <ken@codelabs.ch> Date: Thu, 29 Sep 2016 13:16:08 +0200 Subject: Re: Ada supported in Coreboot Newsgroups: comp.lang.ada

>[...]

Its SPARK 2014, see e.g. the Intel graphics initialization code at [1].

[1] - https://review.coreboot.org/#/c/ 11869/

## Ada Inside

## Failure of the Schiaparelli Lander

From: Peter C. Chapin <PChapin@vtc.vsc.edu> Date: Sat, 29 Oct 2016 09:45:13 -0700 Subject: Failure of the Schiaparelli lander: A software problem?

Newsgroups: comp.lang.ada

While not specifically Ada related, this is a topic that might be of interest to many in this group. As you may know the Schiaparelli Mars lander recently crashed to the surface of Mars instead of landing softly as intended. The article here provides some details:

http://www.skyandtelescope.com/ astronomy-blogs/

schiaparelli-requiem-for-a-mars-lander/

According to the article the spacecraft jettisoned its heat shield and parachute early and then, even worse, turned off the descent engines while the spacecraft was still over a mile from the ground. The article says,

"... a computer glitch seems to have confused the lander, as miscommunication between its onboard navigational system and radar erroneously told Schiaparelli it was near the surface."

I'm not sure what "computer glitch" means, exactly, but this sounds like a software failure of some kind. Does anyone here have access to more information about this? Was this a software failure? If so, what was the nature of the failure, and was it something the use of Ada (or SPARK) might have avoided? I realize the ESA is still analyzing the telemetry from the lander so perhaps more details will come to light in time.

#### From: Dirk Craeynest

<dirk@cs.kuleuven.be> Date: Sun, 30 Oct 2016 07:19:27 -0000 Subject: Re: Failure of the Schiaparelli lander: A software problem? Newsgroups: comp.lang.ada

#### >[...]

FYI, in a press release [1] earlier this year, AdaCore wrote:

"Thales Alenia Space implemented in Ada two ExoMars On-Board Software (OBSW) components: one for the Trace Gas Orbiter (TGO) on an ERC32 target, and one for the Entry, Descent and Landing Demonstrator Module (EDM) on a LEON2 target."

So there already was (at least some) Ada software on the Schiaparelli lander. The above quote seems to suggest that all software on the lander was in Ada, as the latter is named as one of the two components implemented in Ada...

Maybe someone from AdaCore or Thales on CLA can tell us more?

[1] http://www.adacore.com/press/ ada-on-board-gnat-pro-helps-exomarsget-to-the-red-planet/

#### From: Dirk Craeynest

<dirk@cs.kuleuven.be> Date: Mon, 31 Oct 2016 06:48:04 -0000 Subject: Re: Failure of the Schiaparelli lander: A software problem? Newsgroups: comp.lang.ada

> What is a "Demonstrator Module"? It is in actual control? I guess we'll have to wait.

The "Entry, Descent and Landing Demonstrator Module (EDM)" is the technical name for what is also known as the Schiaparelli lander.

<http://exploration.esa.int/mars/ 47852-entry-descent-and-landingdemonstrator-module/>

[See also "ExoMars", AUJ 37-3, p. 130. —sparre]

## AZip - A Portable Zip Archive Manager

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Tue, 1 Nov 2016 02:45:43 -0700 Subject: Ann: AZip v.2.0 Newsgroups: comp.lang.ada

The version 2.0 of AZip is out!

URL: http://azip.sf.net/

AZip is a Zip archive manager. The latest addition is an archive

recompression tool. Some features:

- Flat view / Tree view

- Multi-document (should be familiar to MS Office users)

- Simple to use (at least I hope so ;-) )

- Useful tools:

o Text search function through an archive, without having to extract files

- o Archive updater

- o Integrity check

o Archive recompression (new), using an algorithm-picking approach for improving a zip archive's compression.

- Encryption

- Methods supported: Reduce, Shrink, Implode, Deflate, Deflate64, BZip2, LZMA

- Free, open-source

- Portable (no installation needed, no DLL, no configuration file)

- "Under the hood" features:

- AZip is from A to Z in Ada :-)

- Uses the highly portable Zip-Ada library

- Portability to various platforms: currently it's fully implemented with GWindows (for Windows), and there is a GtkAda draft, but anyway the key parts of the UI and user persistence are generic, platform-independent

[See also "AZip - A portable Zip Archive Manager", AUJ 36-2, p. 69. —sparre]

## AdaChess

From: Alessandro Iavicoli

- Date: Tue Nov 8 2016

- Subject: AdaChess is growing up: more Ada and more chess

- URL: http://www.adachess.com/engine/ adachess-is-growing-up-more-ada-andmore-chess.html

The upcoming AdaChess version is a really nice improvement of the previous one. AdaChess comes with some big new features both in terms of chess playing style/strength and in the Ada source code. As everybody knows, AdaChess had (has?) only two serious weakness: the speed and the search depth. Both of them has been greatly improved. Let's see what's new in the last release!

## The engine

Compared to the last version, AdaChess is surely stronger. I will tell you soon how much it is! Those are the main changes in the engine.

#### The move generator

In the previous version, the generator had some bottlenecks. First of all, it played all the moves to check for legality, even moves that clearly could not leave king in check. The new generator has been designed to avoid those bottlenecks. How? AdaChess move generator try to minimize the test for legality while generating moves. It does that by looking first if the moving piece is absolutely pinned – in this case it just moves along the line that the piece can move. On a second pass, it generate check evasion if the king is in check.

Compared to the v2.1 GSEI version, the move generator speed is 3x faster.

#### The search

Another important improvement is the principal variation search. The alpha-beta is still the main searching algorithm, but now there are two helper search functions: the zero-window search and the late move reduction search.

Both of them decrease the number of nodes to be searched after the "best" moves are found. Together with the more accurate score assigned to moves (to be sorted and played first) the search goes at lease 1-2 ply deeper than the v2.1 version.

Another important improvement is the use of a SEE in quiescence to avoid the engine searching for bad capture and waste time.

#### The hash tables

Yes! Finally I developed the hash tables for AdaChess. Thanks to the transposition tables, the engine save lot of time while searching the same positions twice or more. Currently, the hash tables works well on endgames and for recaptures where the engine saves the previous search and reuse those data.

#### The evaluation

In my honest opinion, the static evaluation wasn't so bad in the 2.1 version. The only notable lack was in king defence. So, there is where I improved the evaluation by looking for attacking to the king zone and trophism.

AdaChess now full understand if each side has castled and can detect leaks in castle structure. Also, AdaChess recognize attacks to the opponent king and defends according to the weight of the attack.

#### Other stuffs

AdaChess has many other minor changes:

Recognize if a moves checks the opponent king and it recognize what kind of check it is;

New input/output notation. AdaChess recognize and works with your favourite notation:

Winboard/UCI: c5d6, e1g1, d7d8q,

SAN: Bf5, Nb6+, O-O, Qxf8#, ...

Long Algebraic: Nf1-g3, Rh1xd1, ...

You can switch between notation by starting the engine and passing the notation as parameter with

#### adachess -n

. . .

<winboard|uci|san|long\_algebraic>

Please note that AdaChess does not communicate by using UCI protocol. It still needs Winboard protocol.

However, AdaChess recognize all of those notations as input so if you want to build your own book just build it as you want and call it adachess.book!

Source code: more Ada and less chess

When I started to develop AdaChess I had two things in mind: making a nice chess engine in Ada. Wait, I said two things, which one is the other? Yes: making a nice chess engine and make it in Ada. It is the same sentence, one from the chess point of view and one from the Ada coding point of view. From the chess point of view it means making the engine stronger and faster. From the Ada point of view it means write code that is readable and as much idiomatic as possible.

The new code is very much Ada idiomatic and it is well commented so everybody who wants to read it can find full explanations on data structures, procedures as well as any other thing inside AdaChess. I believe that this release is very much Ada-like and I'm sure you will find the code interesting and nothing to complain about!

You can download the latest release from the download page!

AdaChess is a GPL software so feel free to use and redistribute it under the terms of the GNU Public License. If you find any bug or if you thing that can be improved in some way please contact me!

#### Have fun and enjoy!

[See also "AdaChess", AUJ 34-1, p. 17. —sparre]

## Ada in Context

## An Obscure Arithmetic Run-Time Error

From: Yannick Moy

- Date: Thu Sep 22 2016 Subject: SPARK 2014: The Most Obscure Arithmetic Run-Time Error Contest

- URL: http://www.spark-2014.org/entries/ detail/the-most-obscure-arithmetic-runtime-error-contest

Let's start with the typical examples of overflows and division by zero:

#### $\mathbf{Z} := \mathbf{X} + \mathbf{Y};$

$\mathbf{Z} := \mathbf{X} / \mathbf{Y};$

Here, X, Y and Z might be integers, fixed-point numbers or floating-point numbers. If X and Y are too big, X + Ywon't fit into a machine integer or floating-point, hence the overflow error. If Y is zero, X / Y has no meaningful value, hence the division by zero error. Let's look now at a more exotic overflow, which happens when you negate a signed integer:

Z := -X;

In the specific case where X is the minimal machine integer of this size (say, -2147483648 for a 32 bits signed integer), negating it results in a value that's one more than the maximal integer of that size (2147483647 for a 32 bits signed integer). This is because machine signed integers are asymmetric: there is one more negative value than there are positive values.

This error is rather common, because it is such a special case, so programmers tend to overlook it. Take for example the original C code of the Crazyflie small drone that we translated into SPARK. They discovered the bug after debugging a scenario that causes the drone to spin uncontrollably.

The same reason explains why there might be an overflow on absolute value operation:

Z := abs X; Indeed, if X is -2147483648 here, its absolute value would be 2147483648 which is more than the maximal 32 bits machine integer.

There is an even more obscure overflow, which happens when you divide integers:

$\mathbf{Z} := \mathbf{X} / \mathbf{Y};$

In the specific case where X is again the minimal machine integer of this size (-2147483648 for a 32 bits signed integer), and Y is -1, dividing X by Y is the same as negating X, so we are back to the previous run-time error.

Now, let's open the curtain on the most obscure arithmetic run-time error: the possibility that an exponentiation on a floating-point value results in a division by zero. Yes, you may have values for X and N such that  $X^{**N}$  results in a division by zero. How? Take X=0.0 and N=-1. The Ada standard says that  $X^{**N}$  in that case is the same as  $1/(X^{**}(-N))$ ... but X is zero, so  $X^{**}(-N)$  is zero, so... yes, we have a division by zero. Amazing!

Well, it turned out that this was also a surprise for the SPARK developers. We did not know this rule of Ada, so we did not implement the check that detects this case in SPARK. This is now fixed thanks to Rod Chapman who noticed that. At this point, you should wonder how one can ever make sure to get rid of all run-time errors in her code? Are coding standard, reviews and testing going to detect all possible problems? I don't believe so. I believe that the only way to detect all possible such cases is to use a static analysis tool like SPARK. If we were able to miss one case, while we earn a living for focusing on such checking, no amount of attention and cleverness is going to make a developer catch all such cases in a real life application.

## Introducing Static Analysis to Legacy Projects

From: Artium Nihamkin <artium@nihamkin.com> Date: Sat, 5 Nov 2016 03:28:20 -0700 Subject: Re: [Ann] AdaControl 1.18r8 released Newsgroups: comp.lang.ada

[...]

I would like to raise an issue with static analysis tools, style checkers and similar tools that is particularly valid for tools aiming at Ada projects.

Sometimes a developer decides to try these tools on an already existing codebase. This will lead to thousands of violations.

Fixing them is not acceptable in a field tested code.

The developer would like to know only about the violations in the newly added code.

Allowing this requires integration with source control tools and the ability to parse the analysis tool's log in a smart way (for example adding a line of code in the beginning of the file, will cause all the lines of the violations to increase by one)

It is interesting to hear your thoughts about this, and if you are aware of any solutions used by AdaControl users.

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Sat, 5 Nov 2016 13:44:51 +0100 Subject: Re: [Ann] AdaControl 1.18r8 released

Newsgroups: comp.lang.ada

> [...]

A semantic tool, especially one using ASIS like AdaControl, can work only on

compilable compilation units. OTOH, you can apply AdaControl to selected units, not necessarily a whole project.

My opinion is that if you modify a unit, then it's a good opportunity to fix any violation to coding rules. So my recommendation would be to include AdaControl in the process of entering a modified unit into the SCM.

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Mon, 07 Nov 2016 09:02:13 +0100 Subject: Re: [Ann] AdaControl 1.18r8 released

Newsgroups: comp.lang.ada

[...]

> Fixing them is not acceptable in a field tested code.

A reasonable view. - As Jean-Pierre indicates; once you touch a component, it may be time to fix observed problems in it.

We're fixing violations in field-tested components, where we estimate that it is plain luck that we haven't registered a failure due to the violation.

Cost is another argument for not fixing all violations immediately.

> The developer would like to know only about the violations in the newly added code.

Just like with compiler warnings. But how can you easily keep track? You could of course simply count the number of violations of each kind, and make sure the numbers aren't growing. How would you integrate that in a version control system? (It requires that you log analysis results for every commit, and I haven't found a nice way to do that in any of the version control systems I have used so far.) Jean-Pierre's suggestion (to fix a file when you touch it) is tempting - until you have to change 2 lines in a 5000 line source file (with ~5000 violations). Then you quickly redefine "component" to something smaller than the whole source file - and live with not having automated checking of the rule.

From: Markus Schöpflin Date: Mon, 7 Nov 2016 10:03:21 +0100 Subject: Re: [Ann] AdaControl 1.18r8 released

Newsgroups: comp.lang.ada

>[...]

> The developer would like to know only about the violations in the newly added code.

For a similar issue (huge legacy code base with thousands of compiler warnings) we have simply created a script which checks the output of the build against a known reference build, and then complains if the new build contains warnings not found in the reference build.

The script basically uses the following algorithm:

- For both logs, extract all warnings and remove all line number references. This results in two temporary files.

- Sort each temporary file and diff the resulting two files.

- Output all warnings found in the second file but not in the first.

After each release the reference build log is then updated.

Over the course of about five years, this has helped us to bring the warning count down from about 4000 to about 300, and to get the most critical components free of warnings.

## Tools to get you there. Safely.

Ada and The GNAT Pro High-Integrity Family

AdaCore

www.adacore.com

## Conference Calendar

## Dirk Craeynest

KU Leuven. Email: Dirk.Craeynest@cs.kuleuven.be

This is a list of European and large, worldwide events that may be of interest to the Ada community. Further information on items marked  $\blacklozenge$  is available in the Forthcoming Events section of the Journal. Items in larger font denote events with specific Ada focus. Items marked with O denote events with close relation to Ada.

The information in this section is extracted from the on-line *Conferences and events for the international Ada community* at: http://www.cs.kuleuven.be/~dirk/ada-belgium/events/list.html on the Ada-Belgium Web site. These pages contain full announcements, calls for papers, calls for participation, programs, URLs, etc. and are updated regularly.

## 2017

- January 12-14 18th IEEE International Symposium on High Assurance Systems Engineering (HASE'2017), Singapore. Topics include: model-driven engineering, design languages, formal methods, domain specific languages, evolution and change, verification and validation, security and privacy, reliability and safety, tools for high assurance systems, etc. Systems of interest include: cyber-physical systems, distributed systems, embedded systems, autonomous vehicles, robot swarms, etc.

- January 15-17 18th International Conference on Verification, Model Checking, and Abstract Interpretation (VMCAI'2017), Paris, France. Topics include: program verification, model checking, abstract interpretation, static analysis, type systems, program certification, hybrid and cyber-physical systems, etc.

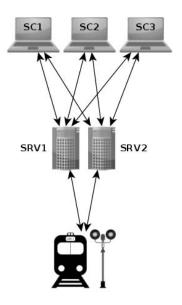

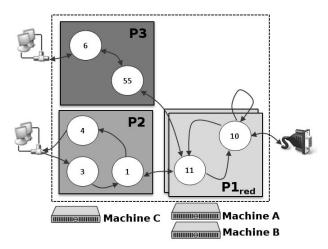

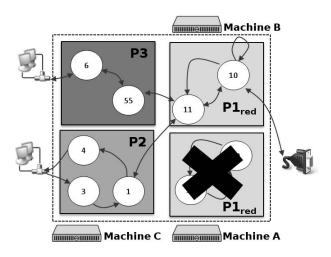

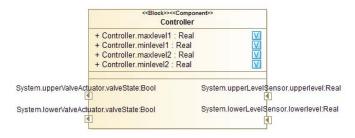

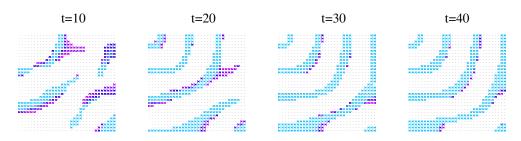

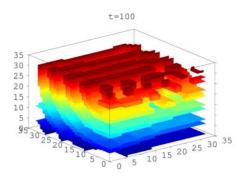

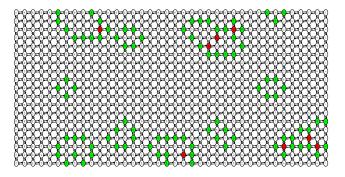

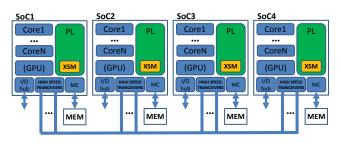

- © January 15-21 44th ACM SIGPLAN **Symposium on Principles of Programming Languages** (POPL'2017), Paris, France. Topics include: all aspects of programming languages and programming systems.