# ADA USER JOURNAL

# Volume 38 Number 1 March 2017

### Contents

|                                                                                                                                      | Page              |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                | 2                 |

| Editorial                                                                                                                            | 3                 |

| Quarterly News Digest                                                                                                                | 4                 |

| Conference Calendar                                                                                                                  | 25                |

| Forthcoming Events                                                                                                                   | 31                |

| Special Contribution                                                                                                                 |                   |

| J. Cousins<br>"ARG Work in Progress"                                                                                                 | 33                |

| Article                                                                                                                              |                   |

| B. Wang, H. Gao and J. Cheng<br>"Definition-Use Net and System Dependence Net Generators for Ada 2012 Program<br>their Applications" | ns and<br>37      |

| SPARK 2014 Rationale: Type Predicates, Variables that are Constant, Support for Ray<br>Support for Type Invariants                   | venscar and       |

| Y. Moy and C. Dross                                                                                                                  | 57                |

| Ada-Europe Associate Members (National Ada Organizations)                                                                            | 64                |

| Ada-Europe Sponsors                                                                                                                  | Inside Back Cover |

# Editorial Policy for Ada User Journal

### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

### Submission Guidelines

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

One year ago, in the editorial for the March issue of 2016, I pointed out to the readers the, at that time, recent update to the Ada 2012 standard. That issue of the journal included a special contribution which briefly described the main changes, clarifications and corrections in that update. Nevertheless, the work on the language never stops, and it is intention of the Ada User Journal to keep readers aware of the standardisation process, what is being considered and pipelined for future evolution.

We are therefore very happy to be able to publish in this issue a paper on the work in progress in the Ada Rapporteur Group (ARG), the WG9 group responsible for the language interpretation and evolution, written by the Chair of the ARG, Jeff Cousins, from BAE Systems Surface Ships Limited, UK. This paper provides information on the Ada Issues which have been already addressed and approved this past year, but also some information on the work in the pipeline. An interesting read for sure.

Continuing with the technical contributions, the issue then provides an extensive technical work from a group of authors of the Saitama University, Japan, updating previous work on definition-use and system dependence net graphs to consider new features of Ada 2012. Finally, a set of contributions from the SPARK 2014 Rationale, by Yannick Moy and Claire Dross, of AdaCore, France.

As usual, the reader will find the valuable information of the News and Calendar sections, contributed by Jacob Sparre Andersen and Dirk Craeynest, their respective editors. I would also like to draw your attention to the Ada-Europe 2017 conference, which, apart from the rich content of tutorials, exhibition and scientific and technical presentations will also provide a very rich networking environment. A particular highlight this year is the panel discussion on "The Future of Safety-Minded Languages" – which will feature interesting and potential controversial discussions. I hope to see you there!

Luís Miguel Pinho Porto March 2017 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

### Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

### Contents

| Ada Inside 11<br>Ada in Context 14 | Ada-related Events<br>Ada-related Tools<br>Ada-related Products<br>Ada and Operating Systems<br>References to Publications | 4<br>4<br>7<br>8<br>9 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                    |                                                                                                                            |                       |

### Ada-related Events

[To give an idea about the many Adarelated events organised by local groups, some information is included here. If you are organising such an event feel free to inform us as soon as possible. If you attended one please consider writing a small report for the Ada User Journal. —sparre]

### "Make with Ada" Winners

From: Olivier Henley

<olivier.henley@gmail.com> Date: Fri, 2 Dec 2016 06:55:23 -0800 Subject: Make with Ada winners Newsgroups: comp.lang.ada

I don't know when results became public [...] but the winners of the Make with Ada are here:

http://www.makewithada.org/

The winning project, by Stephane Carrez, looks really impressive and it looks like it is here:

https://github.com/stcarrez/etherscope

Anyways, congrats to everyone, IMO that initiative is great and I will kick myself to participate next time.

[See also ""Make with Ada" Programming Competition", AUJ 37-2, p. 69. —sparre]

### Ada-Europe 2017 in Vienna

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Thu, 19 Jan 2017 21:47:34 -0000 Subject: FINAL CfP Ada-Europe 2017, Sun 22 Jan submission deadline Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

FINAL Call for Papers

22nd International Conference on Reliable Software Technologies - Ada-Europe 2017

12-16 June 2017, Vienna, Austria

http://www.ada-europe.org/ conference2017

Organized by TU Vienna on behalf of Ada-Europe, in cooperation with ACM SIGAda, SIGBED, SIGPLAN and the Ada Resource Association (ARA)

The 22nd International Conference on Reliable Software Technologies - Ada-Europe 2017 will take place in Vienna, Austria. Following its traditional style, the conference will span a full week, including a three-day technical program and vendor exhibition from Tuesday to Thursday, along with parallel tutorials and workshops on Monday and Friday. This edition features a focused Special Session on Reliable and Safe Robotics.

\*\*\* DEADLINE Sunday 22 JANUARY 2017 \*\*\*

Regular & Special Session Papers + Industrial Presentations: submit via https://easychair.org/conferences/?conf=a daeurope2017

Tutorials & Workshops: submit to the Tutorial & Workshop Chair Ben Brosgol <brosgol at adacore.com>

For more information please see the full Call for Contributions at http://www.ada-europe.org/ conference2017

### Frama-C and SPARK Day in Paris

From: Claude Marché <Claude.Marche@inria.fr> Date: Thu, 26 Jan 2017 13:25:03 +0100 Subject: [Spark2014-discuss] [Save the date] 2017/05/30 Frama-C & SPARK Day: Formal Analysis and Proof for Programs in C and Ada To: frama-c-discuss@lists.gforge.inria.fr, spark2014-discuss@lists.forge.open-

do.org, Why3 Club <why3club@lists.gforge.inria.fr>

Date: Tuesday, May 30th, 2017

Location: Paris (Université Paris-Diderot, Amphithéatre Buffon, 15 rue Hélène Brion)

This one-day workshop aims at gathering both academic and industrial users of the environments Frama-C and SPARK, for sharing experiences and discussing perspectives. It is co-organized by CEA List (http://www-list.cea.fr/en/), AdaCore (http://www.adacore.com/), Inria joint lab `ProofInUse' (http://www.spark-2014.org/proofinuse), and Université Paris-Diderot. This workshop will take place in the context of the event `Open Source Innovation Spring 2017' (http://www.open-source-innovationspring.org/) initiated by thematic group `Logiciel libre' of the cluster Systematic-Paris-Region and IRILL (`Initiative de Recherche et Innovation sur le Logiciel Libre').

Claude Marché | tel: +33 1 69 15 66 08

### Ada-related Tools

### **Bare Bones**

From: Luke A. Guest

<laguest@archeia.com> Date: Thu, 17 Nov 2016 11:12:17 -0800 Subject: Screenshot of bare bones Newsgroups: comp.lang.ada

I've updated my bare bones OS project and it can now dump the location where a program crashed, using last chance handler.

https://github.com/Lucretia/bare\_bones

https://snag.gy/JludRq.jpg

[See also "Low-level Programming", AUJ 34-3, p. 155. —sparre]

### **Simple Components**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Sat, 19 Nov 2016 13:06:10 +0100 Subject: ANN: Simple Components v4.17 released

Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, multiple connections server/client designing tools.

http://www.dmitry-kazakov.de/ada/ components.htm

Changes the previous version:

- Bug fix in GNAT.Sockets.Connection\_ State\_Machine.ELV\_MAX\_Cube\_Client related to decoding valve position; - Set\_Thermostat\_Valve procedures were added to GNAT.Sockets.Connection\_ State\_Machine.ELV\_MAX\_Cube\_Client;

- Set\_Thermostat\_Parameters and Set\_Thermostat\_Schedule have the mode parameter added.

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Sun, 5 Feb 2017 12:36:43 +0100 Subject: ANN: Simple Components for Ada v4.18

Newsgroups: comp.lang.ada

[...]

The new version provides an implementation DIGEST-MD5 authentication method for SMTP clients and fixes some bugs.

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Mon, 20 Feb 2017 18:53:41 +0100

Subject: ANN: Simple Components for Ada v4.19

Newsgroups: comp.lang.ada

[...]

Changes to the previous version:

- Set\_Thermostat\_Temperature and Set\_Thermostat\_Automatic procedures of GNAT.Sockets.

- Connection\_State\_Machine.ELV\_MAX \_Cube\_Client allow specifying the temperature even if the thermostat is in the automatic mode;

- Downed primitive operations were added to GNAT.Sockets.Server package.

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Sun, 12 Mar 2017 09:39:46 +0100 Subject: ANN: Simple Components for Ada v4.20

Newsgroups: comp.lang.ada

[...]

Changes to the previous version:

- Modbus TCP client bug fixed. The bug prevented receiving large responses, more than 60 words, e.g. to FC3 (read holding registers).

### **GtkAda Contributions**

### From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Sun, 20 Nov 2016 11:01:39 +0100 Subject: ANN: GtkAda contributions v3.17 released

Newsgroups: comp.lang.ada

The library deals with the following issues:

- Tasking support;

- Custom models for tree view widget;

- Custom cell renderers for tree view widget;

- Multi-columned derived model;

- Extension derived model (to add columns to an existing model);

- Abstract caching model for directorylike data;

- Tree view and list view widgets for navigational browsing of abstract caching models;

- File system navigation widgets with wildcard filtering;

- Resource styles;

- Capturing resources of a widget;

- Embeddable images;

- Some missing subprograms and bug fixes;

- Measurement unit selection widget and dialogs;

- Improved hue-luminance-saturation color model;

- Simplified image buttons and buttons customizable by style properties;

- Controlled Ada types for GTK+ strong and weak references;

- Simplified means to create lists of strings;

- Spawning processes synchronously and asynchronously with pipes;

- Capturing asynchronous process standard I/O by Ada tasks and by text buffers;

- Source view widget support.

http://www.dmitry-kazakov.de/ada/ gtkada\_contributions.htm

This version provides minor bugs fixes for the Gtk.Main.Router package.

[See also "Simple Components (et al.)", AUJ 37-3, p. 126. —sparre]

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Tue, 21 Feb 2017 23:06:12 +0100 Subject: ANN: GtkAda contributions v3.18 Newsgroups: comp.lang.ada

[...]

Changes to the previous version:

- Gtk.Main.Router implementation of Send is changed so that when called on the main task context the callback is made at the loop end rather than immediately.

### IkaMo Bittorrent Library

From: Edward R. Fish

<onewingedshark@gmail.com>

Date: Wed, 23 Nov 2016 17:01:32 -0800

Subject: Re: There are some Ada lib for

processing bittorrent bencoded files and

streams ?

Newsgroups: comp.lang.ada

Well, here it is -- it and the 'shell' I was going to use for a torrent client.

https://github.com/OneWingedShark/ IkaMo

### VTKAda

From: Leonid Dulman

<leonid.dulman@gmail.com> Date: Sun, 27 Nov 2016 08:41:58 -0800

Subject: I'm pleased to announce VTKAda version 7.1.0 free edition release 27/11/2016

Newsgroups: comp.lang.ada

VTKAda is Ada-2012 port to VTK (Visualization Toolkit by Kitware, Inc) and Qt5 application and UI framework by Nokia VTK version 7.1.0, Qt version 5.7.0(5.8.0beta) open source and vtkc.dll,vtkc2.dll,qt5c.dll(libvtkc.so,libvtk c2.so,libqt5c.so) were built with Microsoft Visual Studio 2015 in Windows (WIN32) and gcc in Linux x86-64.

Package was tested with gnat gpl 2012 ada compiler in Windows 10 64bit, Debian 8.3 x86-64.

As a role Ada is used in embedded systems, but with VTKAda(+QtAda) you can build any desktop applications with powerful 2D/3D rendering and imaging (games, animations, emulations) GUI, Database connection, server/client, Internet browsing and many others thinks.

VTKAda you can be used without QtAda subsystem

Qt5Ada and VTKAda for Windows, Linux (Unix) is available from

https://drive.google.com/folderview?id=0 B2QuZLoe-yiPbmNQRI83M1dTRVE &usp=sharing (google drive. It can be mounted as virtual drive or directory or viewed with Web Browser)

[See also "VTKAda", AUJ 35-1, p. 9. —sparre]

### YAMI4

From: Maciej Sobczak <maciej@msobczak.com> Date: Thu, 8 Dec 2016 14:53:59 -0800 Subject: YAMI4 1.10.2 released Newsgroups: comp.lang.ada

I am pleased to announce that YAMI4 1.10.2, which is a minor update, was just released:

http://www.inspirel.com/yami4/

The update targets specifically newer versions of GNAT, which due to stricter handling of some language constructs[\*] refused to compile the older code. The library should now work correctly with newest GNAT versions.

[\*] The actual language problem was occasionally discussed on comp.lang.ada, most recently in this thread:

https://groups.google.com/forum/#!topic/c omp.lang.ada/HNUxQAz4\_FE/discussion

[See also "YAMI4", AUJ 34-4, p. 198. —sparre]

### PragmAda Reusable Components

From: PragmAda Software Engineering <pragmada@

pragmada.x10hosting.com> Date: Sat, 10 Dec 2016 13:15:42 -0700 Subject: PragmAda Reusable Components Update

Newsgroups: comp.lang.ada

There's a new version of the PragmARCs for ISO/IEC 8652:2007 available. This has minor changes to eliminate duplicated code between the random-number pkgs. Those who have used functions to obtain values in a range, or to obtain real values from generators that return integer results, may have to make minor changes to their code. Threefry\_Random now has a block of comments describing the concept and expected use of encryption-based (counter-based) RNGs, and has a new, pure function that returns a random value to fulfill the expectations of those who have read that counter-based RNGs can be accessed in parallel.

[See also "PragmAda Reusable Components", AUJ 37-3, p. 128. —sparre]

### **Image Analysis Library?**

From: Luke A. Guest

<laguest@archeia.com> Date: Wed, 25 Jan 2017 12:43:10 +0000 Subject: Re: Any suggestion for an image analysis package for Ada? Newsgroups: comp.lang.ada

> Has anybody a suggestion for an image analysis package for Ada?

> Or Computer/Robot vision?

>

> Or any idea for an easy way to use for example OpenCV directly from Ada?

Create bindings to OpenCV and don't stick a GPL license on them, use the same license as OpenCV, which is BSD.

From: Björn Lundin <b.f.lundin@gmail.com> Date: Wed, 25 Jan 2017 14:55:54 +0100

Subject: Re: Any suggestion image analysis package for Ada?

Newsgroups: comp.lang.ada

>[...]

The only binding I've heard of is described at <http://mdh.diva-portal.org/smash/ get/diva2:425844/FULLTEXT01.pdf>, but I'm not sure where the actual code is.

Googling gives some hints like <https://searchcode.com/codesearch/view/ 13067579/#>,

but I'm unsure if it is alive and maintained

### Qt5Ada

From: Leonid Dulman <leonid.dulman@gmail.com> Date: Sat, 28 Jan 2017 22:21:07 -0800 Subject: Announce: QtAda 5.8.0 Newsgroups: comp.lang.ada

Announce : Qt5Ada version 5.8.0 (539 packages) release 01/02/2017 free edition Qt5Ada is Ada-2012 port to Qt5 framework (based on Qt 5.8.0 final).

Qt5ada version 5.8.0 open source and qt5c.dll,libqt5c.so(x64) built with Microsoft Visual Studio 2015 in Windows, gcc x86-64 in Linux.

Package tested with gnat gpl 2012 ada compiler in Windows 32bit and 64bit , Linux x86,Linux x86-64 Debian 8.5.

It supports GUI, SQL, Multimedia, Web, Network, Touch devices, Sensors,Bluetooth, Navigation and many others things.

Changes for new Qt5Ada release :

Added packages for modules QWinExtracs,QTextToSpeech,QGamepa d,QHelp ,QScxml,QtChart modules support

Added new demos.

Added easy way to use Qt resource files (qrc).

My configuration script to build Qt 5.8.0 is: configure -opensource -release nomake tests -opengl dynamic -qt-zlib qt-libpng -qt-libjpeg -openssl-linked OPENSSL\_LIBS="-lssleay32 -llibeay32" -plugin-sql-mysql -plugin-sql-odbc plugin-sql-oci -icu -prefix "e:/Qt/5.8".

As a role ADA is used in embedded systems, but with QTADA(+VTKADA) you can build any desktop applications with powerful 2D/3D rendering and imaging (games, animations, emulations) GUI, Database connection, server/client, Internet browsing, Modbus control and many others things.

Qt5Ada and VTKAda for Windows, Linux (Unix) is available from

https://drive.google.com/folderview?id=0 B2QuZLoe-yiPbmNQRI83M1dTRVE &usp=sharing (google drive. It can be mounted as virtual drive or directory or viewed with Web Browser)

The full list of released classes is in "Qt5 classes to Qt5Ada packages relation table.docx". VTKAda version 7.1.0 is based on VTK 7.1.0 (OpenGL2) is fully compatible with Qt5Ada 5.8.0.

I hope Qt5Ada and VTKAda will be useful for students, engineers, scientists and enthusiasts. With Qt5Ada you can build any applications and solve any problems easy and quickly.

If you have any problems or questions, tell me know.

[See also "Qt5Ada", AUJ 36-3, p. 122. —sparre]

### Deepend

From: Brad Moore

<br/>

It's been a while since a new release of Deepend has been announced, the last announced version being version 3.4, though there have been updates since then.

Now that 3.9 has been posted, seems like a good time to mention the availability of new features and fixes.

Deepend is a set of storage pools for Ada 95, Ada 2005, and Ada 2012 that includes subpool capabilities. Groups of memory allocations from a storage pool can be assigned to specific subpools where groups of objects can be deallocated as a group by deallocating the subpool, rather than by individual deallocations of objects.

Each subpool is "owned" by a specific task in Ada, allowing allocations and deallocations to be efficient, as well as being safer and less error prone.

Since version 3.4, the most notable changes are;

- Ada 2012 subpools were not working in version 3.4, but now work properly with the Ada 2012 subpool syntax.

- It is now possible to set task ownership of the storage pool itself, as well as subpools.

- Portability changes made to integrate with PTC's ObjectAda 64bit compiler for Ada 2005 and Ada 95

- Portability changes made to integrate with RR Software's Janus Ada compiler for Ada 95

- Memory allocations returned by the generic allocators were not initializing memory. This is important for types that have discriminants or tags. Now memory is initialised which is consistent with behaviour when one uses Ada's "new" keyword syntax to provide the allocations.

- The generic allocator routines now support allocating unconstrained types, such as strings.

There are 4 different storage pools to choose from;

- Unbounded storage pool with subpool support

- Bounded storage pool with subpool support

- Unbounded storage pool without subpool support

- Bounded storage pool without subpool support

Deepend source code can be found at;

https://sourceforge.net/projects/ deepend/files/

[See also "Deepend", AUJ 37-4, p. 190. —sparre]

### **Reference Manual in Info** Format

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Thu, 23 Feb 2017 03:42:35 -0800 Subject: Ada Reference Manual 2012 with Technical Corrigendum 1 in info format available

Newsgroups: comp.lang.ada

The Ada Reference Manual 2012 with Technical Corrigendum 1 is now available in info format.

See http://stephe-leake.org/ada/arm.html

or update the Emacs package "Ada Reference Manual"

### Gnoga: PIXI Support with Sprites

From: Pascal Pignard <p.p11@orange.fr> Date: Sat, 18 Mar 2017 19:57:45 +0100 Subject: Rép : PIXI support with sprites. Newsgroups: gmane.comp.lang.ada.gnoga

I've rewritten PIXI Graphics closer to PIXI API rather than Context 2D API.

I've also added some PIXI Containers methods.

I've pushed this on Gnoga dev\_1.3 branch.

Feel free to send code review:

https://sourceforge.net/p/gnoga/code/ci/ dev\_1.3/tree/components/pixi/src/

One of my main concern is to define right Ada types while there are implicit in Javascript.

Beyond that, I wonder about some new API:

- Move\_To: moves sprite to a specified location with a specified speed

- On\_Collision: send a Gnoga event when a collision of 2 sprites or near a location

- Acceleration: add acceleration property (positive or negative)

Any other ideas are welcome.

Feel free to point out some API you want to be available.

Take a look to "leaves" demo which brings a very promising beginning of what could be done with PIXI.

Waiting for your feedbacks on PIXI support, I'll try to bring more support on mnmenu plugin.

### **Ada-related Products**

### **Rapita Verification Suite**

From: Rapita Systems Date: Fri Dec 9 2016 Subject: RVS 3.6 released URL: https://www.rapitasystems.com/news/ rvs-36-released

Rapita Systems is proud to announce the latest release of its on-target software verification tool suite RVS, version 3.6.

Over the last 6 months, we have been working tirelessly to make this our highest quality release to date.

Testing processes in the development of software for critical real-time embedded systems are incredibly expensive, both in terms of the effort required to run tests and subsequent analysis effort. We believe that our verification tools should improve the efficiency of these testing processes, by being designed to work seamlessly through the development process.

This is why we have been developing new features in RVS 3.6 that help direct the testing process, reducing the effort required to repeat tests and trace results to tests and requirements. These new features, as well as some of the other improvements made since RVS 3.5, are listed below:

- The new Treemaps feature in RapiCover lets you visualize your coverage at a glance

- New options for managing tests and subprograms allow you to filter coverage with fine granularity

- Our new Optimal Dataset Calculator can determine the minimal set of tests you must run again when you change code

- Our improved justification workflow gives you new options, such as including custom fields in templates

- RVS now supports many new Ada 2012 features, and recent GNAT compilers

- Our coverage parsing tool now lets you process multiple tests in a single command-line

- We have fixed over 150 bugs

You can find more information on some of the new features available in RVS 3.6 on our website.

[...]

[See also "Rapita Verification Suite", AUJ 37-2, p. 77. —sparre]

### GNAT Pro, CodePeer, QGen and SPARK Pro

From: AdaCore Press Center Date: Tue Mar 14 2017 Subject: AdaCore Releases New Versions of GNAT Pro, CodePeer, QGen and SPARK Pro

URL: http://www.adacore.com/press/ adacore-releases-v17/

Annual major release of flagship products brings new platform support, other enhancements

NUREMBERG, Germany, Embedded World Conference, March 14, 2017. AdaCore today announced the release of the latest version of its four major products:

- GNAT Pro 17.1, a development environment for Ada and C, on native and cross platforms;

- CodePeer 17.1, a deep static analysis tool for Ada that can identify bugs and vulnerabilities both during development and retrospectively on existing code bases;

- QGen 17.1, a model-based development and verification toolset for Simulink® and Stateflow® models, which generates code in MISRA-C or SPARK; and

- SPARK Pro 17.1, a verification environment that brings mathematicsbased assurance to high-integrity software.

"Developing and verifying critical systems is a challenging task, especially when certification against software standards such as DO-178C or EN 50128 is required," said Cyrille Comar, AdaCore President. "The latest version of our products will help organizations meet this challenge, through enhancements such as QGen's model-level debugger and CodePeer's detection of dangerous CWE weaknesses. Customers have long relied on AdaCore's tools and services when producing safety-critical or high-security software, and our V17.1 product line marks a continuation of our commitment.'

GNAT Pro includes a full-featured build toolset for Ada and C, Integrated Development Environments (the GNAT Programming Studio (GPS) and the Eclipse-based GNATbench), a comprehensive suite of tools (a visual debugger, a coding standard checker, etc.), and an extensive set of libraries and bindings. The GNAT Pro 17.1 release, based on GCC 6 and GDB 7.10, includes improved debugger support under GPS, a better algorithm for Ada elaboration order, enhancements to the GPRbuild multi-language build tool, better integration of GNATtest and GNATcoverage, an implementation of the extended Ravenscar profile on bare metal targets, and support for SMP on leon3. The supplemental GNATcoverage dynamic analysis tool has been upgraded with incremental coverage analysis, improved object code coverage, and support for ARM bare metal and native Windows (both 32- and 64-bit) platforms.

CodePeer is an Ada source code analyzer that detects run-time and logic errors, including a number of weaknesses among the Common Weakness Enumeration (CWE) Top 25 Most Dangerous Software Errors. CodePeer 17.1 provides improvements in the handling of "false alarms", more precise diagnostic messages, and a variety of user interface enhancements. The tool has been designated as "CWE Compatible" in the MITRE Corporation's Common Weakness Enumeration Compatibility and Effectiveness Program.

QGen is a qualifiable and tunable code generator and model verification toolsuite for a safe subset of Simulink® and Stateflow® models, particularly oriented towards real-time control software in safety-critical systems. QGen 17.1 includes a model-level debugger that is unique in the industry, allowing synchronized views and execution control between the model and the generated code. QGen 17.1 also includes support for Processor-in-the-Loop (PIL) testing, an enhanced user interface, improved code generation, and the implementation of additional blocks.

SPARK Pro is an integrated static analysis toolsuite for verifying highintegrity software through formal methods. It supports the SPARK 2014 language and can be used at various levels, for example to demonstrate the absence of run-time errors. SPARK uses the same contract-based programming syntax as Ada 2012, facilitating "hybrid verification" that combines traditional testing and formal methods. SPARK Pro 17.1 brings improved proof automation and enhanced proof interaction (including the generation of counterexamples).

[...]

[See also "GNAT Pro", AUJ 37-1, p. 16. —sparre]

From: AdaCore Press Center Date: Tue Mar 21 2017 Subject: AdaCore Releases GNAT Pro 17 Development Environment for SYSGO's PikeOS RTOS

URL: http://www.adacore.com/press/ gnat-pro-17-sysgos-pikeos-rtos/

AdaCore/SYSGO Partnership Fosters Spread of Embedded Ada

TOULOUSE, France, Certification Together International Conference, March 21, 2017 - AdaCore today announced the release of its GNAT Pro 17.1 development environment for SYSGO's Real-Time Operating System PikeOS®. With GNAT Pro 17.1, Ada users targeting PikeOS® will see a number of product enhancements, including upgrades to the underlying code generator and debugger technologies (to GCC 6 and GDB 7.10, respectively), better elaboration order handling, improved stubbing in

Volume 38, Number 1, March 2017

GNATtest, and enhanced debugger support in the GNAT Programming Studio (GPS) IDE.

AdaCore and SYSGO are longtime partners in the embedded market, with Ada's reliability benefits providing an excellent match for SYSGO's safetycritical PikeOS® RTOS. Over the past several years, the companies' joint customers have developed certified Ada applications meeting the highest levels in software standards such as EN 50128 (rail).

GNAT Pro for PikeOS® is especially suited for high-assurance embedded applications, thanks to its configurable run-time capability and its high-integrity profiles. The Zero Footprint (ZFP) profile minimizes (and in fact generally eliminates completely) all code in the executable other than the compilergenerated code for the application, and applications needing concurrency support can take advantage of both simple and extended versions of the Ravenscar tasking profile.

"Supporting RTOSes that help our customers build software that matters is part of our core strategy at AdaCore," said Jamie Ayre, Commercial Team Lead at AdaCore. "Over the years, customers have benefited from a close integration of our technologies and the common goal of providing a solid platform for building high-integrity software."

"For the past 10 years, SYSGO and AdaCore have enjoyed an effective and synergistic cooperation," said Markus Jastroch, Director of Marketing at SYSGO AG. "Our shared experience and deep knowledge of safety-critical applications has benefited our customers, in one example helping a multicore project successfully achieve Safety Integrity Level SIL 4."

### Ada and Operating Systems

### Linux: Interfacing to External Hardware

From: Patrick

<patrick@spellingbeewinnars.org>

Date: Sun, 1 Jan 2017 18:42:04 -0800

Subject: Interfacing Ada With Full Runtime

Directly to Electronic Chips Newsgroups: comp.lang.ada

Ada-AVR is a neat project and I am not knocking it. It doesn't have tasking support yet but this is of course a huge job.

If I want to connect any sort of computer running Linux directly to a circuit using "full Ada" with tasking support what are my options? By circuit, I mean a variety of electronic components and in this case with no microcontroller, an A/D chip is a simple example.

I am thinking that single board computers like BeagleBone are my best bet, they have plenty of GPIO lines.

Has anyone interfaced directly with chips via SPI or IC2 via a GPIO PCI card or GPIO-USB adapter?

Are there any other options?

From: Brian Drummond

<br/><br/><br/><br/><br/><br/><br/>Date: Mon, 2 Jan 2017 14:02:36 -0000<br/><br/>Subject: Re: Interfacing Ada With Full<br/>Runtime Directly to Electronic Chips

Newsgroups: comp.lang.ada

>[...]

There are ARM-Cortex development boards with a bit more resources, and Ada support including (Ravenscar) tasking, either bare-bones or over a small RTOS.

Look for work by Simon Wright in respect of these.

Much simpler than Beaglebone, but not full Linux.

Interfacing to hardware isn't difficult. Generally you abstract the hardware level into a package which knows where the register addresses are, and different (related) targets use different implementations of the packages.

For full Linux, I'd look at the Raspberry Pi. But then you get involved in writing device drivers - there's a project on the first steps on writing Linux device drivers in Ada, but it's more complex, and not as well trodden as Linux device drivers in C.

From: Simon Wright

<simon@pushface.org> Date: Mon, 02 Jan 2017 16:25:23 +0000 Subject: Re: Interfacing Ada With Full Runtime Directly to Electronic Chips

Newsgroups: comp.lang.ada

>[...]

You can talk I2C from a Raspberry Pi; see [1], [2]. It was simple to install GNAT etc from libre.adacore.com, since Raspbian is a Debian offshoot.

Beaglebone also supports Debian, see [3] for a report on this.

Both of the above use OS device support via file read/write/ioctl. If you want to go bare(ish) metal, there is the AdaCore Ada\_Drivers\_Library at [4]. This uses cross-compilation for ARM Cortex MCUs, compilers from AdaCore (or [5], [6] for Mac), with runtimes for boards mostly from STMicroelectronics (e.g. [7]).

The AdaCore runtimes support Ravenscar tasking[8] and come in two flavours, small footprint (-sfp-) and full (-full-). The -full- version supports exception handling and finalization and includes Ada.Numerics. Neither support containers easy enough to copy into the -fullversion, I expect).

The Ada\_Drivers\_Library uses a BSD license. The AdaCore runtimes use a full-GPL license. If this matters to you I have runtimes for Arduino Due and STM32F4[9] which are based on FreeRTOS and have the GCC Runtime Library Exception, allowing release of code on proprietary terms.

Just to indicate the flavour of this baremetal code, I have some SPI code for an STM32F427, using interface code generated by AdaCore's SVD2Ada[10], at [11].

- [1] https://sourceforge.net/projects/ raspi-i2c-ada/

- [2] http://raspi-i2c-ada.sourceforge.net

- [3] https://groups.google.com/forum/ #!topic/beagleboard/O5AU2XL6NJ8

- [4] https://github.com/AdaCore/ Ada\_Drivers\_Library

- [5] https://sourceforge.net/projects/ gnuada/files/GNAT\_GPL%20Mac%20 OS%20X/2016-arm-eabi-darwin-bin/

- [6] https://sourceforge.net/projects/ gnuada/files/GNAT\_GCC%20Mac%20 OS%20X/6.1.0/arm-eabi/

- [7] http://uk.farnell.com/ stmicroelectronics/stm32f407gdisc1/dev-board-foundation-linemcu/dp/2506840

- [8] https://en.wikipedia.org/wiki/ Ravenscar\_profile

- [9] https://sourceforge.net/projects/ cortex-gnat-rts/

- [10] https://github.com/AdaCore/svd2ada

- [11] https://github.com/simonjwright/ multiplexed-io/blob/master/drivers/spi1/ src/spi1-device.adb

From: Philip Munts <philip.munts@gmail.com> Date: Mon, 2 Jan 2017 23:55:50 -0800 Subject: Re: Interfacing Ada With Full

Runtime Directly to Electronic Chips Newsgroups: comp.lang.ada

>[...]

I suggest my own Linux Simple I/O Library

(http://git.munts.com/libsimpleio). It provides Pascal calling sequence wrappers around the Linux system calls for I2C, SPI, UART, and raw HID devices and includes some shim packages for GNAT.

I have tested it with both native and cross compilers on the BeagleBones Black and Green and Raspberry Pi 2 and 3. I use it mostly with the Raspberry Pi 2 cross toolchain (which also works fine for the BeagleBone family) from AdaCore and targeted to my own embedded Linux distribution called MuntsOS (http://git.munts.com/arm-linux-mcu). I also have a collection of packages and example programs for various Mikroelektronika click boards and Raspberry Pi hats that are not published yet. I am in the middle of writing a paper about this very topic.

### FreeBSD/ARM64: GNAT

#### From: John Marino

<dragonlace.cla@marino.st> Date: Wed, 8 Feb 2017 07:30:35 -0800 Subject: ANN: GNAT for FreeBSD/64 available (two options)

Newsgroups: comp.lang.ada

If anybody is interested in Ada on the 64bit ARMv8 architecture, there are a couple more options available to you today.

Last week I created a FreeBSD/DragonFly to FreeBSD64/ARM cross-compiler and placed it in ports: http://www.freshports.org/lang/ gnatcross-aarch64/

That compiler was based on previous GnatDroid work.

Over the weekend, I used that crosscompiler to fully bootstrap FSF GCC 6.3.1 to FreeBSD/ARM64. Now the entire FreeBSD Ports Ada framework is available on this soon-to-be-tier-1 platform. The existing gcc6-aux port (http://www.freshports.org/lang/gcc6-aux) was expanded to support aarch64.

It passes the complete testsuite. That required providing a freebsd-specific signal frame unwinder which I'm passing back to GCC.

results: http://www.dragonlace.net/ gnataux/freebsd\_arm64/

I also mentioned this news on my mostly neglected website: http://www.dragonlace.net/

### MacOS X: GDB on Sierra

From: Simon Wright

<simon@pushface.org> Date: Mon, 13 Feb 2017 22:09:41 +0000 Subject: GDB vs macOS Sierra Newsgroups: gmane.comp.lang.ada.macosx

To: GNAT-OSXdhAwdhUhaNgMT+7pcfOT8A@public.g mane.org

Apple's security enhancements in Sierra prevent the GDBs available on-line (in GNAT GPL 2016 from libre.adacore.com, FSF GCC 6.1.0 at Sourceforge) from working at all.

Discussion on an updated version and how to install it at http://forward-incode.blogspot.co.uk/2017/02/gdb-vsmacos-sierra.html.

[...]

### **Debian: GNAT**

From: Nicolas Boulenguez <nicolas.boulenguez@free.fr> Date: Sat, 18 Feb 2017 22:06:01 +0100 Subject: some news Newsgroups:

gmane.linux.debian.packages.ada

The compiler for next release will be gnat-7, currently only in experimental.

I suggest that we use this release to change the directory project in policy. Installing projects to /usr/share/ada/adainclude creates unmotivated divergence with upstream's /usr/share/gpr.

Users of gprbuild will not notice, it already searches in both directories.

Libxmlada compiles and the basic link/run test passes with this change, so I have good hope for gprbuild. Most other libraries rely on dh-ada-library and will be updated automatically during next build.

### **OpenVMS: GNAT**

From: Gérard Calliet <gerard.calliet@piasofer.fr>

Date: Thu, 2 Mar 2017 13:37:12 +0100 Subject: Gnat Ada on OpenVMS is back Newsgroups: comp.lang.ada

The OpenVMS OS, after an announced death in 2013, is back with its primary engineering team, organized as a start-up (www.vmssoftware.com).

In this context, we did a new build on OpenVMS / Itanium of the Gnat Ada compiler. We needed it for an industrial project (a port from OenVMS Alpha to OpenVMS Itanium, an urban transportation control software). The project is about to be run in production, with images compiled by our Gnat Ada compiler.

We want to generalize this renewal of Ada on OpenVMS. We offer free of charge our compiler (with no support) to downloading. The portal (still in work) www.vmsadaall.org can be used to ask for a download. We wish it becomes a place for exchanges between all people that are interested by the initiative.

If you are interested, please tell us, we need evaluations, advice, ideas.

### References to Publications

### Writing on Air

From: Dirk Craeynest <dirk@feles.cs.kuleuven.be> Date: Mon Apr 03 2017 Subject: Great "Ada Inside" demo -"Writing on Air" URL: http://blog.adacore.com/ writing-on-air [...] on AdaCore's blog there's a very nice article by Jorge Real from the Universitat Politècnica de València, describing a pendulum-like device that creates the illusion of text floating in the air!

See: <http://blog.adacore.com/ writing-on-air>.

See this device in action at the upcoming Ada-Europe 2017 conference, mid-June in Vienna, Austria!

### **DIY Instant Camera**

From: Fabien Chouteau <fabien.chouteau@gmail.com> Date: Mon Dec 12 2016 Subject: Make with Ada: DIY instant camera

URL: http://blog.adacore.com/ make-with-ada-diy-instant-camera

There are moments in life where you find yourself with an AdaFruit thermal printer in one hand, and an OpenMV camera in the other. You bought the former years ago, knowing that you would do something cool with it, and you are playing with the latter in the context of a Hackaday Prize project. When that moment comes - and you know it will come — it's time to make a DIY instant camera. For me it was at the end of a warm Parisian summer day. The idea kept me awake until 5am, putting the pieces together in my head, designing an enclosure that would look like a camera. Here's the result:

[...]

### Introductory Ada Programming Book

### From: Andrew Shvets

<andrew.shvets@gmail.com> Date: Sat, 31 Dec 2016 05:18:07 -0800 Subject: Introductory Ada Programming Book

Newsgroups: comp.lang.ada

My name is Andrew Shvets. I've been learning how to program in Ada over the past few years. As someone that came from C/C++, Java and Python many of the concepts that were in Ada were not easy to digest at first. After spending a fair amount of time looking for a guide that would help me out (something that would guide me through much of the ideas in Ada in a gentle manner was strongly preferred and be focused on Ada 2012), I couldn't find something like this (there is, on the other hand plenty of material that would explain more advanced concepts.) Having mastered many of the basic concepts in this wonderful language, I figured that having a guide for this would be very helpful and wrote one. Hence the book "Introductory Ada Programming Book: A Book for Beginner Programmers and Beginners to

Ada". The goal was to create a roadmap for those new to Ada learn more quickly and gain a certain level of mastery.

https://www.amazon.com/ Introductory-Ada-Programming-Book-Programmers-ebook/dp/ B01N6D5TPE/ref=sr\_1\_1?ie=UTF8& qid=1483189391&sr=81& keywords=introductory+ada

I'm open to sending PDFs as review copies, please send your requests to: introductory dot ada at gmail dot com

Thank you for taking the time to read through this! Also, thank you for those -on this newsgroup -- who have helped me better understand Ada!

Looking forward to hearing from everyone!

### Very Simple Scheduler

From: Maciej Sobczak

<maciej@msobczak.com> Date: Tue, 24 Jan 2017 00:16:34 -0800 Subject: Very Simple Ada Scheduler Newsgroups: comp.lang.ada

http://inspirel.com/articles/ Ada\_On\_Cortex\_Very\_Simple\_Scheduler .html

This article is an extension chapter for the Ada on ARM Cortex-M tutorial and presents a very simple, but yet surprisingly flexible scheduler for managing multiple tasks (well, finite state machines) in a single embedded system.

The example program from this article deals with 3 independently blinking LEDs, but can be easily extended to more complex designs.

Your comments are welcome,

### CAN Newsletter: Ada for Automation

From: Stéphane Los

<new.stephane.los@gmail.com> Date: Sun, 5 Mar 2017 12:32:51 -0800 Subject: "Ada for Automation" in the CAN Newsletter magazine March 2017: 25th

anniversary Newsgroups: comp.lang.ada

I wanted to let you know about the "CAN Newsletter magazine March 2017: 25th anniversary" which features an article about "Ada for Automation".

The magazine:

https://can-newsletter.org/engineering/ engineering-miscellaneous/170224\_cannewsletter-magazine-march-2017

Ada for Automation: Ada language for automation

https://can-newsletter.org/uploads/ media/raw/1cb325a3453440e4ae703be8e 392b763.pdf

### Handbook on DO-178C/ED-12C Guidance

From: AdaCore Press Center Date: Tue Mar 21 2017 Subject: AdaCore Publishes Handbook on DO-178C/ED-12C Guidance URL: http://www.adacore.com/press/ handbook-do-178c-ed-12c-guidance/

Free booklet shows how AdaCore qualified tools can reduce costs of certifying airborne software

TOULOUSE, France, Certification Together International Conference, March 21, 2017 – AdaCore today announced the publication and immediate availability of a free booklet, AdaCore Technologies for DO-178C / ED-12C, written by Quentin Ochem (AdaCore) and certification expert Frédéric Pothon. The booklet addresses the DO-178C / ED-12C standards suite the "core" DO-178C / ED-12C standard and its technology supplements - and explains many of their more subtle aspects in the context of several different development scenarios. In so doing, the booklet provides insights into how the Ada and SPARK languages, combined with AdaCore's products and services, can help customers develop and verify airborne software. Many of AdaCore's tools have been qualified on safetycritical projects and have qualification material available; using a qualified tool can save considerable effort in demonstrating that various objectives in the DO-178C / ED-12C standards suite have been met.

"DO-178C is one of the most complex software safety standards in the industry," said Quentin Ochem, lead of Business Development at AdaCore. "This booklet is aimed at software engineers and architects, to help them read between the lines of the standard and better understand the intent, using AdaCore's technologies to illustrate how to meet the various requirements."

The booklet approaches its subject matter from several angles. One chapter summarizes the Ada and SPARK languages and describes various AdaCore tools, many of which have been qualified or are qualifiable for safety-critical systems:

- The GNAT Pro Assurance development environment, including support for "sustained branches", which allows customers to evolve their software on a stable but maintained version of the GNAT Pro environment;

- The CodePeer advanced static analysis tool for Ada, which can find subtle bugs and vulnerabilities both during development and retrospectively on existing codebases;

- Basic static analysis tools, including the GNATcheck code standard enforcer and

the GNATstack tool for computing maximum stack usage;

- Dynamic analysis tools: GNATtest (a test harness generator), GNATemulator (a target emulator), and GNATcoverage (a code coverage analyzer at both the object and source levels, handling statement coverage, decision coverage, and modified condition/decision coverage);

- Integrated Development Environments: GNAT Programming Studio (GPS), GNAtbench, and GNATdashboard; and

- The QGen model-based development and verification toolset, which includes a tunable and qualifiable code generator from a safe subset of Simulink® and Stateflow® models to SPARK or MISRA-C.

A major section of the booklet is a chapter that shows how to exploit AdaCore's technologies to comply with the guidance in the DO-178C / ED-12C suite, in the context of several development scenarios (use cases):

- Coding with Ada 2012 without using Object-Oriented Technology (OOT). This use case shows how AdaCore's products and services contribute to the activities in the core DO-178C / ED-12C standard.

- Coding with Ada 2012 and using OOT. This use case takes into account the guidance in DO-332 / ED-217 (Object-Oriented Technologies and Related Techniques), in particular the objective of Local Type Consistency.

- Developing a design model and using a qualified code generator (QGen). This use case takes into account the guidance in DO-331 / ED-218 (Model-Based Development and Verification).

- Using SPARK and formal analysis. This use case takes into account DO-333 / ED-216 (Formal Methods) and explains how to gain credit for formal proofs to reduce or eliminate testing activities.

For each use case, the booklet explains which AdaCore technologies are applicable, and which activities in the DO-178C / ED-212 suite they contribute to.

The booklet also includes a set of reference tables that summarize how the various AdaCore technologies help satisfy the specific objectives in the DO-178C / ED-12C suite.

### Availability

The DO-178C booklet is available now, at no cost. To download a PDF version please visit www.adacore.com/tech-do-178c. For a printed copy please contact info@adacore.com

[...]

### Ada Inside

### **SparForte**

From: Ken O. Burtch <koburtch@gmail.com> Date: Mon, 14 Nov 2016 06:32:27 -0800 Subject: [ANN] SparForte 2.0 Newsgroups: comp.lang.ada

SparForte is a shell, scripting and web template language based on Ada.

Version 2.0 was released on October 10, 2016.

Major new features include:

- in out, out mode parameters on user functions

- GNU readline is used for the command prompt

- Berkeley DB support

- Software architect policy blocks

Also the database configuration issues should be resolved (thanks to volunteers).

The SparForte home page is:

http://www.sparforte.com

A summary of the changes are found here:

http://www.pegasoft.ca/coder/ coder\_october\_2016.html

The full release notes are found here:

http://www.sparforte.com/news/2016/ news\_oct2016\_2.html

[See also "SparForte", AUJ 37-3, p. 130. —sparre]

From: Ken O. Burtch <koburtch@gmail.com> Date: Wed, 28 Dec 2016 11:34:00 -0800 Subject: [ANN] SparForte 2.0.1 Newsgroups: comp.lang.ada

SparForte 2.0.1 is bug fix release of SparForte 2.0.

SparForte is an open source shell, scripting and web template language loosely based on the Ada language. It runs on Linux and FreeBSD. It is maintained by myself and volunteers.

There are 17 updates included in this release. The change log can be found here:

http://www.sparforte.com/news/2016/ news\_dec2016.html

The language can be downloaded from the SparForte home page:

http://www.sparforte.com/index.html

From: Ken O. Burtch <koburtch@gmail.com> Date: Thu, 2 Feb 2017 10:10:05 -0800 Subject: [ANN] SparForte 2.0.2 Newsgroups: comp.lang.ada

SparForte 2.0.2 contains follow-up bug fixes for SparForte 2.0. There are 19

changes. A complete list of changes is located at:

http://www.sparforte.com/news/2017/ news\_feb2017.html

The SparForte home page is

http://www.sparforte.com

SparForte is my Ada-based shell, web template and scripting language. It is maintained by volunteers.

### **MAX! Home Automation**

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Mon, 21 Nov 2016 18:17:37 +0100 Subject: MAX! home automation v1.6 released

Newsgroups: comp.lang.ada

MAX! home automation is a GTK application used to control ELV/eQ3 network of heating devices, like radiator thermostats, shutter contacts etc.

http://www.dmitry-kazakov.de/ada/ max\_home\_automation.htm

- Changes to the previous version:

- Monitoring radio band duty cycle was added;

- Commands that control thermostats are serialized and monitored for failures;

- Cube radiator thermostats configuration save and restore added;

- Thermostat schedule and parameters upload diagnostics added;

- Offset temperature can be set negative;

- HTTP server request documentation getset\_temperature changed to get-settemperature;

- Save file dialogs changed to ask override confirmation;

- Bug fix in HTTP server that prevented querying the thermostat's measured temperature;

- Valve position is correctly reported;

- Thermostat parameters and schedule optimized to minimize RF traffic;

- Documentation extended with instructions how to run the application remotely or in the headless mode.

[See also "MAX! Home Automation", AUJ 37-2, p. 79. —sparre]

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 22 Feb 2017 18:07:19 +0100 Subject: MAX! home automation v1.8 Newsgroups: comp.lang.ada

[...]

Major changes in this version are E-mail reports when device batteries go low and ODBC or SQLite long term data logging.

### **Muen Separation Kernel**

From: Adrian-Ken Rueegsegger <ken@codelabs.ch> Date: Mon, 6 Feb 2017 19:30:05 +0100 Subject: [ANN] Muen development version 0.8 released Newsgroups: comp.lang.ada

We are proud to announce the availability of Muen version 0.8.

The following major features and improvements have been implemented since the last release:

#### Subject Lifecycle

With the implementation of a subject loader (SL) component it is now possible to reset and restart subjects at runtime with minimal support from the kernel.

The new loader policy abstraction eases the specification of loader subjects which control the lifecycle of one or multiple subjects. Aside from the state, loaders have access to the entire address space of a managed subject in order to be able to set up the execution environment.

The new SL component written in SPARK 2014 initializes/resets the writable memory regions of its associated subjects. To find the actual memory regions to process, the loader consults each monitored subject info region by querying it using the new subject info (sinfo) client library. Prior to starting execution of a monitored subject, integrity hashes of each memory region are calculated and compared to their reference value provided by the sinfo data.

The demo system has been adapted to make use of this new functionality: the NIC Linux can be restarted by pressing the Right Control+F10 key combination.

#### System reboot/shutdown

The introduction of a new 'kernel' event mode and event actions for system reboot and poweroff enables policy writers to grant subjects the capability to initiate a system reboot or shutdown. If a subject triggers a reboot event, the kernel performs a power-cycle using the Reset Control Register (I/O port 0xcf9). The shutdown functionality is implemented by performing an ACPI shutdown using the poweroff port and the PM1A Control Sleep Type capability.

As with the subject restart, the demo system has been extended to showcase the new feature: a system reboot can be triggered by pressing the Right Control+F11 keys while Right Control+F12 initiates a shutdown.

#### Policy & Toolchain improvements

The Muen policy has been extended with a config section which enables the parametrization of a system via the declaration of configuration values. Boolean expressions referencing existing config values can be used to formulate additional properties. The introduction of conditionals that reference config values or expressions selectively enable/disable parts of the policy which allows for flexible customization of a system at integration time.

To increase the expressiveness of the policy and ease native component development, component descriptions have been extended with the library construct including dependency declaration. Additionally it is now possible to declare logical devices as well as memory and channel array resources. The new component spec generation tool reads the description of a given component and generates Ada/SPARK packages containing constants of the declared logical component resources. These generated specifications can be used in the component source code to access the declared resources. This ensures a consistent view of the system according to the policy.

Physical memory regions can now optionally declare an integrity hash. The SHA-256 hash value can be used to verify the initial content of a given region at runtime. A tool has been implemented that calculates hashes for all physical regions with content (file or pattern). The region hashes are exported as part of the subject info data and used by the SL as described above.

#### Kernel improvements

To prevent potential issues related to Intel Hyper-Threading, e.g. side-channels, the kernel now only activates one thread per physical CPU core. CPUID leaf 11 (Extended Topology Enumeration Leaf) is used to determine the SMT ID of each logical CPU and deactivate it if the ID is non-zero. This effectively disables HT even if no such option is present in the BIOS.

Feature-wise, support for event actions has been added. The improved functionality increases the flexibility of the event mechanism and facilitates subject lifecycle management as well as system restart and shutdown.

Many other improvements and stabilizations such as e.g. replacement of assembler code with SPARK and reduction of stack size to 4K have been implemented.

#### Further changes

Further changes and improvements include

- Support for 32-bit Windows VMs using Genode/Virtualbox

- Support for Intel Broadwell and Skylake microarchitecture

- Support for PCI multi-function device pass-through

- Implement tool to statically calculate worst-case stack usage

- Implement tool to generate scheduling plans

- Implement subject info client library in SPARK 2014

- Update of Linux kernel to version 4.6

- Add support for multiple initramfs per Linux subject

With the advent of subject lifecycle management, system shutdown and reboot support and the numerous toolchain improvements, the Muen platform is getting more and more mature. The continuous enhancement and refinement of system policy abstractions, especially the components construct, further simplifies the system specification process and enables the description of complex systems composed of a large number of subjects.

We are also thrilled that this release includes the previously announced [1] support for execution of hardwareaccelerated 32-bit Windows VMs on top of the Muen SK through the use of Genode/VirtualBox as a deprivileged VMM. A detailed description of the architecture and an account of how this feature came to be can be found in the Genode 16.08 release notes [2].

Last but not least we would like to thank Christiane Kuhn for her contribution of the scheduling plan generation tool [3] which she developed as part of a student project/internship.

Further information about Muen is available on the project website [4] and the git repository can be found at [5].

Please feel free to give the latest development version of Muen a try. As always, feedback is very much appreciated!

[1] https://groups.google.com/forum/ #!topic/muen-dev/ln7ZrIfDk8c

[2] https://genode.org/documentation/ release-notes/16.08#VirtualBox\_4\_ on\_top\_of\_the\_Muen\_separation\_kernel

[3] https://git.codelabs.ch/?p=muen/ mugenschedcfg.git

[4] https://muen.codelabs.ch/

[5] https://git.codelabs.ch/?p=muen.git

[See also "Muen Separation Kernel", AUJ 37-1, p. 18. —sparre]

From: Adrian-Ken Rueegsegger <ken@codelabs.ch> Date: Mon, 13 Feb 2017 18:07:39 +0100 Subject: Re: [ANN] Muen development version 0.8 released

Newsgroups: comp.lang.ada

[...]

> 1. I understand that this separation Kernel is an hypervisor, but how does it compare to other hypervisor like for instance the one from Wind River? Does Muen allows hard Real Time software? What kind of scheduling does the Muen kernel?

I am not sure how to best answer this question since I do not know the Wind River Hypervisor. Looking at the product information online some of the features are quite similar while in other areas there are differences. Since I am not in a position to make a meaningful comparison, let me instead list some of the features of Muen to give you a better picture:

### Static resource allocation

One of the main design choices of the Muen Separation Kernel and systems build on top of it is, that all system resources such as memory, devices, CPU time etc are assigned to subjects via the system policy at integration time. As a consequence, systems have a static structure which does not change during runtime. This means that the SK does not perform any dynamic resource allocation at runtime, which greatly simplifies the kernel design and implementation. Note that Muen has support for Intel VT-d (DMA and Interrupt remapping) which facilitates PCI device pass-through.

### Multicore support

All cores provided by a hardware platform can be used for subject execution.

### Scheduling

Muen implements a fixed, cyclic scheduler. Execution order and time assignment of each subject is specified in the system policy. The kernel enforces the scheduling plan during runtime by executing each subject for the alloted time and then (preemptively) switching to the next one.

### Subject execution environment

Since Muen employs Intel Virtualization Extensions (VT-x) incl. Unrestricted Guest Support and Nested Paging/Extended Page Tables (EPT) as a basic mechanism to execute and separate subjects, it can run many different types of subjects:

- Native 64-bit Ada & SPARK 2014 subjects.

- Linux 32/64-bit VMs.

- Genode x86\_64 base-hw system.

- Windows 32-bit VMs (by means of Genode/VirtualBox).

A subject execution environment can be further customized in the system policy, e.g. allow access to the Timestamp Counter (TSC).

#### Small size and low complexity

During the development of Muen we took deliberate design choices to minimize the overall kernel complexity. The simplification drastically reduces code size which is illustrated by the current, tiny kernel size of ~5'500 sloc. This make the kernel suitable for formal verification. On the other hand, a consequence is that the supported feature set is smaller than what you get from a general purpose/dynamic hypervisor. Here are two examples of restrictions imposed by Muen:

- Subjects are not allowed to migrate between CPU cores

- Muen only runs on recent x86\_64 hardware with Intel VT-x and EPT support

Aside from these features there are some additional points that we think are important.

### Availability of code & documentation

Muen is an open source project and we publish all code and documentation. We think it is paramount for an SK to be independently inspectable since it is always part of the Trusted Computing Base (TCB) of any system built on top of Muen. The small size makes it realistically possible to read and understand the entire Muen kernel code.

### Formal Verification

Since Muen is implemented in SPARK 2014, we prove full absence of runtime errors at the source code level. Since we publish the entire source code and because the SPARK GPL toolchain by AdaCore is freely available, everybody can independently reproduce these proofs in their own environment.

> 2. How does Muen compare to solutions like Linux KVM? How does it compare to Xen?

Similar to the first question it is not so easy to compare Muen to a fully fledged hypervisor such as KVM and Xen since it is comparing apples with oranges. Xen and KVM are fully-fledged hypervisors which feature dynamic VM construction and deconstruction, live migration etc. With Muen systems you have to take more of an embedded system development approach, where you know your target hardware platform and system structure at integration time.

I think in the end it comes down to this: since Muen is a Separation Kernel it (intentionally) does not address all use cases targeted by general purpose hypervisor.

> 3. Will it be possible to use Muen with the future OpenVMS on x86-64?

I have no prior experience with OpenVMS. Since there are no inherent restrictions imposed by Muen on the kind of subjects that can be executed it should in principle be possible. However, without more technical information and access to OpenVMS x86-64 there is no way for me to estimate the required porting effort.

PS: If you have more questions regarding Muen there is also a project mailing list, see [1].

#### [1] https://muen.sk/#mailing-list

From: Adrian-Ken Rueegsegger <ken@codelabs.ch> Date: Wed, 1 Mar 2017 22:39:24 +0100 Subject: Re: Unikernel / Ada Newsgroups: comp.lang.ada

> Some time ago I read some papers on the MirageOS (https://mirage.io/), a library operating system. The model works in short (simplified): The application sources (in case of Mirage in OCaml) are compiled / linked together with all its depending "library os" sources into one fully standalone binary (unikernal). This binary is then deployed directly f.e. on a Xen Hypervisor. No complex OS involved. small, efficient, more secure, fast to boot,

> https://mirage.io/wiki/overview-ofmirage

>

> I find this model interesting for GNAT. Maybe there are already some ideas around?

Funny you should mention MirageOS specifically. I have been toying around with it over the past weekend and actually managed to run some example scenarios as subjects on the Muen Separation Kernel [1]. I posted a small teaser here [2].

Regarding Ada: we have published a few SPARK/Ada subjects that run natively on Muen. Currently we only provide a zerofootprint runtime which obviously restricts the language features one can use to write native Ada/SPARK subjects. However, there is no inherent limitation, it is simply a matter of extending the runtime.

Apropos of developing a TCP/IP stack from scratch: this might be of interest [3].

### [1] https://muen.sk

[2] https://twitter.com/Kensan42/status/ 835941733359882240

[3] https://github.com/AdaCore/ spark2014/tree/master/testsuite/gnatprove/ tests/ipstack

### **Running Gnoga in Amazon** Cloud

From: Björn Lundin

<br/><b.f.lundin@gmail.com><br/>Date: Mon, 20 Mar 2017 09:22:15 +0100<br/>Subject: Re: Experience with Amazon Web<br/>Services ?

Newsgroups: gmane.comp.lang.ada.gnoga

> Did anyone deploy a GNOGA app on Amazon Web Services (more precisely 14

Amazon Cloud service, https://aws.amazon.com/ec2/)?

Yes, I did a year ago or so.

It just worked - after my friend (the one with Apache know-how of us) had set it up.

> Any advice, caveat, feedback ?

http+https is redirected to the gnogaservice for a certain path.

There is also some stuff handling

upgrading the connection to web sockets.

[...]

From: Björn Lundin <b.f.lundin@gmail.com> Date: Mon, 20 Mar 2017 13:59:48 +0100 Subject: Re: Experience with Amazon Web Services ?

Newsgroups: gmane.comp.lang.ada.gnoga

Björn Lundin wrote:

- > http+https is redirected to the gnogaservice for a certain path.

- > There is also some stuff handling upgrading the connection to web sockets. No there was not. I think now that was before we went through Apache.

### >[...]

The gnoga part listen at http://localhost:9080 and all https stuff is via Apache2

http is redirected to https some browser do not need to login, others do

The machine is known to DNS servers

This is on a

uname -a

Linux prod 3.2.0-4-amd64 #1 SMP Debian 3.2.68-1+deb7u2 x86\_64 GNU/Linux

cat /etc/apache2/sites-enabled/030somesite.somewhere.com.conf

<VirtualHost \*:80> ServerName somesite.somewhere.com ServerAdias somesite2.somewhere.com ServerAdmin someone@somesite.somewhere RewriteEngine on RewriteCond % {SERVER\_PORT} !^443\$ RewriteRule .\* https://% {SERVER\_NAME}% {REQUEST\_URI} [R,L] LogLevel info CustomLog \${APACHE\_LOG\_DIR}/ log\_80.nonobet.com\_access.log

combined ErrorLog \${APACHE\_LOG\_DIR}/ log\_80.nonobet.com\_error.log

### </VirtualHost>

<VirtualHost \*:443>

ServerName somesite.somewhere.com ServerAlias somesite2.somewhere.com ServerAdmin

someone@somesite.somewher

RewriteEngine on RewriteCond % {HTTPS} =off RewriteRule .\* - [F,L] SSLEngine on SSLCertificateFile /etc/apache2/sites-available/ wildcard.somesite.com\_cert.pem SSLCertificateKeyFile /etc/apache2/sites-available/ somesite\_common\_server\_key.pem LogLevel info CustomLog \${APACHE\_LOG\_DIR}/ log\_443.nonobet.com\_access.log combined ErrorLog \${APACHE LOG DIR}/ log\_443.nonobet.com\_error.log ProxyPass / http://127.0.0.1:9080/ ProxyPassReverse / http://127.0.0.1:9080/ <Location "/"> AuthName "Please login!" AuthType Basic AuthBasicProvider file AuthUserFile /etc/apache2/ sites-available/ somesite.com authentication Require valid-user SetEnvIfNoCase ^User-Agent\$ .\*Mobile ALLOW\_IN SetEnvIfNoCase ^User-Agent\$ .\*Epiphany ALLOW\_IN Order Deny, Allow Deny from all Allow from env=ALLOW\_IN Satisfy Any </Location> </VirtualHost>

### Ada in Context

### Getting Started with Bareboard Development

From: Jeffrey R. Carter <jrcarter@acm.org> Date: Sat, 12 Nov 2016 21:01:36 -0700 Subject: Re: Getting started with bareboard development Newsgroups: comp.lang.ada

Adam Jensen wrote:

> How is it done in embedded software engineering? (Links and/or references are very welcome)!

Typically embedded S/W has to interface to various H/W devices (sensors and actuators). Frequently such S/W is designed around the capabilities and features of the intended H/W. This is not a good idea. When the intended H/W changes (as it does frequently on the projects I've been involved in) the entire design has to be revised.

What I have done when designing such S/W is to 1st design the core S/W without regard to the capabilities and features of the intended H/W. I create the simplest and clearest design, and this identifies the kind of information the S/W needs to

obtain and the kind of external actions it needs to take.

Next, for each piece of external information the S/W needs to obtain, I write a pkg spec for a S/W-leaning interface. This keeps the S/W simple and clear by providing just the kind of I/F it needs.

Then, for each intended H/W device, I write a pkg spec for a H/W-leaning interface. This reflects the capabilities and features of the device.

Then I write bodies for each of the S/W I/F pkgs that use the H/W I/F pkgs.

Now comes the fun part. I write an environment pkg that simulates reality, and write simulation bodies for the H/W I/F pkgs that read or modify that simulated reality. The body can take do things to make its behavior realistic; for example, if a sensor is noisy, the body would add noise to the real value.

This lets you play with your S/W and see if it behaves reasonably.

When it's time to run the S/W on the real system, you eliminate the environment pkg and replace the H/W I/F bodies with ones that actually I/F with the H/W. Note that the only differences between the simulated and actual systems are those bodies.

This approach has a number of benefits:

- Changing a device only affects a S/W I/F body and a H/W I/F pkg.

- Often the simplest and clearest design for the core S/W wants to access information or take action in a way the intended H/W doesn't support. The S/W I/F pkg provides a single place to convert between the 2 views, keeping the core S/W uncoupled. For example, in the ubiquitous cruise-control problem, the best approach for the core S/W might be for it to decide when it obtains the car's speed, but a common design for the speed sensor is something that generates an interrupt every time something rotates a certain amount.

- While there is usually a 1:1 correspondence between S/W and H/W I/F pkgs, there need not be. I've seen sensors that returned multiple, unrelated values. The design had multiple S/W I/F pkgs interacting with a single H/W I/F pkg.

- I've worked on projects where the whole point was to create a simulation to see if the approach is viable, with no idea what the H/W devices would be like in a real system. By using this approach, when it was decided to go ahead with a real system, only the H/W I/F pkgs and the S/W I/F bodies had to be rewritten.

When I present such a design, coders usually start whining about "efficiency". In my decades of experience, such a design has never been responsible for a

### system not meeting its timing requirements.

#### From: Jeffrey R. Carter <jrcarter@acm.org> Date: Sun, 13 Nov 2016 14:04:59 -0700 Subject: Re: Getting started with bareboard development Newsgroups: comp.lang.ada

#### Adam Jensen wrote:

> When writing device drivers, how do you mock the memory map of the target hardware?

>

> In the mocked hardware, how is timing controlled?

>

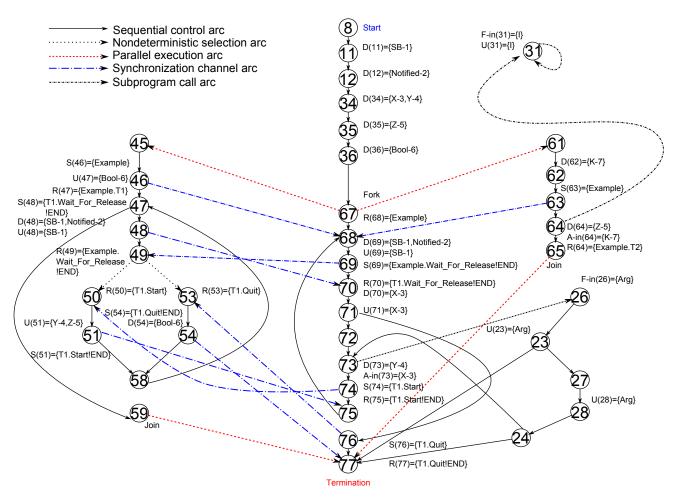

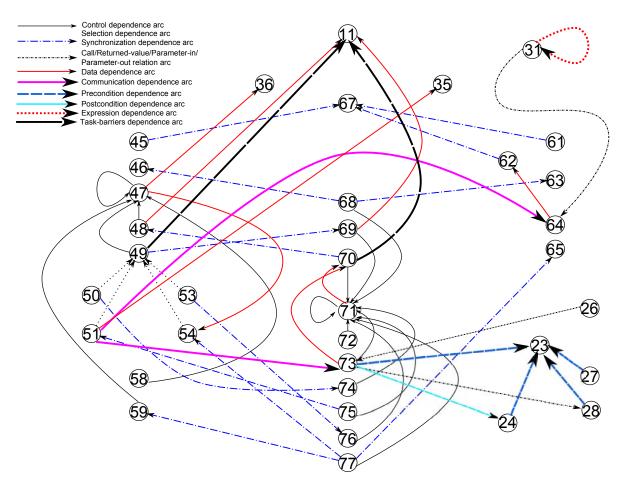

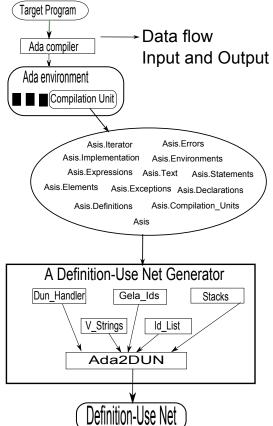

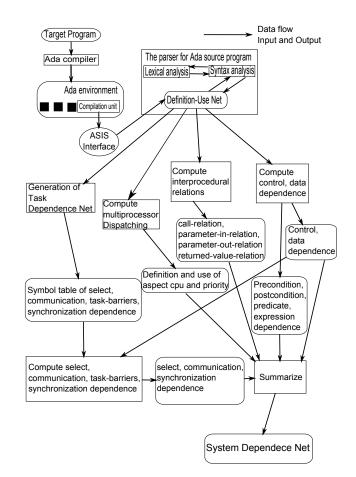

> When extending and mapping run-time support to the mocked hardware, how does that fit into the run-time system for the native platform (your workstation)?