# ADA USER JOURNAL

# Volume 38 Number 2 June 2017

# Contents

|                                                                                                                                                                     | Page              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                                               | 66                |

| Editorial                                                                                                                                                           | 67                |

| Quarterly News Digest                                                                                                                                               | 68                |

| Conference Calendar                                                                                                                                                 | 87                |

| Forthcoming Events                                                                                                                                                  | 92                |

| Community Input for the Maintenance and Revision of the Ada Programming Langua                                                                                      | .ge 96            |

| Ada-Europe 2017 Panel                                                                                                                                               |                   |

| E. Ploerederer and J. Garrido<br>"Panel Session Summary: The Future of Safety-Minded Languages"                                                                     | 97                |

| Articles                                                                                                                                                            |                   |

| B. I. Sandén<br>"Protocol Monitors: a Control-System Structuring Concept"                                                                                           | 99                |

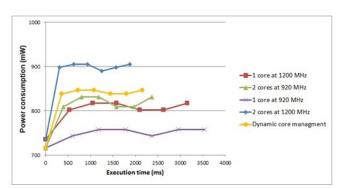

| A. Ghorbel, N. Ben Amor and M. Jallouli<br>"Towards a Power Adaptation Strategy in Multi-core Embedded Devices. A Case S<br>a HMI for Wheelchair Command Technique" | Study:<br>105     |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                                           | 112               |

| Ada-Europe Sponsors                                                                                                                                                 | Inside Back Cover |

# Editorial Policy for Ada User Journal

### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

### Announcements and Reports

We are happy to publicise and report on events that may be of interest to our readers.

### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

### Submission Guidelines

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

As usual, the June issue of the Journal is finalised shortly after the Ada-Europe conference, which this year took place in Vienna, Austria, in the week of June 12 to 16. The organizers must be congratulated for a very successful conference, with a very rich program, both technical and social. The program included not only a set of high-quality scientific papers and technical presentations, but also a panel on the future of safety-minded languages in general (and Ada in particular). The reader will find in this issue a summary of the panel contributions, by Erhard Ploedereder, panel moderator and Jorge Garrido, rapporteur. Also related to the future of Ada, this issue publishes the call for Community Input for the Maintenance and Revision of the Ada Programming Language, put forward by ISO/IEC JTC 1/SC 22/WG 9, the group of experts responsible for the maintenance and revision of Ada, requesting comments and contributions for the next revision of the language. I encourage you to read, and contribute!

As announced in Vienna, next year the Ada-Europe conference will take place mid-June in Lisbon, Portugal. You will forgive me in recommending (more than usual for obvious reasons) that you plan already to attend: not only for the conference program, which for sure will be worthwhile, but to have the opportunity to visit the "coolest" city in Europe (CNN) or Europe's best work-and-play capital (BBC). Don't miss it! I would also like to call your attention to the 19th International Real-Time Ada Workshop, which will return to the beautiful place of Benicasim, Spain, in April. You can find the preliminary call for papers of these two important events in the Forthcoming Events section of this issue. Together with these you will also find an announcement of the Make with Ada programming competition, which promotes the development of embedded code using Ada and SPARK.

As for the other technical contents of the issue, the first article, by Bo Sandén, from the Colorado Technical University, USA, presents an approach to encapsulate Ada protected objects with a protocol monitor concept. Afterwards, a group of authors from the Ecole Nationale d'Ingénieurs de Sfax, Tunisia, describes an approach to address power management, in order to comply with energy budgets, in multicore embedded devices. Also as usual, the News and Calendar sections, produced by Jacob Sparre Andersen and Dirk Craeynest, the respective editors, complete the issue.

As a post scriptum, I would like to apologise for any delay the issue may have in arriving to your desk. The Ada User Journal is prepared by a team of highly-dedicated volunteers, and occasionally pressing matters delay concluding an issue. When that happens near to vacation periods, as in this issue, printing and distribution may be affected. We are sorry for that and will, as always, persevere in reducing these delays as much as possible.

Luís Miguel Pinho Porto June 2017 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

### Jacob Sparre Andersen

Jacob Sparre Andersen Research & Innovation. Email: jacob@jacob-sparre.dk

# Contents

| Ada-related Events         | 68 |

|----------------------------|----|

| Ada-related Resources      | 70 |

| Ada-related Tools          | 70 |

| Ada-related Products       | 75 |

| Ada and Operating Systems  | 76 |

| References to Publications | 77 |

| Ada Inside                 | 77 |

| Ada in Context             | 78 |

# Ada-related Events

[To give an idea about the many Adarelated events organised by local groups, some information is included here. If you are organising such an event feel free to inform us as soon as possible. If you attended one please consider writing a small report for the Ada User Journal. —sparre]

## "Make with Ada" Programming Competition

From: Jamie Ayre <ayre@adacore.com> Date: Mon, 15 May 2017 14:14:35 +0200 Subject: [AdaCore] Make With Ada competition launched

To: libre-news@lists.adacore.com

Dear GNAT community,

We are pleased to announce the 2nd annual Make with Ada competition launches today! The competition calls on embedded developers across the globe to build cool embedded applications using the Ada and SPARK programming languages and offers over \$8000 in total prizes, as well as a 3D printer as the student-only prize.

The competition runs from May 15 to September 15, 2017 and you can register your embedded project idea from 15:00 CEST today at www.makewithada.org. You may participate in the competition as an individual or part of a small team and we invite you to check out our resources to get you started here

http://makewithada.org/getting-started.

Don't miss out and start Making with Ada today!

[See also ""Make with Ada" Winners", AUJ 38-1, p. 4. —sparre]

## Automotive - Safety & Security

From: Christoph Karl Walter Grein <christ-usch.grein@t-online.de> Date: Sat, 20 May 2017 11:25:48 -0700 Subject: Call for Participation: Automotive - Safety & Security 2017 Newsgroups: comp.lang.ada

Automotive - Safety & Security 2017

May 30+31, 2017, Stuttgart, Germany Venue: Robert Bosch Auditorium in Stuttgart/Feuerbach, Germany

http://www.automotive2017.de

Seventh in the series, the conference deals again in aspects of reliability, safety, security, privacy, etc. in automotive systems, many of which are heavily influenced by advances in applied Software Engineering. The presented papers discuss technologies and processes to improve safety and security of these systems.

Keynote speakers are Franco Gasperoni (AdaCore, New York), Christian Wieschebrink (BSI, Bonn), and Stefan Jähnichen (TU Berlin, Einstein Center Digital Future).

The programme of the conference, the associated committee meeting and the social events as well as registration and venue information is found on the website cited above.

The conference language is primarily German or English by choice.

Come join us for two focused days on making our cars and trucks more safe and secure!

# **Ada-Belgium Spring Event**

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Mon, 5 Jun 2017 17:56:01 -0000 Subject: Ada-Belgium Spring 2017 Event, Sun 25 June 2017 Newsgroups: comp.lang.ada, fr.comp.lang.ada, be.comp.programming

Ada-Belgium Spring 2017 Event Sunday, June 25, 2017, 12:00-19:00 Wavre area, south of Brussels, Belgium including at 15:0 2017 Ada-Belgium General Assembly and at 16:00

Ada Round-Table Discussion <http://www.cs.kuleuven.be/~dirk/adabelgium/events/local.html>

bergium/events/local.ntml>

### Announcement

The next Ada-Belgium event will take place on Sunday, June 25, 2017 in the Wavre area, south of Brussels.

For the 10th year in a row, Ada-Belgium decided to organize their "Spring Event", though strictly speaking it will already be summer then ;-), which starts at noon, runs until 7pm, and includes an informal lunch, the 24th General Assembly of the organization, and a round-table discussion on Ada-related topics the participants would like to bring up.

### Schedule

- 12:00 welcome and getting started (please be there!)

- 12:15 informal lunch

- 15:00 Ada-Belgium General Assembly

- 16:00 Ada round-table + informal discussions

- 19:00 end

### **Participation**

Everyone interested (members and nonmembers alike) is welcome at any or all parts of this event.

For practical reasons registration is required. If you would like to attend, please send an email before Wednesday, June 21, 21:00, to Dirk Craeynest <Dirk.Craeynest@cs.kuleuven.be> with the subject "Ada-Belgium Spring 2017 Event", so you can get precise directions to the place of the meeting. Even if you already responded to the preliminary announcement, please reconfirm your participation ASAP.

If you are interested to join Ada-Belgium, please register by filling out the 2017 membership application form[1] and by paying the appropriate fee before the General Assembly. After payment you will receive a receipt from our treasurer and you are considered a member of the organization for the year 2017 with all member benefits[2]. Early enrollment ensures you receive the full Ada-Belgium membership benefits (including the Ada-Europe indirect membership benefits package). As mentioned at earlier occasions, we have a limited stock of documentation sets and Ada related CD-ROMs that were distributed at previous events, as well as back issues of the Ada User Journal[3]. These will be available on a first-come first-serve basis at the General Assembly for current and new members. (Please indicate in the above-mentioned registration e-mail that you're interested, so we can bring enough copies.)

[1] http://www.cs.kuleuven.be/~dirk/ ada-belgium/forms/member-form17.html

[2] http://www.cs.kuleuven.be/~dirk/ ada-belgium/member-benefit.html

[3] http://www.ada-europe.org/auj/home/

### Informal lunch

The organization will provide food and beverage to all Ada-Belgium members. Non-members who want to participate at the lunch are also welcome: they can choose to join the organization or pay the sum of 15 Euros per person to the Treasurer of the organization.

### General Assembly

All Ada-Belgium members have a vote at the General Assembly, can add items to the agenda, and can be a candidate for a position on the Board[4]. See the separate official convocation[5] for all details.

[4] http://www.cs.kuleuven.be/~dirk/ ada-belgium/board/

[5] http://www.cs.kuleuven.be/~dirk/ ada-belgium/events/17/ 170625-abga-conv.html

### Ada Round-Table Discussion

As in recent years, we plan to keep the technical part of the Spring event informal as well. We will have a round-table discussion on Ada-related topics the participants would like to bring up. We invite everyone to briefly mention how they are using Ada in their work or non-work environment, and/or what kind of Ada-related activities they would like to embark on. We hope this might spark some concrete ideas for new activities and collaborations.

### **Directions**

To permit this more interactive and social format, the event takes place at private premises in the Wavre area, south of Brussels. As instructed above, please inform us by e-mail if you would like to attend, and we'll provide you precise directions to the place of the meeting. Obviously, the number of participants we can accommodate is not unlimited, so don't delay...

Looking forward to meet many of you!

Dirk Craeynest, President Ada-Belgium

Dirk.Craeynest@cs.kuleuven.be

### Acknowledgements

We would like to thank our sponsors for their continued support of our activities: AdaCore, Atos, Esterline, and KU Leuven

(University of Leuven)

If you would also like to support Ada-Belgium, find out about the extra Ada-Belgium sponsorship benefits:

http://www.cs.kuleuven.be/~dirk/ ada-belgium/member-benefit.html# sponsor

# Ada-Europe 2017

From: Dirk Craeynest

<dirk@cs.kuleuven.be> Date: Tue, 6 Jun 2017 04:29:01 -0000 Subject: Press Release - Reliable Software Technologies, Ada-Europe 2017 Newsgroups: comp.lang.ada,

fr.comp.lang.ada, comp.lang.misc

FINAL Call for Participation

\*\*\* UPDATED Program Summary \*\*\*

22nd International Conference on Reliable Software Technologies - Ada-Europe 2017

12-16 June 2017, Vienna, Austria

http://www.ada-europe.org/ conference2017

\*\* Check out tutorials and workshop! \*\*

\*\*\* Full Program available on conference web site \*\*\*

\*\*\* Online proceedings available at event \*\*\*

\*\*\* Register now! \*\*\*

### Press release:

22nd Ada-Europe Conference on Reliable Software Technologies

International experts meet in Vienna

Vienna, Austria (6 June 2017) - TU Vienna and Ada-Europe organize from 12 to 16 June 2017 the "22nd International Conference on Reliable Software Technologies - Ada-Europe 2017" in Vienna, Austria. The event is organized in cooperation with the Ada Resource Association (ARA), and with ACM's Special Interest Groups on Ada (SIGAda) and on Programming Languages (SIGPLAN).

The Ada-Europe series of conferences has over the years become a leading international forum for providers, practitioners and researchers in reliable software technologies. These events highlight the increased relevance of Ada in general, and in safety- and securitycritical systems in particular, and provide a unique opportunity for interaction and collaboration between academics and industrial practitioners.

This year's conference offers two days of parallel tutorials, a workshop, three keynotes, a full technical program of refereed papers and industrial presentations, an industrial exhibition and vendor presentations, and a social program.

Eight excellent tutorials on Monday and Friday cover a broad range of topics: Introduction to SPARK 2014; Ada on ARM Cortex-M, a Zero-Run-Time Approach; Software Measurement for Dependable Software Systems; Real-Time Parallel Programming with the UpScale SDK; Using Gnoga for Desktop/Mobile GUI and Web development in Ada; Frama-C, a Collaborative Framework for C Code Verification; On beyond ASCII: Characters, Strings, and Ada 2012; Modular Open System Architecture for Critical Systems.

In addition, on Friday the conference hosts for the 4th consecutive year the International Workshop on "Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering" (De-CPS 2016), now with a focus on "Transportation of the Future".

Three eminent keynote speakers have been invited to open each day of the core conference program.

Giovanni Battista Gallus (Array, Italy), in "The laws of robotics and autonomous vehicles may be much more than three, but don't panic... yet", will talk about the future European legal framework, which is relevant for the development of autonomous vehicles, and especially programming issues.

Thomas Henzinger (IST, Austria), in "Behavioral Software Metrics", will show how the classical satisfaction relation between programs and requirements can be replaced by quantitative preference metrics that measure the "fit" between programs and requirements.

Kay Römer (TU Graz, Austria), in "Dependable Internet of Things", will introduce the Dependable Things research center at TU Graz and present recent results on improving the dependability of wireless communication and localization, embedded computing, and networked control for the Internet of Things.

The technical program presents 14 refereed and carefully selected papers on the latest research, new tools, applications and industrial practice and experience, a collection of 9 industrial presentations reflecting current practice and challenges, 4 presentations and a discussion in a special panel session on "The Future of Safety-Minded Languages", and vendor presentations. Springer Verlag publishes all peer-reviewed papers in the proceedings of the conference, as LNCS

69

Vol. 10300. The remainder of the proceedings will be published in the Ada User Journal, the quarterly magazine of Ada-Europe.

The industrial exhibition opens Tuesday morning and runs until the end of Thursday afternoon. Exhibitors include AdaCore, PTC Developer Tools, Rapita Systems, VectorCAST, and Ada-Europe.

The social program includes a Welcome Reception plus robotics presentations on Tuesday evening at "TU the Sky"; its terraces at the top of TU Vienna's buildings offer a terrific view on the city. On Wednesday evening there will be a Vienna bus tour, followed by the traditional Ada-Europe Conference Banquet, held at a very famous "Heuriger". Each day, coffee breaks in the exhibition area and sit-down lunches offer ample time for interaction and networking.

The Best Paper Award will be presented during the Conference Banquet, the Best Presentation Award during the Closing session.

The conference is hosted by TU Vienna at Palais Eschenbach, which is located near the center of Vienna and can easily be accessed by metro.

The full program is available on the conference web site. Online registration is still possible.

Latest updates:

The 16-page "Final Program" is available at http://www.ada-europe.org/ conference2017/ AE2017\_final\_program.pdf

Check out the 8 tutorials in the PDF program, or in the schedule at http://www.ada-europe.org/ conference2017/tutorials.html.

Registration fees are very reasonable and the registration process is done on-line. Don't delay! For all details, select "Registration" at http://www.ada-europe.org/ conference2017 or go directly to https://adaeurope.upv.es/index.html.

For those who can't attend the full conference, note that Wednesday 14 June is "Meet Ada-Europe day!", and single day registration is discounted.

The proceedings, published by Springer Verlag as Lecture Notes in Computer Science Vol. 10300, are already available online. See https://link.springer.com/ book/10.1007/978-3-319-60588-3. A printed copy is included in every full conference registration.

Help promote the conference by advertising for it! http://www.ada-europe.org/ conference2017/promotion.html. Put up the poster at http://www.ada-europe.org/ conference2017/picts/AE2017\_poster.png Recommended Twitter hashtags: #AdaEurope and/or #AdaEurope2017.

For the latest information consult the conference web site http://www.adaeurope.org/conference2017.

# Ada-related Resources

# RosettaCode

From: Alejandro R. Mosteo <alejandro@mosteo.com> Date: Fri, 10 Feb 2017 17:51:56 +0100 Subject: Bernoulli numbers at RosettaCode Newsgroups: comp.lang.ada

While reading on the first algorithm attributed to our favorite lady, I saw that there's no Ada implementation at RosettaCode. Just in case someone has some time in their hands to fix this omission.

https://rosettacode.org/wiki/ Bernoulli\_numbers

Funnily enough, the Pascal impl is taken from an Ada one:

https://marquisdegeek.com/code\_ada99

# **Social Network Site**

From: Tomek Walkuski <tomek.walkuski@gmail.com> Date: Thu, 6 Apr 2017 01:01:35 -0700 Subject: [ANN] Ada community on Gitter Newsgroups: comp.lang.ada

Hi, I've recently started Ada developers community on Gitter, feel free to join if you want!

https://gitter.im/ada-lang

### **Repositories of Open Source** Software

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Mon Jun 26 2017 Subject: Repositories of Open Source software GitHub: 907 repositories [1] 431 developers [1] 850 issues Rosetta Code: 635 examples [2] 32 developers [3] 0 issues [4] Sourceforge: 258 repositories [5] BlackDuck OpenHUB: 210 projects [6] Bitbucket: 78 repositories [7] OpenDO Forge: 24 projects [8] [8] 521 developers Codelabs: 21 repositories [9] AdaForge: 8 repositories [10] [1] https://github.com/search? q=language%3AAda&type=Repositories

[2] http://rosettacode.org/wiki/ Category:Ada

[3] http://rosettacode.org/wiki/ Category:Ada\_User

[4] http://rosettacode.org/wiki/Category: Ada\_examples\_needing\_attention

[5] http://sourceforge.net/directory/ language%3Aada/

[6] https://www.openhub.net/ tags?names=ada

[7] https://bitbucket.org/repo/ all?name=ada&language=ada

[8] https://forge.open-do.org/[9] http://git.codelabs.ch/

[10] http://forge.ada-ru.org/adaforge

[See also "Repositories of Open Source Software", AUJ 37-4, p. 184. —sparre]

# Ada on Social Media

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Tue Jun 27 2017 Subject: Ada on Social Media Ada groups on various social media:

- Reddit: 998 readers [2]

- StackOverflow: 811 followers [3]

- Google+: 766 members [4]

- Freenode 85 participants [5]

- Gitter: 48 people [6]

- Twitter: 10 tweeters [7]

[1] https://www.linkedin.com/ groups?gid=114211

[2] http://www.reddit.com/r/ada/

[3] http://stackoverflow.com/questions/ tagged/ada

[4] https://plus.google.com/communities/ 102688015980369378804

[5] #Ada on irc.freenode.net

[6] https://gitter.im/ada-lang

- [7] https://twitter.com/search?

- f=realtime&q=%23AdaProgramming

- [See also "Ada on Social Media", AUJ

- [1] 37-4, p. 184. —sparre]

# Ada-related Tools

# Ada for Automation

From: Stéphane Los

<new.stephane.los@gmail.com> Date: Thu, 23 Mar 2017 08:10:52 -0700 Subject: "Ada for Automation" Demo Portal Newsgroups: comp.lang.ada

Thanks to Gnoga (D. Botton) and Simple Components (D. Kazakov), Ada for Automation can offer a Demo Portal so that you can play with it without having to install / build anything.

### It features:

- applications running in the cloud and using Modbus TCP protocol to communicate thanks to libmodbus binding

- and applications using PROFINET IO protocol thanks to Hilscher cifX 50-RE board and netRAPID module.

Here is the link to it:

http://ada4automation.slo-ist.fr/

[Project homepage: http://slo-ist.fr/ada4autom]

### Pixmap to Screen

### From: LaeMing Ai

<laeming@exemail.com.au> Date: Sat, 25 Mar 2017 18:01:59 -0700 Subject: Best way to put an array-based pixmap on a screen? Newsgroups: comp.lang.ada

I am hoping to learn some Ada with an explicit interest in simple software 3D rendering (i.e.: writing the render code in Ada, NOT calling external libraries such as OpenGL). I want to set up a shim between my Ada environment and my Linux Desktop to facilitate monitoring my output, without having to mess about with the daunting (I quickly found) task of interfacing to SDL or GTK+!

All I really want to see from my code's perspective is a 2D array of 32-bit pixel values that I can manipulate from my developing Ada code, and not have to worry about the intricacies of window managers. Is it possible to get help constructing a project template providing the following:

- Function to create a non-resizable X11 window of dimensions N high by 2N wide (N is nominally valued at 512, but could be any value of 2<sup>x</sup> above 256).

- Callback for if the above window's close box is activated, to terminate the program.

- Function to copy an array of 2N by N of 32 bit values (8:Red 8:Green 8:Blue 8:ignored) to the above window.

At this stage I am not concerned with input to the window (other than the close box terminating the application, would be nice).

Packing it all into a single source file that I can put to the side and largely ignore would be nice too!

I particularly don't want event loops, or anything else dragged in from outside the Ada environment if at all possible - the point of using Ada is to learn to do all that /in/ Ada! :-)

I have played around with some AdaGTK examples but keep getting bogged down.

From: Dirk Craeynest <dirk@cs.kuleuven.be> Date: Sun, 26 Mar 2017 09:35:11 -0000 Subject: Re: Best way to put an array-based pixmap on a screen? Newsgroups: comp.lang.ada

> [...]

You might want to take a look at the code Ludovic Brenta provided for his series of presentations in several Ada Developer Rooms at past FOSDEM events. He used a minimal Ada interface to the xcb-library to do exactly that, i.e. to display a 2D array of pixel values on the screen.

For more info, see:

Ada DevRoom @ FOSDEM 2013

Ada Tasking: Multithreading Made Easy

https://www.cs.kuleuven.be/~dirk/ ada-belgium/events/13/

130203-fosdem.html#multithreading Ada DevRoom @ FOSDEM 2014

Ada Task Pools: Multithreading Made Easy

https://www.cs.kuleuven.be/~dirk/ ada-belgium/events/14/ 140201-fosdem.html#multithreading

video registration:

http://ftp.belnet.be/FOSDEM/2014/ K4601/Saturday/Ada\_Task\_Pools\_ Multithreading\_Made\_Easy.webm

Ada DevRoom @ FOSDEM 2015

Multithreading Made Easy, part 3 -Bounded Work Queues

https://www.cs.kuleuven.be/~dirk/ ada-belgium/events/15/ 150131-fosdem.html#multithreading

video registration (very low sound level):

https://ftp.heanet.ie/mirrors/ fosdem-video/2015/devroom-ada/ multithreading\_\_CAM\_ONLY.mp4>

source distribution (latest version):

https://www.cs.kuleuven.be/~dirk/ ada-belgium/events/15/150131fosdem/06-ada-multithreading.tgz

From: reinert <reinkor@gmail.com> Date: Sun, 26 Mar 2017 06:27:58 -0700 Subject: Re: Best way to put an array-based pixmap on a screen? Newsgroups: comp.lang.ada

In case it could be useful, here is a simple test program using GLOBE\_3D (texture). I just started to use GLOBE\_3D for fast (interactive) video-like rendering

(programming in Ada): with Text\_IO; use Text\_IO; with GL, GLUT.Devices; use GL, GLUT.Devices; procedure a1 is

> package Flt\_lo is new Text\_IO.Float\_lo(Float); package Int\_lo is new Text\_IO.Integer\_lo(Integer);

use Flt\_lo,Int\_lo;

GLUT\_Problem: **exception**; **use** GLUT;

texDat : **array** (1..64) **of** aliased gl.ushort; texDat\_Ptr : **constant** pointer := to\_Pointer(texDat(texDat'First) 'unchecked\_access);

tex : aliased GL.uint;

tex\_Ptr : **constant** GL.uintPtr := tex'unchecked\_access;

n,k : Integer := 1;

### begin

glut.Init; glut.SetOption(GLUT. ACTION\_ON\_WINDOW\_CLOSE. GLUT.ACTION\_GLUTMAINLOOP RETURNS); glut.InitDisplayMode(GLUT.DOUBLE or GLUT.RGB or GLUT.DEPTH ); glut.InitWindowSize(800,600); glut.InitWindowPosition(1, 1); if glut.CreateWindow( "Tittel A") = 0 then raise GLUT\_Problem; end if; glut.Devices.Initialize; n := texDat'First; for i in 1..8 loop for j in 1..8 loop k := (if i = j then 1 else 0);k := (if (i + j) mod 2 = 0)then 1 else 0); texDat(n) := gl.ushort(k\*100 + 100);n := n + 1; end loop;

end loop;

gl.GenTextures(1, tex\_Ptr); gl.BindTexture(GL.TEXTURE\_2D, tex);

- gl.TexParameter(GL.TEXTURE\_2D, GL.TEXTURE\_MIN\_FILTER, GL.NEAREST); gl.TexParameter(GL.TEXTURE\_2D, GL.TEXTURE\_MAG\_FILTER, GL.NEAREST);

- gl.TexImage2D(GL.TEXTURE\_2D, 0, GL.LUMINANCE, 8, 8, 0, GL.LUMINANCE\_ALPHA, GL\_UNSIGNED\_BYTE, texDat\_Ptr);

gl.BindTexture(GL.TEXTURE\_2D, 0); gl.MatrixMode(GL.PROJECTION); gl.Ortho(0.0, 800.0, 0.0, 600.0, -1.0, 1.0); gl.MatrixMode(GL.MODELVIEW); gl.ClearColor(1.0, 1.0, 1.0, 0.0); gl.Clear(GL.COLOR\_BUFFER\_BIT); gl.BindTexture(GL.TEXTURE\_2D, tex); gl.Enable(GL.TEXTURE\_2D); gl.Color(1.0, 1.0, 1.0, 1.0); gl\_Begin(QUADS); gl.TexCoord(0.0, 0.0); gl.Vertex(100, 100); gl.TexCoord(0.0, 1.0); gl.Vertex(100, 500); gl.TexCoord(1.0, 1.0); gl.Vertex(500, 500); gl.TexCoord(1.0, 0.0); gl.Vertex(500, 100); gl\_End;

gl.Disable(GL.TEXTURE\_2D); gl.BindTexture(GL.TEXTURE\_2D, 0); gl.Flush; glut.SwapBuffers;

Delay 10.0;

### end a1;

[See also "GLOBE\_3D", AUJ 37-4, p. 186. —sparre]

### GNATCOLL

From: Emmanuel Briot <briot@adacore.com> Date: Tue Apr 4 2017 Subject: New strings package in GNATCOLL URL: http://blog.adacore.com/new-stringspackage-in-gnatcoll

GNATCOLL has recently acquired two new packages, namely GNATCOLL.Strings and GNATCOLL.Strings\_Impl. The latter is a generic package, one instance of which is provided as GNATCOLL.Strings.

But why a new strings package? Ada already has quite a lot of ways to represent and manipulate strings, is a new one needed?

This new package is an attempt at finding a middle ground between the standard String type (which is efficient but inflexible) and unbounded strings (which are flexible, but could be more efficient).

GNATCOLL.Strings therefore provides strings (named XString, as in extendedstrings) that can grow as needed (up to Natural'Last, like standard strings), yet are faster than unbounded strings. They also come with an extended API, which includes all primitive operations from unbounded strings, in addition to some subprograms inspired from GNATCOLL.Utils and the Python and C++ programming languages.

### Small string optimization

GNATCOLL.Strings uses a number of tricks to improve on the efficiency. The most important one is to limit the number of memory allocations. For this, we use a trick similar to what all C++ implementations do nowadays, namely the small string optimization.

### [...]

[See also "GNATColl", AUJ 37-3, p. 128. —sparre]

### GNATColl.JSON Support Packages

From: Per Sandberg

JSON-Support for most types in the Ada.Containers hierarchy.

- Simplify mapping of one-dimensional containers

- Added very crude code generator.

https://github.com/persan/gnatcolljson/releases/tag/gnatcoll-JSON-v1.1.0

[See also "GNATColl.JSON Support Packages", AUJ 37-2, p. 75. —sparre]

### Simple Components

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Mon, 17 Apr 2017 21:54:13 +0200 Subject: ANN: Simple Components for Ada v4.21

Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, multiple connections server/client designing tools.

http://www.dmitry-kazakov.de/ada/ components.htm

The new version extends WebSocket support. It introduces a HTTP server implementation or base type capable to handle connections running over WebSockets instead of normal sockets.

No changes in the implementation of existing connection objects required. For example the same MQTT\_Connection object implementing the MQTT protocol can be used this way, and so providing MQTT over WebSocket.

[See also "Simple Components", AUJ 38-1, p. 4. —sparre]

### Ada 2005 Math Extensions

From: Simon Wright <simon@pushface.org> Date: Thu, 27 Apr 2017 11:52:40 +0100 Subject: ANN:Ada 2005 Math Extensions 20170427

Newsgroups: comp.lang.ada

The latest release of this project[1] is available at Sourceforge[2].

Changes:

- The procedure declaration for the generalized real eigensystem solution was wrong: the eigenvectors should have been complex. This has been corrected.

- The tests now succeed with LAPACK 3.2 to 3.4, and 3.5 to 3.7 (the Fortran results for Real Generalized Eigensystems changed at 3.5). This may be a symptom of some deeper problem, to be investigated.

- The package can be installed with the compiler by 'make install'.

- The code is compatible with GNAT GPL 2016 and FSF GCC 7 (a minor change was required to avoid a compilation warning).

Windows users: there's now a version of LAPACK for Windows[3]; I haven't tried it, but it has to be an improvement on the situation in 2013!

[1] http://gnat-math-extn.sourceforge.net/ index.html/

[2] https://sourceforge.net/projects/ gnat-math-extn/files/20170427/

[3] http://icl.cs.utk.edu/ lapack-for-windows/lapack/

[See also "Ada 2005 Math Extensions", AUJ 34-3, p. 138. —sparre]

From: Simon Wright <simon@pushface.org> Date: Tue, 09 May 2017 13:49:01 +0100 Subject: Re: ANN:Ada 2005 Math Extensions 20170427

Newsgroups: comp.lang.ada

> So if understand well, this is an extension of the Ada Arrays in rowmajor order, right? How is it using Lapack since Fortran has column-major order for its matrices?

By transposing input matrices before handing over to LAPACK, and transposing the results before handing back to the caller.

> I have also seen different projects that use Lapack:

> - Ada Lapack: https://sourceforge.net/projects/adalapack/

This is a translation of the Fortran library to Ada, and uses native Ada ordering (row-major).

> - AdaLAPACK:

https://sourceforge.net/projects/adalapa ck/

This is a binding, and its interface is explicitly in terms of Fortran-convention objects; for example,

type Fortran\_Real\_Matrix is array (Fortran\_Integer range <>, Fortran\_Integer range <>) of Real; pragma Convention (Fortran, Fortran\_Real\_Matrix); procedure SGEEV (JOBVL : Character; JOBVR : Character; N : Fortran\_Integer; A : Fortran\_Real\_Matrix; LDA : Fortran\_Real\_Vector; WR : out Fortran\_Real\_Vector; WI : out Fortran\_Real\_Vector; VL : out Fortran\_Integer; VR : out Fortran\_Integer; WORK : in out Fortran\_Real\_Vector; LWORK : Fortran\_Integer; INFO : out Fortran\_Integer;

**pragma** Import (Fortran, SGEEV, "sgeev\_");

# **GNAT and UTF-8**

From: Simon Wright

<simon@pushface.org> Date: Sun, 30 Apr 2017 18:10:42 +0100 Subject: GNAT vs UTF-8 source file names Newsgroups: comp.lang.ada

ACATS 4.1 test C250002 involves unit names with UTF-8 characters (the source has the correct UTF-8 BOM, the relevant unit is named C250002\_Z where Z is actually UTF-8 C381, latin capital letter a with acute; gnatchop correctly generates a source file with the BOM and name c250002\_z where z is actually UTF-8 C3A1, latin small letter a with acute).

On compiling, the compiler (GNAT GPL 2016, FSF GCC 7.0.1) fails to find the file; it says e.g.

GNATMAKE GPL 2016 (20160515-49) Copyright (C) 1992-2016, Free Software Foundation, Inc. gcc -c -l../../../support -gnatW8 c250002.adb gcc -c -l../../../support -gnatW8 c250002\_0.ads End of compilation

gnatmake: "c250002\_?.adb" not found

I suspect that the problem is down to the .ali file. macOS says

\$ file -I \*

c250002.adb: text/plain; charset=utf-8 c250002.ali: text/plain; charset= unknown-8bit c250002.lst: text/plain; charset=us-ascii c250002.o: application/x-mach-binary; charset=binary

c250002\_0.ads: text/plain; charset=utf-8 c250002\_á.adb: text/plain; charset=utf-8 c250002\_á.ads: text/plain; charset=utf-8

(the last 2 were actually a-acute on the terminal) but the .ali file is confused about whether the representation of the a-acute is C3A1 (good, assuming it gets interpreted as UTF-8 without a BOM) or E3A1 (bad), particularly about the corresponding .ali file name.

Any thoughts? is this a known issue?

(C250001, which has BOMs and UTF-8 identifiers but not file names, works fine with no -gnatW8 messing)

From: Simon Wright <simon@pushface.org> Date: Sat, 17 Jun 2017 18:20:28 +0100 Subject: Re: GNAT vs UTF-8 source file names

Newsgroups: comp.lang.ada

> [...]

PR ada/81114 refers[1].

It turns out that this failure occurs on Windows and macOS. The problem is that GNAT smashes the file name to lower case if it knows that the file system is case-insensitive (using an ASCII tolower, so of course 'smash' is the right word if there are UTF-8 characters in there).

There is an undocumented environment variable that affects this:

\$

GNAT\_FILE\_NAME\_CASE\_SENSITIVE=1 gnatmake c250002 gcc -c c250002.adb gcc -c c250002\_á.adb gnatbind -x c250002.ali gnatlink c250002.ali \$ ./c250002

,... C250002 ACATS 4.1 17-06-17 18:05:55 ---- C250002 Check that characters above ASCII.Del can be used in identifiers, character literals and strings.

- C250002 C250002\_0.TAGGED\_Ã \_ID. ==== C250002 PASSED ============

I wonder why, if the FS is caseinsensitive, GNAT bothers at all? (there was, I think, some remark about detecting whether two filenames represented different files).

What do people who actually need to use international character sets do about this? Do you just avoid using international characters in Ada unit names? Or have I just missed the relevant part of the manual?

[1] https://gcc.gnu.org/bugzilla/ show\_bug.cgi?id=81114

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Tue, 27 Jun 2017 15:22:11 +0200 Subject: Re: GNAT vs UTF-8 source file names

Newsgroups: comp.lang.ada

> What do people who actually need to use international character sets do about this? [...]

One of my customers simply has a policy saying that all identifiers have to be in English (the policy doesn't say if it should be American English or proper English), and thus neatly works around the problem.

This reminds me that Jean-Pierre Rosen had a very entertaining tutorial on glyphs,

graphemes, alphabets, characters, character sets, encodings, etc. at Ada-Europe 2017 in Vienna. We learnt all kinds of stuff we really don't want to know and worry about. ;-)

From: Niklas Holsti <niklas.holsti@tidorum.fi> Date: Wed, 28 Jun 2017 00:45:55 +0300 Subject: Re: GNAT vs UTF-8 source file names

Newsgroups: comp.lang.ada

> What do people who actually need to use international character sets do about this? [...]

I use ISO-Latin-1 identifiers in some Ada programs written in a Finnish context, using the Finnish alphabet letters ä, ö, and sometimes the Swedish å. Worked OK for me until \*some\* of the file systems I use changed from file names with 8-bit characters to UTF-8 file names, after which CVS was quite messed up. I have since limited myself to ASCII in all identifiers that become file name parts in GNAT's file-naming convention, but I still use ISO Latin 1 for other identifiers.

> [...] all identifiers have to be in English [...] works around the problem.

Only if you stick to "modern" English spelling. Otherwise you could have, for example,

package Coördinates is ...

## **DB\_Maker**

From: Jeffrey R. Carter

<jrcarter@acm.org>

Date: Tue, 2 May 2017 22:19:41 +0200

Subject: DB\_Maker

Newsgroups: gmane.comp.lang.ada.gnoga

A generic for creating simple DBs (one table in an RDBMS) with PragmARC.Persistent\_Skip\_List\_Unboun ded and a Gnoga UI.

https://github.com/jrcarter/DB\_Maker

Includes Movies, a demo program, that could be used to catalog your extensive collection of BetaMax videotape cassettes.

### **Question: Z-Wave Support?**

From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Wed, 3 May 2017 18:36:12 +0200 Subject: Ada Z-wave support Newsgroups: comp.lang.ada

Is there serious interest in having Z-wave stack on top of

GNAT.Serial\_Communications?

(I studied Z-ware protocol a bit. It is overly complicated and has multiple design issues that prevent having a straightforward protocol stack implementation. Existing implementations like openzwave are correspondingly messy. The protocol itself [serial API] is not openly available and must be reverse engineered. All that will require considerable efforts and nothing will work at first.)

[See also "Open Z Wave", AUJ 37-1, p. 15. —sparre]

# Qt5Ada

From: Leonid Dulman <leonid.dulman@gmail.com> Date: Wed, 31 May 2017 22:39:06 -0700 Subject: Announce : Qt5Ada version 5.9.0 (541 packages) release 01/06/2017 free edition Newsgroups: comp.lang.ada

Qt5Ada is Ada-2012 port to Qt5 framework (based on Qt 5.9.0 final) Qt5ada version 5.9.0 open source and qt5c.dll,libqt5c.so(x64) built with Microsoft Visual Studio 2015 in Windows, gcc x86-64 in Linux. Package tested with gnat gpl 2012 ada compiler in Windows 32bit and 64bit , Linux x86-64 Debian 8.5

It supports GUI, SQL, Multimedia, Web, Network, Touch devices, Sensors, Bluetooth, Navigation and many

others thinks.

Changes for new Qt5Ada release:

Added packages for modules:

QJson,QBson,QMongo (Mongo DB) modules support.

My configuration script to build Qt 5.9.0 is: configure -opensource -release nomake tests -opengl dynamic -qt-zlib qt-libpng -qt-libjpeg -openssl-linked OPENSSL\_LIBS="-lssleay32 -llibeay32" -plugin-sql-mysql -plugin-sql-odbc plugin-sql-oci -icu -prefix "e:/Qt/5.9"

As a role ADA is used in embedded systems, but with QTADA(+VTKADA) you can build any desktop applications with powerful 2D/3D rendering and imaging (games, animations, emulations) GUI, Database connection, server/client, Internet browsing, Modbus control and many others thinks.

Qt5Ada and VTKAda for Windows, Linux (Unix) is available from https://drive.google.com/ folderview?id=0B2QuZLoeyiPbmNQR183M1dTRVE&usp=sharing (google drive. It can be mounted as virtual drive or directory or viewed with Web Browser)

The full list of released classes is in "Qt5 classes to Qt5Ada packages relation table.docx" VTKAda version 7.1.0 is based on VTK 7.1.0 (OpenGL2) is fully compatible with Qt5Ada 5.9.0

I hope Qt5Ada and VTKAda will be useful for students, engineers, scientists and enthusiasts With Qt5Ada you can build any applications and solve any problems easy and quickly.

[See also "Qt5Ada", AUJ 38-1, p. 6. —sparre]

## ASIS2XML

From: Simon Wright <simon@pushface.org> Date: Sat, 03 Jun 2017 15:25:23 +0100 Subject: ASIS2XML 20170603 Newsgroups: comp.lang.ada

Minor release, at

https://sourceforge.net/projects/asis2xml/files/20170603/

- Compatible with GNAT GPL 2016, FSF GCC 6, 7.

- Fixes bug #3, Package head components missing.

- Updates Makefile, add install target.

[See also "ASIS2XML", AUJ 35-2, p. 80. —sparre]

# ArchiCheck

From: Lionel Draghi <Lionel Draghi@Ada

<Lionel.Draghi@Ada-France.org> Date: Thu, 8 Jun 2017 00:06:01 +0200 Subject: Ann: ArchiCheck v0.1 Newsgroups: comp.lang.ada

Archicheck is a simple tool to describe and enforce architecture/design decision that are not easily checked by languages and compilers.

This code was written twelve years ago, and even announced on comp.lang.ada (http://groups.google.com/group/comp.lan g.ada/browse\_thread/thread/4a195a443fce 793e/41bb2cb527464bab?q=comp.lang.ad a+example+of+layered+software#41bb2c b527464bab) in November 2005, but never released.

Here it is, essentially as it was in 2005, build in the same environment (Darcs, Gnat, NaturalDocs, Dia, OpenToken, etc.).

This tool was written because of my frustration that simple design decision where not complied with.

A classical and recurring case was that for a bug fix, someone adds a "with" in the code, that created a visibility to a package supposed to be in an upper layer.

Few month of such a code spaghettization resulted in subtle elaboration order problems, and obviously in code degradation.

Another classical design decision not so easy to verify is to forbid any dependencies on OS specific code, except in an appointed "portability" package.

Ada couldn't prevent this (not to mention other languages), and I found no external tools able to verify it.

This is why I started the Archicheck project, as a tool that read a text file containing in simple statements the architecture description, and check the code compliance. Consider the my\_rules.txt file:

Presentation\_Layer contains A B C packages

Application\_Layer contains D E F packages

Domain\_Layer contains G H I packages

Presentation\_Layer is a layer over Application\_Layer

Application\_Layer is a layer over Domain\_Layer

Only Hardware\_Abstraction\_Layer can use Interfaces.C

Just put:

archicheck my\_rules.txt -I ./my\_src

in your make file, and that's it.

This is a POC, the code is not at all robust, or even well tested, and it check only Layer rules at this stage (cf. Tests section here:

http://lionel.draghi.free.fr/Archicheck/ index.html).

Any feedback or comment is welcome (even on the tool's name!).

More info on http://lionel.draghi.free.fr/ Archicheck/index.html

From: Randy Brukardt <randy@rrsoftware.com> Date: Wed, 7 Jun 2017 20:04:54 -0500 Subject: Re: ArchiCheck v0.1 Newsgroups: comp.lang.ada

>[...]

pragma Profile

(No\_Implementation\_Extensions);

forbids any dependence on implementation-defined stuff. That eliminates most (not all) sources of nonportable code, it clearly includes targetdependent packages like Ada.Directories.Information. See 13.12.1(9-13/3). By far the best way to avoid OS-specific code is to stick to the language-defined packages!

Of course, you could use an OS-Dependent package of your own design (or one picked up off the Internet), and the language can't possibly help with that. So your tool certainly has value beyond what the language (any language for that matter) can do.

From: Randy Brukardt

<randy@rrsoftware.com> Date: Thu, 8 Jun 2017 22:27:34 -0500 Subject: Re: ArchiCheck v0.1 Newsgroups: comp.lang.ada

[...]

Another item that would help for this sort of thing is

###

which prevents any use of the named package (which doesn't actually have to exist anywhere). For instance,

**pragma** Restrictions (No\_Dependence, GNAT);

prevents any use of package GNAT or any of its children in your program. (Which will get rid of a lot of GNATdefined facilities.)

In your case, one can use it to prevent using various locally defined packages that might not be portable.

# **Ada-related Products**

## State of the Compiler Market

From: John McCabe

<john@mccabe.org.uk>

Date: Wed, 22 Feb 2017 16:26:17 -0800

Subject: State of the compiler market

Newsgroups: comp.lang.ada

I have honestly been searching on Google for this, but I can't easily find out who produces a commercial (or free) compiler for Ada 2012, other than AdaCore. Can anyone give me some pointers please?

I've looked at some compilers I've used in the past but they seem to have stagnated around Ada 95.

Also, are there any modern (i.e. Later than Ada 95) compilers for a MIPS target, or for any DSPs?

From: Per Sandberg

<per.s.sandberg@bahnhof.se>

Date: Thu, 23 Feb 2017 06:16:11 +0100

Subject: Re: State of the compiler market

Newsgroups: comp.lang.ada

[...]

And concerning MIPS there is a open cross built on debian: https://packages.debian.org/sid/devel/ gnat-5-mips-linux-gnu

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Wed, 22 Feb 2017 22:01:56 -0800 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

For Ada 2012 it's probably AdaCore's GNAT only so far.

For Ada 2005 there are some other options - whether they are complete is another question. At least PTC ObjectAda can build correctly a program using maps, containers and the dot notation for objects (e.g. GLOBE\_3D demos).

Here is a compiler list obtained by googling, then filtered over time: http://unzip-ada.sourceforge.net/ #adacomp

From: Joakim Strandberg <joakimds@kth.se>

Date: Thu, 23 Feb 2017 01:01:44 -0800 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada The ICC Ada compiler supports Ada 2005: http://www.irvine.com/

From: Randy Brukardt <randy@rrsoftware.com> Date: Thu, 23 Feb 2017 15:22:28 -0600 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

### > [...]

So far as I know, only AdaCore has a full Ada 2012 compiler.

The next release of Janus/Ada will support a smattering of Ada 2012 features, to go with a smattering of Ada 2007 features, and most (but not quite all) of Ada 95. (Customers should be able to try a preview of this version next month.)

Both PTC compilers (ObjectAda and Apex) are Ada 2005, as is Irvine.

Everything else seems to be stuck on Ada 95.

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Tue, 27 Jun 2017 10:00:25 +0200 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

### >[...]

PTC has announced that they are working on adding Ada 2012 features to PTC ObjectAda.

If I remember the presentation at Ada-Europe 2017 correctly, the first step is aspects, contracts, conditional expressions and expression functions.

From: Luke A. Guest

<laguest@archeia.com> Date: Sun, 26 Feb 2017 00:20:45 +0000 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

### >[...]

This is an issue for us open source people, the idea of a new compiler has been discussed here before. Randy has stated people shouldn't bother, but I disagree as there are reasons to have another one. One reason being that if there isn't an alternative there will be one company monopolising the future of the language and there will be no further work to expand the language into new areas and will continue to stay in aerospace.

If this happens, a new language derived from Ada would need to happen and fast. Again, this has been discussed, see the thread started by David Botton about the getadanow logo competition.

### From: Randy Brukardt

<randy@rrsoftware.com> Date: Sat, 25 Feb 2017 20:26:49 -0600 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

### >[...]

To be fair, I've said people shouldn't bother simply because the odds of it reaching a usable state are near zero. As several people have noted, the parser is the easy part. Figuring out Ada resolution rules, Ada tasking, the Ada optimization rules, and many other things will sap anyone of energy long before they complete it. (Note that we never had an intent to build a full Ada compiler when we started out. We got pushed that way when others got interested. And 35+ years have elapsed...)

I think a better approach would be to convince an existing Ada 95 implementation to go open source and then enhance that to do the things desired (Ada 2020 support, etc.). I'd consider it if (a) there were people truly interested and (b) it was reasonably obvious how to monitize the result (that is, provide enough revenue for living).

### From: Paul Rubin

Date: Fri, 24 Feb 2017 01:32:21 -0800 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

> Could agree on that but a fair question is: How many real compiler-vendors are there for C and C++?

Gcc, Clang, icc, Microsoft, I guess that's all the current C++ that I can think of though there are probably a few more. "Current" for now means the compiler supports C++14 or comes pretty close.

There's plenty of C compilers around, especially in the embedded world. CompCert (compcert.inria.fr) has a formally verified code generator, which has never been done for Ada.

From: Dirk Craeynest

<dirk@cs.kuleuven.be> Date: Sun, 26 Feb 2017 10:14:07 -0000 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

> I think a better approach would be to convince an existing Ada 95 implementation to go open source and then enhance that to do the things desired (Ada 2020 support, etc.).

### Hear, hear!!!

Action for all: Talk to your favorite Ada95/2005 vendor, and ask them about their plans to upgrade to newer Ada features!

From: reinkor <reinkor@gmail.com> Date: Wed, 1 Mar 2017 00:43:40 -0800 Subject: Re: State of the compiler market Newsgroups: comp.lang.ada

I got a bit scared from this discussion since I am investing much time in developing an application in Ada.

Can Adacore's (gnat) public licence safeguard the language is available the coming 10-20 years? I.e. can I stay relaxed? :-)

From: Jacob Sparre Andersen

<jacob@jacob-sparre.dk>

Date: Tue, 27 Jun 2017 10:29:57 +0200

Subject: Re: State of the compiler market

Newsgroups: comp.lang.ada

> [...] can I stay relaxed? :-)

I think you can.

My bet is that Ada will be around at least another 20 years.

At some point we will have accept to break backwards compatibility, but I can't see how and when it will happen.

# RapiTestFramework

From: Rapita Systems Date: Tue May 9 2017 Subject: An early look at RapiTestFramework URL: https://www.rapitasystems.com/ blog/early-look-rapitestframework

We have been hard at work recently developing RapiTestFramework, a new RVS tool that generates and runs unit, integration and system tests on embedded targets or host systems. RapiTestFramework injects test framework code, builds a test harness, runs this on the target and reports results.

RapiTestFramework has come along very well during its early development, and has been used by both the embedded software industry and ourselves (as part of our new software verification services). What's more, we have been working on kits to help you qualify the tool for use in your DO-178B/C or ISO 26262 projects.

In this post, we thought we'd share with you some of the design decisions we made during the development of RapiTestFramework, which led to the strong position the tool is in today.

### Thinking of the future

All of our tools are built to meet the evolving needs of embedded software verification, and RapiTestFramework is no exception. Because these needs change over time, we built RapiTestFramework to be flexible from the outset.

We did this by spending the early design period concentrating on the features we need from the tools that parse source code and inject tests, based on real needs identified from our customers.

By using a bottom-up approach and leaving questions about higher-level features such as the user-interface for later, we could spend the time needed to engineer a flexible tool that will be relevant for years to come.

There are some really exciting features we can implement using

RapiTestFramework, such as data and control coupling and identifying infinite loops in your source code before running it, but you'll have to wait until a future blog post for more on that.

[...

[See also "Highlights from Ada Europe 2016", AUJ 37-3, p. 124. —sparre]

# **ObjectAda**

From: Jacob Sparre Andersen <jacob@jacob-sparre.dk> Date: Tue Jun 13 2017 Subject: Jacob Sparre on Twitter URL: https://twitter.com/Jacob\_Sparre/ status/874657941814730752

PTC announces work on #Ada2012 support in Object Ada. #AdaProgramming #AdaEurope2017

[Slide transcription follows. --sparre]

Ada Products in Development

-----

- Corrections / enhancements to existing product releases

- ObjectAda V10.0 for Windows

- o Visual Studio 2017 & windows 10 SDK

- o Phased introduction of Ada 2012 support

- + V10.0: new expression forms, Aspects & Contracts

[End slide transcription. --sparre]

[See also "Apex Ada, Object Ada and Ada World", AUJ 37-1, p. 17. —sparre]

# Ada and Operating Systems

### **Debian: gprinstall?**

From: Simon Wright

<simon@pushface.org> Date: Tue, 14 Feb 2017 17:01:17 +0000 Subject: Debian & gprinstall Newsgroups: comp.lang.ada

Has anyone devised a setup to use gprinstall to install a library to match the Debian Ada Policy?

I don't care so much (perhaps I should) about getting the so names right, but I'd like at least to get the library GPRs installed where Debian looks for them.

At the moment, on jessie, gprinstall installs:

Sources in /usr/include/<library>/

ALI files in /usr/lib/<library>/

- Objects in /usr/lib/<library>/

- (for a relocatable library, a symlink to the so in /usr/lib/<library>/ is put in /usr/lib)

GPRs in /usr/share/gpr/

and at the very least GPRs should be in /usr/share/ada/adainclude/. That's easy enough using

--project-dir=share/ada/adainclude, but what about the other directories? (they need to be reasonably out of the way of anywhere that Debian would install software). From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de> Date: Tue, 14 Feb 2017 18:57:10 +0100 Subject: Re: Debian & gprinstall Newsgroups: comp.lang.ada

>[...]

But gprinstall cannot follow policies of all Linux flavors. Fedora's policy is very different, e.g. it has a system gpr project to include into the library project and get directories' paths from there.

If indeed gprinstall were to care of the Linux target I would suggest to generate a proper project installation file, \*.deb, \*.rpm and use it in the standard system installer.

I wrote an extremely ugly bash script to generate Debian and Fedora project files. It would be a great help if gprinstall did this (and \*msi setup for Windows). Not that I believe that to happen...

From: Simon Wright

<simon@pushface.org> Date: Tue, 14 Feb 2017 21:30:32 +0000 Subject: Re: Debian & gprinstall Newsgroups: comp.lang.ada

>[...]

I only want a set of switches that will make gprinstall do something that works on Debian with the system compiler (no problem if using GNAT GPL, of course, since the default setup is what GNAT GPL expects) and doesn't trample over other software.

Is the Fedora equivalent of the Debian Ada policy written up anywhere?

>[...]

But I'm not going to distribute binary library packages for any Linux flavours. So I don't need to understand .deb, .rpm, etc etc. I just want the \_source\_ packages to be easily installable.

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 15 Feb 2017 09:44:17 +0100 Subject: Re: Debian & gprinstall Newsgroups: comp.lang.ada

>[...]

I think a natural way would be if AdaCore added package Installer to the project file which could contain variables and commands to gprinstall.

> Is the Fedora equivalent of the Debian Ada policy written up anywhere?

https://fedoraproject.org/wiki/ Packaging:Ada

> [...] I just want the \_source\_ packages to be easily installable.

Sure, but there is no easy way, not any more. I mean, with all these multi-arch systems and cross compilers it becomes more and more complicated. So maybe in the end it would be easier to do it in a hard way... From: Simon Wright <simon@pushface.org> Date: Wed, 15 Feb 2017 09:29:48 +0000 Subject: Re: Debian & gprinstall Newsgroups: comp.lang.ada

[...] See package Install in

http://docs.adacore.com/gprbuild-docs/ html/gprbuild\_ug/ gnat\_project\_manager.html#packages Not sure when it was introduced.

# Mac OS X: AdaControl

From: Jean-Pierre Rosen <rosen@adalog.fr> Date: Thu, 30 Mar 2017 07:21:36 +0200 Subject: AdaControl available for MacOS Newsgroups: comp.lang.ada

Thanks to Pascal Pignard, an executable distribution of the current version of AdaControl is available from AdaControl's page:

http://www.adacontrol.fr

Nitpick:

To install it, type:

gprinstall inst.gpr

(will be in the doc with next version) [See also "AdaControl", AUJ 37-4, p. 189. —sparre]

# **CP/M:** Towers of Hanoi

From: Alexey Voronin

<dreamy16101976@gmail.com>

Date: Wed, 19 Apr 2017 14:44:38 -0700

Subject: Ada compiler on Arduino Nano 3.0

Newsgroups: comp.lang.ada

I ran the Ada language compiler on my Arduino Nano-based emulator of computer with Intel 8080 and OS CP/M!

https://acdc.foxylab.com/sites/default/ files/cpm\_mk1.jpg

http://acdc.foxylab.com/node/76 (in russian)

https://github.com/Dreamy16101976/cpm 4nano

Compilation of the program TOWERS.ADA for solving the problem of the "Hanoi Tower":

https://acdc.foxylab.com/sites/default/ files/towers\_ada\_comp.png

Running the compiled program TOWERS.COM:

https://acdc.foxylab.com/sites/default/ files/towers\_ada\_3.png

From: Weston Pan <pan.weston@gmail.com> Date: Wed, 19 Apr 2017 16:59:09 -0700 Subject: Re: Ada compiler on Arduino Nano 3.0

Newsgroups: comp.lang.ada

Congratz!

There is an old Janus/Ada 1.5 CP/M compiler as well

(http://www.retroarchive.org/cpm/lang/JA NADA15.ZIP). Maybe you can try that out too.

# Mac OS X: GCC

From: Simon Wright <simon@pushface.org> Date: Mon, 15 May 2017 20:14:20 +0100 Subject: ANN: GCC 7.1.0 for macOS Newsgroups: comp.lang.ada

GCC 7.1.0 for macOS El Capitan and Sierra, built for C, C++, Ada, Fortran, Objective-C, and Objective-C++, and including Ada ASIS, AUnit, GDB, Gprbuild, GNATColl, and XML/Ada, is available at https://sourceforge.net/projects/gnuada/

files/GNAT\_GCC%20Mac%20OS%20X/ 7.1.0/native-2016

[See also "Mac OS X: GCC", AUJ 37-2, p. 77. —sparre]

# Mac OS X: GCC for ARM-EABI

From: Simon Wright

<simon@pushface.org> Date: Sat, 20 May 2017 16:49:27 +0100 Subject: ANN: GCC 7.1.0 for arm-eabi Newsgroups: comp.lang.ada

GCC 7.1.0, rebuilt as a cross-compiler from macOS to arm-eabi, is available at https://sourceforge.net/projects/gnuada/ files/GNAT\_GCC%20Mac%20OS%20X/ 7.1.0/arm-eabi/

The compiler is known to run on El Capitan and Sierra; it may not run on earlier OS X releases.

The compiler was tested with the Cortex-M3 as found on the Arduino Due[1] and the Cortex-M4 as found on the STMicroelectronics[2] STM32F4 Discovery and STM32F429I Discovery boards. Note, however, that GCC 7 has implemented multilib support for other ARM chips.

GNAT GDB 2016 (rebuilt for arm-eabi) is included.

The compiler comes with no Ada Runtime System (RTS). See the Cortex GNAT Run Time Systems project[3] for candidates.

NOTE 1: the compiler/RTS interface has changed; for the time being, you will need to check out the latest repository update.

NOTE 2: for the same reason, this compiler can't presently be used with AdaCore's embedded-runtimes repository at Github[4].

[1] http://www.arduino.com

[2] http://www.st.com

[3] https://sourceforge.net/projects/ cortex-gnat-rts/

[4] https://github.com/AdaCore/ embedded-runtimes [See also "Mac OS X: GCC for ARM-EABI", AUJ 37-2, p. 78. —sparre]

# References to Publications

# Up-to-date Version of the RM

From: Randy Brukardt

<randy@rrsoftware.com> Date: Mon, 20 Feb 2017 16:03:22 -0600 Subject: Re: relax double parens in expression\_function\_declaration? Newsgroups: comp.lang.ada

> [...] However, I can't find a rule in the ARM that allows it.

You're looking at the wrong version of the RM, then: that was fixed in the Corrigendum. Since "Corrigendum" means "bug-fixes" in ISO-speak, it's silly to use the original version. Find the Corrigendum version of the RM on Ada-Auth.org: http://www.adaauth.org/standards/ada12\_w\_tc1.html. (Or from the main ARM page: http://www.ada-auth.org/arm.html). Since there are fixed scattered throughout the manual, one can never guess whether changes were made to a particular rule.

You can also find the working version of the RM on Ada-auth.org, which includes everything that's been approved for the next version of Ada (whenever that will be); that includes more bug fixes as well as some new features: http://www.adaauth.org/standards/ada2x.html (Whether or not any compiler supports the new stuff is of course up to them; I know GNAT does support some of the new features.)

# **SPARK: Proving GCD**

From: Yannick Moy <moy@adacore.com> Date: Wed, 5 Apr 2017 16:52:44 -0700 Subject: Re: [Spark] Proving GCD Newsgroups: comp.lang.ada

I had proved various versions of GCD some time ago, and needed some motivation to write a blog post about it. Your question gave me the impulse! Here is the blog post, that should answer your question:

http://www.spark-2014.org/entries/detail/ gnatprove-tips-and-tricks-proving-theghost-common-denominator-gcd

# Ada Inside

# **SparForte**

From: Ken O. Burtch <koburtch@gmail.com> Date: Sun, 26 Mar 2017 13:47:00 -0700 Subject: [ANN] SparForte 2.0.3 Newsgroups: comp.lang.ada A new version of SparForte, my Adabased shell, scripting language and web template engine, has been released. It is maintained by myself and other volunteers.

The focus of version 2.0.3 is additional bug fixes following the release of SparForte 2.0. This release includes 25 changes.

A major change in this version: the "new" functions (e.g.

doubly\_linked\_lists.new\_list) have been replaced with a new parameterized type system (e.g. list : doubly\_linked\_list.list( strings ); ).

The release notes can be viewed from

http://www.sparforte.com/news/2017/ news\_mar2017.html

SparForte may be downloaded from

http://www.sparforte.com/download.html

If you encounter any problems, please note I don't read comp.lang.ada regularly.

[See also "SparForte", AUJ 38-1, p. 11. —sparre]

# **KDF9** Emulator

From: Bill Findlay <findlaybill@blueyonder.co.uk > Date: 11 Apr 2017 00:50:30 GMT Subject: KDF9 emulator Newsgroups: alt.folklore.computers, comp.lang.ada

A new version of ee9, my emulator for the English Electric KDF9, is now available, with much other info about the '9, at:

http://www.findlayw.plus.com/KDF9/

Binaries for Mac OS and Linux are provided. The latter also runs on Windows 10 (!)

I hope to offer binaries for Windows <10, and perhaps for the Raspberry Pi in due course.

Older binaries for the latter two systems are already available.

ee9 is written in Ada 2005, using GNAT, the GNU Ada compiler.

[See also "KDF9 Emulator", AUJ 36-4, p. 208. —sparre]

# **MAX! Home Automation**

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Wed, 19 Apr 2017 18:30:25 +0200 Subject: ANN: MAX! home automation v1.9 Newsgroups: comp.lang.ada

The software is an Ada GUI application to control wireless radiator thermostats produced under brands MAX! and ELV.

http://www.dmitry-kazakov.de/ada/ max\_home\_automation.htm

Changes to the previous version:

- MQTT on WebSocket support added;

- The MQTT server's topic names have the leading '/' removed because some MQTT clients reported having troubles with names starting with /';

- When controlled over HTTP or MQTT the target temperature can be specified to be airing, comfort, and eco according to the thermostat settings;

- The thermostat address can be omitted when in control commands over HTTP or MQTT. In this case the command applies to all thermostats;

- HTTP access control (CORS) support added;

- HTTP server JSONP support added. [See also "MAX! Home Automation", AUJ 38-1, p. 11. —sparre]

### Pasta!

From: Gautier de Montmollin

<gautier.de.montmollin@gmail.com> Date: Sat, 20 May 2017 12:48:53 +0000 Subject: Re: Experience with Amazon Web Services ?

*Newsgroups: gmane.comp.lang.ada.gnoga* There is now a permanent URL:

http://pasta.phyrama.com/

The program is work in progress of course - first priority, availability of Gnoga for touchscreen devices...

From: Gautier de Montmollin <gautier.de.montmollin@gmail.com> Date: Thu, 1 Jun 2017 23:44:16 +0000 Subject: Pasta! - levels 11 to 15 available Newsgroups: gmane.comp.lang.ada.gnoga

...same address:

http://pasta.phyrama.com/

Eventually you'll have to redo level 10 - sorry for that.

There was a bug occurring right after last available level was completed, before the increment of the counter of completed levels; this has been corrected.

Now there is some basil leaves appearing among the pasta...

Have fun!

[...]

PS: level 15 is though, but can be done with some luck and experience. I

test levels right after designing them.

The level design is done (as for the Leaves demo) in Ada too, e.g. :

when 14 =>

return

(columns => 7,

rows => 5,

thresholds => 1,

needed =>

(1 => (kind => 'A', min => 10)),

startup\_board => (

1 | 7 => (3 => blocking\_2,others => ' '),

3 | 5 => (3 => blocking\_3,others => ' '),

others => (others => ' ') ), moves => 10, level\_probs => ('A' .. 'E' => 1.0 / 5.0, others => 0.0), logo\_x => logo\_x, logo\_y => logo\_y );

# Ada in Context

# Dot Notation and Untagged Types

From: Luke A. Guest

<laguest@archeia.com>

Date: Sun, 5 Feb 2017 06:17:04 -0800 Subject: Why can't Ada use dot notation on private types?

Newsgroups: comp.lang.ada

A lot of people dislike the fact that you cannot use dot notation on a tagged type if it's private. Is there a reason for this? Surely the compiler knows it's tagged when it looks it up?

From: Randy Brukardt <randy@rrsoftware.com> Date: Mon, 6 Feb 2017 13:44:37 -0600 Subject: Re: Why can't Ada use dot notation on private types?

Newsgroups: comp.lang.ada

> [...]

That was the original idea. But we ran into semantic problems with elementary types (and private types completed with elementary types), so we ended up restricting it to tagged only. (The usual reason applied here: it's better to get a limited version of a feature right -- it can be expanded later if necessary -- that to get a general version of a feature wrong -because then we're stuck with the mistakes forever.)

The problems mainly come from the possibility of implicit .all and 'Access. I personally think we could have done without the later, but the former is traditional Ada semantics which would be weird to not support in this prefix form.

From: Randy Brukardt

<randy@rrsoftware.com> Date: Wed, 8 Feb 2017 17:26:38 -0600 Subject: Re: Why can't Ada use dot notation on private types?

Newsgroups: comp.lang.ada

Dmitry A. Kazakov wrote:

> [...] I want to override "all", so let me do this.

When elementary types are included in prefix notation, there are potentially an infinite number of implicit .all or 'Access combinations. A compiler would have trouble figuring them out (and it could get \*very\* expensive), and a reader would be even more confused.

### From: Randy Brukardt

<randy@rrsoftware.com> Date: Mon. 6 Feb 2017 13:40:26 -0600 Subject: Re: Why can't Ada use dot notation on private types?

Newsgroups: comp.lang.ada

> [privately tagged type]

That would be privacy breaking, of course: the legality of the source would depend upon the private details.

But of course it is legal if you have a tagged private type. (Once done, of course, the fact that the type is tagged is visible.) Completing an untagged private type with a tagged type causes various semantic issues, so I'd recommend against that anyway.

# **Compile-Time Check for** Constant

From: Niklas Holsti <niklas.holsti@tidorum.fi> Date: Thu, 9 Feb 2017 20:46:00 +0200 Subject: Re: Test for constant (or "in parameter" in procedure) Newsgroups: comp.lang.ada

[Check if a entity is a constant/in parameter at compile-time.]

### > [...]

I think I see a valid point in the OP's question. One can imagine a program in which a package A supplies a value ("i" in the example), and in which another, loosely related package B, perhaps in quite another part of the program, implements an algorithm that logically depends on this value never changing (after elaboration). It would be nice to be able to express this inter-package constancy constraint somehow, at compile time, as a guard against future mistakes in program evolution that might make the value non-constant and so destroy the logical basis for the algorithm in package Β.

At present, it seems to me that Ada offers only two ways to do this.

The first way is to make the constant a named number in A, or a constant with a static value, and make a copy as a named number in B. Like this:

### package A is

I: constant Integer := 5; -- A named number or (as here) a -- constant with a static value. end A;

### with A:

package B is My\_I : constant := A.I; -- A named number. This does not -- compile if A.I is non-constant,

-- or has a non-static value (even if

-- constant).

end B<sup>.</sup>

However, this only works if the type of the constant is numeric.