# ADA USER JOURNAL

# Volume 40 Number 1 March 2019

# Contents

|                                                                                                                          | Page              |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                    | 2                 |

| Editorial                                                                                                                | 3                 |

| Quarterly News Digest                                                                                                    | 4                 |

| Conference Calendar                                                                                                      | 24                |

| Forthcoming Events                                                                                                       | 31                |

| Ada-Europe 2018 Industrial Presentations                                                                                 |                   |

| Z. Haider, B. Gallina, A. Carlsson, S. Mazzini, S. Puri<br>"ConcertoFLA-based Multi-concern Assurance for Space Systems" | 35                |

| Ada-Europe 2018 Technical Presentations                                                                                  |                   |

| M. Lindler, J. Aparicio, P. Lindgren<br>"Concurrent Reactive Objects in Rust Secure by Construction"                     | 41                |

| Special Contribution                                                                                                     |                   |

| A. Burns, B. Dobbing, T. Vardanega<br>"Guide for the Use of the Ada Ravenscar Profile in High Integrity Systems (Part 1) | 53                |

| Ada-Europe Associate Members (National Ada Organizations)                                                                | 72                |

| Ada-Europe Sponsors                                                                                                      | Inside Back Cover |

# Editorial Policy for Ada User Journal

#### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

#### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj.*

#### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

#### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

#### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

#### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

Is it true that life begins at forty? Looking back to the history of the Ada User Journal, I think no, it doesn't. The AUJ has a very rich and lively past, with countless contributions received from, and to, the community, actively playing an important role in the promotion of Ada and Reliable Software! Nonetheless, in the year the AUJ turns 40, we instead look to, and prepare for, the future.

An important guarantee of this future is the team in charge of the Journal. And I am glad to inform the readers of further changes to the Ada User Journal editorial team: António Casimiro, from the University of Lisbon in Portugal, joins the team as Associate Editor, and Alejandro Mosteo, from Centro Universitario de la Defensa de Zaragoza, Spain, joins as News Editor. As you all know, the Journal is put together by a set of volunteers, which dedicate time and effort to the preparation, editing, publishing and distribution of the Journal, and it is thus important to strengthen this team. Further changes are being prepared, which we will inform later in the year.

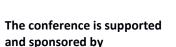

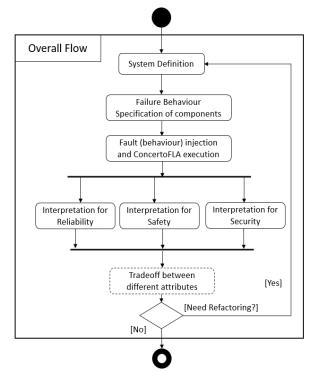

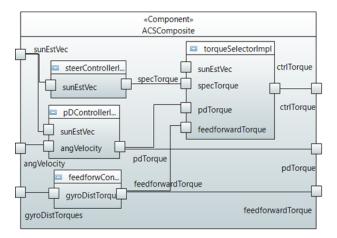

As for the contents of the issue, we conclude the publication of contributions related to the Ada-Europe 2018 conference. First, a paper derived from an industrial presentation, from a group of authors of Mälardalen University and OHB, Sweden, and Intecs, Italy, presenting the customization of the CHESS methodology and the ConcertoFLA toolset for the development of space software under the ECSS standard. Afterwards, the reader will find a paper on the use of the concurrent object concept in the context of the Rust language, which was the topic of a technical presentation at the conference, by a group of authors from the Luleå University of Technology, Sweden.

Closing the issue, we publish the first part of the Guide for the Use of the Ada Ravenscar Profile in High Integrity Systems, which has been updated to consider Ada 2012, and is being prepared to be approved as a ISO technical report. The guide, written by Alan Burns, from the University of York, UK, Brian Dobbing, currently retired and at the time at Altran Praxis, UK, and Tullio Vardanega, from the University of Padua, Italy, includes the definition, rationale and examples of use of the Ravenscar profile, provided in this first part, and also describes the verification approach appropriate to analyse Ravenscar programs, which will be published in the next issue of the Journal.

As usual, the reader will also find the valuable information of the News and Calendar sections. I would also like to draw your attention to the advance information about the Ada-Europe 2019 conference, which, apart from the rich content of tutorials, exhibition and scientific and technical presentations will also provide a very rich networking environment.

Luís Miguel Pinho Porto March 2019 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

#### Kristoffer Nyborg Gregertsen

SINTEF, Email: kristoffer.gregertsen@sintef.no

#### Contents

| Ada-related Tools          | 4  |

|----------------------------|----|

| Ada-related Products       | 7  |

| References to Publications | 8  |

| Ada Inside                 | 8  |

| Ada in Context             | 17 |

#### Ada-related Tools

#### Qt5Ada

From: leonid.dulman@gmail.com Subject: Announce: Qt5Ada version 5.12.0 release 21/12/2018 free edition Newsgroups: comp.lang.ada Date: Fri, 21 Dec 2018 10:56:14 -0800

Qt5Ada is Ada-2012 port to Qt5 framework (based on Ot 5.12.0 final)

Qt5ada version 5.12.0 open source and qt5c.dll, libqt5c.so(x64) built with Microsoft Visual Studio 2017 in Windows, gcc x86-64 in Linux.

Package tested with gnat gpl 2012 ada compiler in Windows 32bit and 64bit, Linux x86-64 Debian 9.4.

It supports GUI, SQL, Multimedia, Web, Network, Touch devices, Sensors, Bluetooth, Navigation and many others thinks.

Changes for new Qt5Ada release:

Added new packages: Qt.QStringView, Qt.QGraphicsCustomItem, Qt.QGLContext

My configuration script to build Qt 5.12.0 is: configure -opensource -release nomake tests -opengl dynamic -qt-zlib qt-libpng -qt-libjpeg -openssl-linked OPENSSL\_LIBS="-lssleay32 -llibeay32" -plugin-sql-mysql -plugin-sql-odbc plugin-sql-oci -icu -prefix "e:/Qt/5.12"

As a role Ada is used in embedded systems, but with QTADA(+VTKADA) you can build any desktop applications with powerful 2D/3D rendering and imaging (games, animations, emulations) GUI, Database connection, server/client, Internet browsing, Modbus control and many others thinks.

Qt5Ada and VTKAda for Windows, Linux (Unix) https://r3fowwcolhrzycn2yzlzzwon.drv.tw/AdaStudio/

The full list of released classes is in "Qt5 classes to Ot5Ada packages relation table.docx" VTKAda version 8.1.0 is based on VTK 8.1.0 (OpenGL2) is fully compatible with Qt5Ada 5.12.0

I hope Qt5Ada and VTKAda will be useful for students, engineers, scientists and enthusiasts

With Qt5Ada you can build any applications and solve any problems easy and quickly.

If you have any problems or questions, tell me know.

#### **AWS** issue

From Andrew Shvets <andrew.shvets@gmail.com> Subject: Can't get to include AWS Newsgroups: comp.lang.ada Date: Thu, 27 Dec 2018 19:58:14 -0800

I installed the latest GNAT Community distribution from AdaCore in ~/GNAT and when I tried to use my \*.GPR file in order to build my code, I encountered the below error:

unknown project file: "aws"

In my \*.GPR file I did 'with "aws";'.

Is there some path or some other config value that needs to be set?

Thanks in advance for your replies.

From: eduardsapotski@gmail.com Subject: Re: Can't get to include AWS Newsgroups: comp.lang.ada Date: Fri, 28 Dec 2018 01:23:55 -0800 Run GPS.

Open project.

Edit -> Project Properties -> Dependencies

Drag AWS to left panel.

Save.

Or in .gpr file paste: with "aws.gpr";

From: Simon Wright

<simon@pushface.org> Subject: Re: Can't get to include AWS Newsgroups: comp.lang.ada Date: Sat, 29 Dec 2018 20:30:30 +0000

> I installed the latest GNAT Community distribution from AdaCore in ~/GNAŤ and when I tried to use my \*. GPR file in order to build my code, I encountered the below error:

> unknown project file: "aws"

> In my \*.GPR file I did 'with "aws";'.

I have GNAT CE installed under /opt/gnat-ce-2018.

If I don't have /opt/gnat-ce-2018/bin on my PATH but say /opt/gnat-ce-2018/ bin/gprbuild -P shvets.gpr where shvets.gpr contains 'with "aws";' I get the same as you.

If I do have /opt/gnat-ce-2018/bin on my PATH and say

gprbuild -P shvets.gpr

it works fine.

#### **Protobuff for Ada**

From: Per Sandberg cper.s.sandberg@bahnhof.se> Subject: protobuff for Ada Newsgroups: comp.lang.ada Date: Fri, 28 Dec 2018 19:57:40 +0100

I managed to resurrect an old master thesis work that was done by Niklas Ekendahl in 2013 and put it on

https://github.com/persan/protobuf-ada

the plan is to get it in working shape.

From: Shark8

<onewingedshark@gmail.com> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Fri, 28 Dec 2018 21:53:55 -0800

Cool

More libs, bindings, and implementations in Ada is a good thing.

Though, it should be noted that ASN.1 is \*probably\* the better technology in cases where ProtoBufs are being considered:

http://ttsiodras.github.io/asn1.html

From: "Dmitry A. Kazakov" <mailbox@dmitry-kazakov.de> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Sat, 29 Dec 2018 12:05:40 +0100

- > Though, it should be noted that ASN.1 is \*probably\* the better technology in cases where ProtoBufs are being considered:

- > http://ttsiodras.github.io/asn1.html

Sorry to disappoint you in this festive time, but this approach has the same fundamental flaw as prepared SQL statements do. You have to bind native Ada objects to protocol/serialized/ persistent objects forth and back. This

does not work well in practice. In fact, it barely work at all considering the overhead and hazards of type conversions.

A different approach is Ada's representation clauses which describe both objects same. Beyond simple textbook cases that does not work either.

The best practical method so far is using manually written stream attributes. Unfortunately it has shortcomings too:

- 1. Reuse is limited and composition is unsafe because stream attributes are non-primitive operations.

- Introspection is almost non-existed. Only tagged types could have it.

- 3. No support of error handling and versioning. Though it is possible to do manually that is extremely error-prone and totally lacks static verification when the number of test cases is huge to potentially infinite. Even worse, the offending cases do not show up in a normally functioning system. So, when detected, it is always too late.

P.S. Needless to say, the problems 1-3 fully apply to other two methods as well.

P.P.S. And nothing was said about referential and recursive types...

From: Olivier Henley <olivier.henley@gmail.com> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Mon, 31 Dec 2018 08:55:40 -0800

Interesting. I do not grasp the problem in full though...

When you say "Sorry to disappoint you in this festive time", do you mean trying a solution from ASN.1 or only trying at Protobuff?

I think I get why a Protobuff could not cover "complete" transfer of Ada types around, but how does other languages do? (Almost everyone has it) Some of these languages have relatively "complex" type system..?

How do they achieve it? They express any complex types with a limited subset of primitive types(string, int32, etc)?

Can you give a more pragmatic example that exemplifies the limitations in Ada?

#### From: "Dmitry A. Kazakov" <mailbox@dmitry-kazakov.de> Subject: Re: protobuff for Ada

Newsgroups: comp.lang.ada

Date: Mon, 31 Dec 2018 18:59:35 +0100

>> When you say "Sorry to disappoint you in this festive time", do you mean trying a solution from ASN.1 or only trying at Protobuff?

Both. They are useless, up to harmful.

> I think I get why a Protobuff could not cover "complete" transfer of Ada types around, but how does other languages do? (Almost everyone has it) Some of these languages have relatively "complex" type system..?

The very concept of a data definition/description language (DDL) is wrong as I tried to explain. It has a very long and sad history in process automation, control, communication (e.g. CORBA), databases (e.g. SQL). Almost everybody and everyone tried it and failed. There are countless protocol describing "languages" around in process automation. I fought with them for decades, wrote several compilers for this mess. One could save huge amount of money and time if there were a law to punish people introducing this stuff... (:-))

> How do they achieve it? They express any complex types with a limited subset of primitive types (string, int32, etc)?

You cannot express a type in a DDL. Data /= Type. Type = data + operations. If you want to express complex typed objects you lose before you start with a DDL. You throw all type semantics overboard.

\*If\* you are OK without semantics then there is no need to introduce this mess. Use Ada stream attributes and simply read and write what you want and how you want. It is clean, easy, fast and 100% Ada.

> Can you give a more pragmatic example that exemplifies the limitations in Ada?

Any limitations Ada might have are unrelated to the issue of language impedance: DDL vs Ada unless you make DDL embedded like embedded SQL, which does not work either.

I believe AdaCore has a product of the sort. Though I don't think that would be much better, but I would rather trust them than anybody else...

From: G. B. <nonlegitur@nmhp.invalid> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Wed, 2 Jan 2019 06:57:14 -0000

\*If\* you are OK without semantics then there is no need to introduce this mess. Use Ada stream attributes and simply read and write what you want and how you want. It is clean, easy, fast and 100% Ada.

What kind of stream do you write for your partners in business? Three of them have different needs than you WRT data and none of them is using Ada.

From: "Dmitry A. Kazakov"

<mailbox@dmitry-kazakov.de> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Wed, 2 Jan 2019 11:02:10 +0100

>[...]

> What kind of stream do you write for your partners in business?

Stream of octets.

> Three of them have different needs than you WRT data and none of them is using Ada.

They still can read and write the stream. You are confusing description of a protocol with the implementation of.

The OP suggested having descriptions in protobuff and partial implementation generated from that. It is a bad idea.

BTW, it is very easy to write things like protobuff straight in Ada with Simple Components

http://www.dmitry-kazakov.de/ada/ components.htm#17.2.1

This feature is rarely used because, as I said, the concept is too limited and constraining if not wrong altogether.

Here is a small example. Consider an example in protobuff:

message Person {

required string name = 1;

required int32 id = 2;

optional string email = 3;

}

This direct Ada code:

type Person is new State\_Machine with Name : String\_Data\_Item (Max\_String\_Length); ID : Unsigned\_32\_Data\_Item; Email : String\_Data\_Item

(Max\_String\_Length);

end record;

Thanks to Ada's "introspection" that is all. It will be read or written by the connections server automatically. On the packet receipt callback, you get values like Person\_Session.ID.Value. Before sending a new packet you assign Person\_Session.ID.Value. Note, this is Ada 95, no fancy stuff.

I didn't show here alternation for using optional fields because the transport level representation would be different anyway. Which is the point actually. Such key details are all left unspecified in the protobuff "description" above along with endianness and other encoding issues. Yet exactly these details are essential in practice where the protocol is already defined. Present or not bits might kept combined in the message header, special values of integers are reserved to indicate exceptional states and so on and so forth. And, again, no semantics whatsoever, just buckets of bits.

From: Per Sandberg

<press.sandberg@bahnhof.se> Subject: Re: protobuff for Ada Newsgroups: comp.lang.ada Date: Tue, 1 Jan 2019 09:05:38 +0100

From my perspective absolutely biggest flaw with technologies like protobuff is:

- \* Its backed by a large corporation.

- \* The technology is well known.

- \* 99.9% of the programming population think that they are the salvation to serialization.

- \* The licensing is open.

And on top.

\* There are significantly more than one project where the lack of protobuff support has ruled out Ada as implementation technology.

And my intent was to eliminate at least the last points even if the technology is inferior.

#### AdaControl

From: "J-P. Rosen" <rosen@adalog.fr> Subject: [Ann] AdaControl V1.20r7 released

Newsgroups: comp.lang.ada Date: Thu, 3 Jan 2019 14:03:30 +0100

Adalog is pleased to announce the release of a new version of AdaControl. Thanks to the support of several sponsors, there are several interesting new controls (see file HISTORY), with a grand total of 70 rules and 565 possible tests! The automatic fixes feature has been extended too.

More details, download, etc. from http://adacontrol.fr. The executable version is now provided for Gnat Community edition 2018.

Reminder: If you have any issue with AdaControl, please report it using

http://sourceforge.net/p/adacontrol/ticket

And if you use it for an industrial project, commercial support is available from Adalog, don't hesitate to ask for information at info@adalog.fr

#### **GNU ELPA**

From: Stephen Leake <stephen\_leake@stephe-leake.org> Subject: GNU ELPA package ada-ref-man version 2012.4 is now available Newsgroups: comp.lang.ada Date: Sat, 5 Jan 2019 10:26:23 -0800

GNU ELPA package ada-ref-man version 2012.4 is now available. This version adds '<' '>' annotation to indicate italics in syntax element names:

generic\_instantiation ::=

package defining\_program\_unit\_name is

new <generic\_package\_>name

[generic\_actual\_part]

[aspect\_specification];

#### **Simple Components**

From: "Dmitry A. Kazakov" <mailbox@dmitry-kazakov.de> Subject: ANN: Simple Components for Ada v4.36

Newsgroups: comp.lang.ada Date: Tue, 8 Jan 2019 12:50:31 +0100 The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, streams, multiple connections server/client designing tools and protocols implementations. The library is kept conform to the Ada 95, Ada 2005, Ada 2012 language standards.

http://www.dmitry-kazakov.de/ada/ components.htm

Changes to the previous version:

- The package GNAT.Sockets.Server.Blocking was added to provide connection servers handling blocking I/O;

- Procedures Send\_Socket and Receive\_Socket were added to the package GNAT.Sockets.Server;

- Procedures Reconnect and Request\_Disconnect were added to the package GNAT.Sockets.Server;

- The functions Is\_Configured, Is\_In, Has\_Device\_Configuration were added GNAT.Sockets.Connection\_State\_Mach ine.ELV\_MAX\_Cube\_Client;

- Airing time decoding/encoding error in GNAT.Sockets.Connection\_State\_Mach ine.ELV\_MAX\_Cube\_Client.

#### **SparForte**

From: koburtch@gmail.com Subject: Ann: SparForte 2.2 Newsgroups: comp.lang.ada Date: Tue, 8 Jan 2019 20:15:29 -0800

SparForte version 2.2 was released over the holidays.

It is available for download from the SparForte website:

https://www.sparforte.com/

This version brings preliminary programming-by-contract, side-effect detection and additional shell features. An overview can be found on my blog:

https://www.pegasoft.ca/coder/ coder\_december\_2018.html

There are also several recent blog articles on the design of SparForte, as requested by the mailing list subscribers.

SparForte is a shell, scripting language and web template engine with a core feature set based on Ada. I hope you will find it useful.

Note: I do not regularly read this newsgroup. Please direct questions to the SparForte mailing list.

#### VTKAda

From: leonid.dulman@gmail.com Subject: VTKAda 8.2.0 Newsgroups: comp.lang.ada Date: Fri, 1 Feb 2019 11:19:09 -0800

I'm pleased to announce VTKAda version 8.2.0 free edition release 01/02/2019.

VTKAda is Ada-2012 port to VTK (Visualization Toolkit by Kitware, Inc) and Qt5 application and UI framework by Nokia VTK version 8.2.0, Qt version 5.12.0 open source and vtkc.dll, vtkc2.dll, qt5c.dll (libvtkc.so, libvtkc2.so, libqt5c.so) were built with Microsoft Visual Studio 2017 (15.9) in Windows (WIN32) and gcc in Linux x86-64

Package was tested with gnat gpl 2017 ada compiler in Windows 10 64bit, Debian 9.4 x86-64

As a role ADA is used in embedded systems, but with VTKADA(+QTADA) you can build any desktop applications with powerful 2D/3D rendering and imaging (games, animations, emulations) GUI, Database connection, server/client, Internet browsing and many others thinks.

VTKADA you can be used without QTADA subsystem

Qt5Ada and VTKAda for Windows, Linux (Unix) https://r3fowwcolhrzycn2yzlzzwon.drv.tw/AdaStudio/

#### Florist

From: "J-P. Rosen" <rosen@adalog.fr> Subject: Florist is in Ada ! Newsgroups: comp.lang.ada Date: Tue, 19 Feb 2019 17:10:08 +0100

See: https://www.carolslaneflorist.com/ about-us

(found this while browsing for Florist, the Ada interface to Posix) :-)

#### **OpenGLAda**

From: Felix Krause <contact@flyx.org> Subject: ANN: OpenGLAda 0.7.0 Newsgroups: comp.lang.ada Date: Sat, 9 Mar 2019 19:18:49 +0100

This release includes some additions to the API, but primarily adds GNAT Community 2018 support. It is also the first release with a Windows installer. This installer includes the optional dependencies (GLFW and Freetype) and installs OpenGLAda on top of an existing GNAT installation.

The dependency on the 3rd party library Strings Edit has been removed and UTF-8 decoding is now part of the project. This hopefully reduces confusion.

Release and further information is available here:

https://github.com/flyx/OpenGLAda/ releases

### **Ada-related Products**

#### SPARK

From: addaon@gmail.com Subject: New to Spark, working an example Newsgroups: comp.lang.ada Date: Sat, 15 Dec 2018 21:43:50 -0800

Folks, new to this list, so not quite sure on etiquette.

I've been trying to understand Spark-2014 well enough to work through an example, and understand the capabilities and workflow of the tools. The example I chose was an example of floor(lg(n)) for n positive.

Rather than put a long post here, I'll refer to my (long) post at stackoverflow:

https://stackoverflow.com/questions/ 53752715/proving-floor-log2-in-spark. (If this is bad etiquette here, let me know, and I'll fix -- but it does seem a bit silly to duplicate the content in two locations)

Since SO seems to have a very limited Ada/Spark community, I'm hoping someone here can point me in the right direction. Basically, trying to understand what tools I should be trying to understand at this point. :-) Should I be looking at proving this with just a better understanding of how to write loop invariants; through appropriate lemmas; through an external prover like Coq; or something else?

From: Simon Wright

<simon@pushface.org> Subject: Re: New to Spark, working an example

Newsgroups: comp.lang.ada

Date: Sun, 16 Dec 2018 09:48:17 +0000 I don't think there's anything wrong with

trying to attract attention (what gets my goat a bit is people posting the same question in both places at the same time).

I have to confess that I hadn't set up my SO account to watch the tags [spark-2014] or [spark-ada] (why both?), or even [gnat] or [ada2012] - rectified. You would have got more views if you'd included [ada] (but not necessarily any (more) answers :)

Your problems are an indication of why I, as a person who has no access to professional SPARK support, haven't invested any effort to speak of in SPARK (my difficulties were with tasking/time rather than mathematical loops, which tend to be rare in control systems).

That said, it looks to me as though the version of gnatprove in GNAT CE 2018 may not fully understand exponentiation:

util.ads:3:14: medium: postcondition might fail, cannot prove

2 \*\* Floor\_Log2'Result <= X

util.ads:3:16: medium: overflow check might fail

(e.g. when Floor\_Log2'Result = 0)

From: Brad Moore <bmoore.ada@gmail.com> Subject: Re: New to Spark, working an example

Newsgroups: comp.lang.ada Date: Tue, 18 Dec 2018 18:41:59 -0800

I am by no means a SPARK expert, but I am also interested in exploring SPARK capabilities.

My approach led me to the following solution using just the SPARK 2018 GPL download from Adacore.... (no extra provers were needed here, other than the ones that come with GNAT CE 2018)

As an aside, it appears the version of gnatprove in GNAT CE 2018 does have a pretty good understanding of exponentiation, given that I was able to get the following proven.

package Util with SPARK\_Mode is Max\_Log2 : constant := Positive'Size - 1; subtype Log\_Result is Natural range 0 .. Max\_Log2;

function Floor\_Log2 (X : Positive) return

Log\_Result with

Global => null,

Depends => (Floor\_Log2'Result => X),

Post => X >= 2\*\*Floor\_Log2'Result

and then X / 2 < 2\*\*Floor\_Log2'Result;

end Util;</pre>

pragma Ada\_2012;

```

package body Util with SPARK_Mode is

function Floor Log2 (X : Positive) return

Log_Result is

begin -- Floor_Log2

Log_Loop :

for I in Log_Result loop

pragma Loop_Invariant

(for all J in 0 ... I \Rightarrow X \ge 2^{**}J);

pragma Assert

(X / 2 < 2**Log_Result'Last);

if X / 2 < 2^{**} then

pragma Assert (X >= 2**I);

pragma Assert (X / 2 < 2**I);

return I;

end if:

pragma Assume(I /= Log_Result'Last);

end loop Log_Loop;

return Log_Result'Last;

end Floor_Log2;

```

end Util;

I technically didn't need to use the Global aspect or the Depends Aspect to prove this function, but I think it is a good idea to provide a more detailed contract using additional SPARK and Ada features, when possible.

The approach I took is to first of all make use of Ada 2012 contracts to constrain the results to only allow valid values. The Log\_Result subtype only includes valid result values.

I think this is an important goal in general to eliminate bugs, whether writing code for regular Ada as well as SPARK. My view is that in general, types such as Integer and Float should not be used since they are types that describe memory storage, not types that describe values of interest in the application domain.

By creating types that more accurately represent the application domain, I believe it makes the job of writing proofs in SPARK much easier, since the prover can reason that the values assigned to such values have specific value ranges and properties.

Another point, is to try to write an implementation that is easier to prove. For that reason, I wrote this is a for loop rather than a while loop, because the compiler can reason statically about how many iterations are performed, and what the values of the loop parameters can be.

The prover was able to prove all the assertions in the implementation.

I had to leave in one assumption, (the pragma assume),

pragma Assume(I /= Log\_Result'Last);

Without that, the prover complains that the post condition,

X / 2 < 2\*\*Floor\_Log2'Result

cannot be proven. It appears that the prover is not able to prove that the loop exited by the return statement, rather than iterating the full loop and exiting the loop without entering the if statement.

However, I think this can be visually inspected and confirmed to be true, since the assert for the if statment,

pragma Assert(X / 2 < 2\*\*Log\_Result'Last);</pre>

just prior to the if statement was proven.

It follows that if the assertion is true, then the if statement would have to be entered on the following line, and that the return would exit the loop.

Thus, the reader should be able to visually tell that it is impossible to get by the if statement when  $I = Log_Result'Last$ , and thus the pragma Assume is true.

The return at the end of the function should never get executed, as the only way to exit the function is via the return inside the loop.

I didn't need to have the return inside the loop for the purpose of proving the function. I just did that to eliminate the need of extra variable declarations.

Probably the prover could be improved so that such an assume could be eliminated while still proving the overall function.

There may be a way to add additional asserts or pragmas to eliminate the need for the pragma Assume. So far I haven't found any, but perhaps someone else might come up with a way. Otherwise, I'm pretty happy with the solution I ended up with, given that the one assume in the code can be visually checked easily for correctness.

I am sure that other SPARK solutions exist. I think when it comes to proving something, it is better to start with something simple, and to have in mind choosing an implementation that is easier to prove. This should make it easier to arrive at a proof.

From: Simon Wright <simon@pushface.org> Subject: Re: New to Spark, working an example

Newsgroups: comp.lang.ada Date: Wed, 19 Dec 2018 16:58:41 +0000

>> util.ads:3:16: medium: overflow check

might fail (e.g. when >>

Floor Log2'Result = 0)

> As an aside, it appears the version of gnatprove in GNAT CE 2018 does have a pretty good understanding of exponentiation, given that I was able to get the following proven.

Apparently so. But the part of gnatprove that gives examples of when the assertion might fail is quite misleading: for example,

util.ads:7:14: medium: postcondition might fail, cannot prove 2 \*\* Floor\_Log2'Result <= X (e.g. when Floor\_Log2'Result = 0 and X = 0) \*when X is Positive\* !!

and util.adb:19:15: medium: overflow check might fail (e.g. when I = 0) 1.18 for I in 1 .. Log Result'Last loop

1.19 if 2 \* I > X then

From: Brad Moore <bmoore.ada@gmail.com> Subject: Re: New to Spark, working an

example Newsgroups: comp.lang.ada Date: Wed, 19 Dec 2018 20:34:13 -0800

I agree that the error messages are misleading, as I was getting similar messages when I was working on this. While the values "0" mentioned in the error messages were confusing to me, I think the messages were helpful at least in suggesting the sort of tests the prover was trying to prove, which ultimately helped me figure out the assertions that were needed to get this to pass. The values given can be a bit of a red herring sometimes, but I think the underlying test described by the message is more helpful. This is my second problem that I attempted to prove in SPARK, so I didn't know if I would succeed, or know much about how to approach this. It's kind of a rewarding feeling when you get the prover to pass.

One suggestion I have to prove post conditions, is to state the post condition as an assert before returning from the subprogram, and work backwards from there.

# References to Publications

#### **Ravenscar References**

From: lyttlec <lyttlec@removegmail.com> Subject: Ravenscar References Newsgroups: comp.lang.ada Date: Wed, 16 Jan 2019 12:48:28 -0500

Can anyone suggest a good reference on using the ravenscar profile? In the Ada books I have, it only gets a one or two page mention. A reference with an extended case study would be great.

From: Simon Wright <simon@pushface.org> Subject: Re: Ravenscar References Newsgroups: comp.lang.ada Date: Wed, 16 Jan 2019 18:15:03 +0000

You might find something useful at http://cubesatlab.org e.g. http://www.cubesatlab.org:430/ PUBLIC/brandon-chapin-HILT-2016.pdf

From: lyttlec <lyttlec@removegmail.com> Subject: Re: Ravenscar References Newsgroups: comp.lang.ada Date: Fri, 18 Jan 2019 14:18:10 -0500

Thanks all for the links. They are a help. However, I'm looking for something along the lines of porting legacy code to be ravenscar "safe".

As an illustration, consider making Dmitry A Kazakov's code meet Ravenscar. I need to port lots of existing more or less standard components to meet Ravenscar. This is to satisfy some regulatory authorities.

From: "Jeffrey R. Carter" <spam.jrcarter.not@spam.not.acm.org> Subject: Re: Ravenscar References Newsgroups: comp.lang.ada Date: Sun, 20 Jan 2019 18:12:11 +0100

I don't know that "port" is a good word for this activity. I once looked at implementing Sandén's FMS problem using Ravenscar. Starting from the requirements, I first had to find a Ravenscar-suitable design. The standard design has a dynamic task per job, and is clearly not possible using Ravenscar. An alternative design using a task per workstation had to be used.

From that choice, Ravenscar drove a proliferation of protected objects and helper tasks. Things that were simple in full Ada became much more complex to meet the restrictions of the profile.

Presumably you would need to apply a similar process to each of the components you need to convert.

From: "Randy Brukardt" <randy@rrsoftware.com> Subject: Re: Ravenscar References Newsgroups: comp.lang.ada Date: Mon, 21 Jan 2019 17:19:43 -0600 Note that the less strict profile Jorvik, defined in Ada 2020 (and already implemented in GNAT) would simplify this process.

I don't think it is possible to "convert" regular Ada code into Ravenscar (unless, of course, it doesn't use any tasks ;-). You pretty much have to completely rewrite it with Ravenscar in mind. (In this way, it is very much like using SPARK.)

From: "J-P. Rosen" <rosen@adalog.fr> Subject: Re: Ravenscar References Newsgroups: comp.lang.ada Date: Tue, 22 Jan 2019 10:25:08 +0100

I don't fully agree with that statement; it all depends where you start from.

I recently helped one of my clients who wanted to move to Ravenscar. The original structure was all Ada83, communicating with rendezvous.

However, it was already safety critical, therefore based on cyclic, never ending tasks, and limited communications. It was reasonably easy to define patterns for matching the existing structure into Ravenscar patterns.

#### Ada Inside

#### **Compilation Issues**

From: alexander@junivörs.com Subject: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 03:46:02 -0800

I've read some threads on here regarding the licensing situation of AdaCore's Libre compiler. For my upcoming project, I'm going to need (= very strong desire) to use Ada and I'm also going to need to be able to license the executable produced thereof in any way I desire.

In regards to the aforementioned, I have two questions. I realize I come forth as somewhat paranoid in the upcoming paragraphs (which undoubtedly I am). The licensing situation worries me a great deal.

1. ```As for the compiler build provided by (the GetAdaNow Mac OS X section's link to Sourceforge)[1]; which parts of that GCC build for compiling Ada can you safely use and still be covered by the "GCC Runtime Library Exception"? I can see it states you can use 'GNATCOLL' and `XMLAda`. I'm assuming the standard library is included as well. Can you on the other hand use all console commands? `gnat <command>`? gprbuild`? Or would these inject "nonruntime library exception'd" GPL code into the executable?```2. ```I've been attempting to compile and link some code through the use of the 'gcc' command solely, but haven't been successful in doing so. I have, on the other hand, been able to successfully generate an

executable by utilizing the `gnatbind` and `gnatlink` commands consecutively after compiling with `gcc -c <file>`. Is it possible to use only the `gcc` command for the matter, or do you need to also throw in a few calls to the `gnat` commands?

When executing the following commands...

\$ gcc -c src/main.adb -o obj/main.o

\$ gcc -o main obj/main.o

I wind up with the following error (on the second command, which should be a GCC link):

Undefined symbols for architecture x86 64:

"\_main", referenced from:

implicit entry/start for main executable

(maybe you meant: \_\_ada\_main)

ld: symbol(s) not found for architecture x86\_64

collect2: error: ld returned 1 exit status

A similar error occurs when I attempt to create `.so` libraries manually using the `shared` compiler switch. With all that being said, is it simply not possible to do these things through solely `gcc`, or am I missing something?```

It may be worth noticing that I've fallen in love with Ada to the utmost degree over the past year. As such, I'm planning on, at the very least, stalking "comp.lang.ada" like some creepy figure. You'll probably see more from me beyond these first two questions, is what I'm saying.

[1] https://sourceforge.net/projects/ gnuada/files/GNAT\_GCC 20Mac OS X/ 8.1.0/native-2017/

From: Simon Wright

<simon@pushface.org> Subject: Re: Licensing Paranoia and Manual Compilation Issues

Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 16:11:48

Let me start by saying that I'm not a lawyer.

> 1. ```As for the compiler build provided by (the GetAdaNow Mac OS X section's link to Sourceforge)[1]; which parts of that GCC build for compiling Ada can you safely use and still be covered by the "GCC Runtime Library Exception"? I can see it states you can use `GNATCOLL` and `XMLAda`. I'm assuming the standard library is included as well. Can you on the other hand use all console commands? `gnat <command>`? `gprbuild`? Or would these inject "non-runtime library exception'd" GPL code into the executable?```

They may (do) \*generate\* source code that gets included in the executable (gnatbind does this). But that isn't code that's provided with the compiler and

Ada User Journal

might have a copyright issue; it's no different in principle from object code generated directly by the compiler.

> 2. ```I've been attempting to compile and link some code through the use of the `gcc` command solely, but haven't been successful in doing so. I have, on the other hand, been able to successfully generate an executable by utilizing the `gnatbind` and `gnatlink` commands consecutively after compiling with `gcc -c <file>`. Is it possible to use only the `gcc` command for the matter, or do you need to also throw in a few calls to the `gnat` commands?

[...]

Building even hello\_world\* is sufficiently complex that you need gnatbind, gnatlink. As you've seen, you can use gcc for the actual compilation.

Building a dynamic library (do you mean .so? are you on a Mac or Linux?

You mention my darwin 8.1.0 release) is more so.

To see what gnatbind gets up to while doing its work, look at the  $b_*$  (or  $b^{*}$ ) files it generates. Not much fun or point in generating those by hand.

\* You can build a simple null program for an embedded system on an MCU without gnatbind, gnatlink. But you have to bother about storage mappings, prcessor startup, linker scripts etc instead.

From: Lucretia

<laguest9000@googlemail.com> Subject: Re: Licensing Paranoia and

Manual Compilation Issues

Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 08:31:59 -0800

#### [...].

What version is that compiler on sourceforge? Is it from FSF directly, i.e. gcc.gnu.org? Or is it GNAT-GPL/CE, i.e. from AdaCore.com? If the latter, the licence is GPL-3.0 no linking exception, otherwise it's GPL-3.0 with linking exception. Basically, avoid anything GPL-3.0 no linking exception, especially Adacore's libraries.

From: G. B. <nonlegitur@nmhp.invalid> Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 18:50:45 -0000

> I've read some threads on here regarding the licensing situation of AdaCore's Libre compiler. For my upcoming project, I'm going to need (= very strong desire) to use Ada and I'm also going to need to be able to license the executable produced thereof in any way I desire.

For licensing in arbitrary ways, the aforementioned Ada distribution is not the suitable one. Another compiler distribution might meet your needs, including some FSF GNAT. GPL means tit-for-tat and thus intentionally puts restrictions on licensing, no back doors.

From: Simon Wright <simon@pushface.org> Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 19:21:04 +0000 > What version is that compiler on sourceforge? [...]

It's vanilla FSF with Adacore libraries, some of which have the runtime library exception, some of which don't (as noted at the link).

The Adacore sources, at https://github.com/AdaCore, are on the whole GPLv3 with the runtime exception. I've taken care to report the status:

from https://sourceforge.net/projects/ gnuada/files/GNAT\_GCC MacOS X/ 8.1.0/native-2017/

Tools included:

Full GPL:

ASIS from https://github.com/ simonjwright/ASIS at [8ba68f3].

AUnit and GDB from GNAT GPL 2017.

Gprbuild from https://github.com/ AdaCore/gprbuild at commit [1e551df] (note, libgpr is GPL with Runtime Library Exception[1]).

GPL with Runtime Library Exception[1:

#### GNATCOLL from:

https://github.com/AdaCore/ gnatcoll-core at commit [a093d11].

https://github.com/AdaCore/ gnatcoll-bindings at commit [2c426fe].

https://github.com/AdaCore/ gnatcoll-db at commit [b66441c].

#### XMLAda from

https://github.com/AdaCore/xmlada at commit [8a4b2bf]

From: alexander@junivörs.com

Subject: Re: Licensing Paranoia and Manual Compilation Issues

Newsgroups: comp.lang.ada

- Date: Tue, 11 Dec 2018 12:50:42 -0800

- > Building a dynamic library (do you mean .so? are you on a Mac or Linux?

- > You mention my darwin 8.1.0 release) is more so.

Yes. According to (this page)[1] it's accomplishable using the following command:

\$ gcc -shared -o libmy\_lib.so \*.o

but that causes an error mentioning how there are "Undefined symbols for architecture x86\_64:".

> For licensing in arbitrary ways, the aforementioned Ada distribution is not the suitable one. Another compiler distribution might meet your needs, including some FSF GNAT. GPL means tit-for-tat and thus intentionally puts restrictions on licensing, no back doors.

GPL on its own, I must say, does serve a purpose. It's nice for the author to be able to share their source or works and still be certain nobody can (legally anyway) steal their work and distribute it for a fee themselves.

When it comes to source code licensed under GPL lacking the runtime library exception, on the other hand, I can't say I'm too fond of it. Compilers on their own, featuring a standard library, should always be free to use; whereupon the user may licence their executable in any way they want.

[1] http://beru.univ-brest.fr/~singhoff/ DOC/LANG/ADA/gnat\_ugn\_20.html

From: Simon Wright

<simon@pushface.org>

Subject: Re: Licensing Paranoia and

Manual Compilation Issues

Newsgroups: comp.lang.ada Date: Tue, 11 Dec 2018 23:45:48 +0000

> [1] http://beru.univ-brest.fr/~singhoff/ DOC/LANG/ADA/gnat\_ugn\_20.html

Because that page (and even the latest one at [2]) is wrong.

Almost all Ada code requires the services of the Ada runtime, and you need to reference the runtime at the link stage.

\$ gcc -shared -o libmy\_lib.dylib \*.o -L<whereever> -lgnat -lgnarl

(<whereever>: e.g. /opt/gcc-8.1.0/lib/gcc/ x86\_64-apple-darwin15/8.1.0/adalib)

This is why it is \*so\* much easier to use gprbuild (I see that that reference talks about using gnatmake; that's because gnatmake is part of GCC Ada, and gprbuild isn't. But modern gnatmakes will delegate to gprbuild if they find one, at any rate if libraries are involved; they can't generate libraries, because it's too complicated for Adacore to maintain in two places, the GCC tree and the gprbuild tree).

If you want to see what's going on you can use -v.

[2] http://docs.adacore.com/gnat\_ugndocs/html/gnat\_ugn/gnat\_ugn/the\_gnat\_c ompilation\_model.html#general-adalibraries

>> For licensing in arbitrary ways, the aforementioned Ada distribution >> is not the suitable one. Another compiler distribution might meet >> your needs, including some FSF GNAT. GPL means tit-for-tat and thus intentionally puts restrictions on licensing, no back doors.

> GPL on its own, I must say, does serve a purpose. It's nice for the author to be able to share their source or works and still be certain nobody can (legally anyway) steal their work and distribute it for a fee themselves.

> When it comes to source code licensed under GPL lacking the runtime library exception, on the other hand, I can't say I'm too fond of it. Compilers on their own, featuring standard library, should always be free to use; whereupon the user may licence their executable in any way they want.

I don't understand. The first para says it's good, the second says it's bad.

From: alexander@junivörs.com

Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Wed, 12 Dec 2018 01:34:01 -0800

> I don't understand. The first para says it's good, the second says it's bad.

Perhaps I've misunderstood something regarding the licensing situation. Is not the reason you cannot use a bunch of AdaCore developed packages due to the fact that it's licensed under GPL without the runtime library exception, ultimately meaning your executable must be licensed under GPL too?

Let's assume someone made a tool to aid people with a repetitive task in Ada. Give that the GPL license and it'd be impossible for someone to "steal" (redistribute for a fee) the original author's code, still allowing people to learn from the code that makes up the tool.

In the second situation, I'm speaking of any library package offering nigh on essential functionality to a programming language (in this case Ada), that does not contain the runtime library exception. I believe that all code developed to ship with a compiler should contain that exception.

I will make sure to await further responses before I justify my belief mentioned in the previous paragraph, should I prove to having gotten something wrong.

Whilst quickly scouring the Internet for some information that would substantiate the claim that some library package files do not contain the runtime library exception, I came across the ('GNAT.Regpat' source)[1], which does

contain some form of the runtime library exception.

I presume perhaps that is an older source file than the one shipped with the compiler at this day (Copyright (c) 1996-2002)?

[1] https://www2.adacore.com/gap-static/ GNAT\_Book/html/rts/g-regpat\_adb.htm

From: Björn Lundin <b.f.lundin@gmail.com> Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Thu, 13 Dec 2018 10:21:54 +0100 >[...]

You can always "steal" GPL code, and redistribute it for a fee as you see fit. The freedom in GPL is not free as free beer, but free as free speach. So you would need to provide the sources to the customers you sell to. And I think, a fairly easy way to reproduce an executable/library.

You code depending on GPL (linked with) will inherit the GPL license.

But you can charge your customers whatever you want.

However you likely need to provide something better that the original code for people \_wanting\_ to pay you, I guess.

From: alexander@junivörs.com Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada Date: Thu, 13 Dec 2018 02:30:20 -0800

>[...]

I don't know wherefrom I got my information that you can't sell a GPL application. Thank you for clarifying this!

From: alexander@junivörs.com Subject: Re: Licensing Paranoia and Manual Compilation Issues Newsgroups: comp.lang.ada

*Date: Thu, 13 Dec 2018 02:32:47 -0800* > I don't know wherefrom I got my

information that you can't sell a GPL application. Thank you for clarifying this!

Or rather, clarifying the contrary; correcting me.

#### **Coextension Bug In GNAT**

From: Jere <jhb.chat@gmail.com> Subject: Potential Coextension Bug in GNAT

Newsgroups: comp.lang.ada Date: Thu, 20 Dec 2018 07:59:00 -0800

I was messing around and trying to learn coextensions and I came across some counter intuitive functionality. If I directly initialize one via an aggregate, it works fine.

However, if I initialize through a constructing function, it seems to treat the access discriminant as a normal access type and finalizes it at the end of the program instead of when the object leaves scope. I don't fully understand them yet and there isn't much on them listed in the RM but one section (at least according to the index)[1]. That one section does indicate that initialization via a function should be valid however, so maybe I am back to I am doing it wrong or potentially a GNAT bug.

I'm using GNAT 7.1.1

Here is my test program

with Ada.Text\_IO; use Ada.Text\_IO; with Ada.Finalization; use Ada.Finalization;

#### procedure Hello is

#### overriding

procedure Finalize(Self : in out Thing\_1)

is

begin

Put\_Line("Finalize Thing\_1");

end Finalize;

type Thing\_2 (Other : not null access Thing\_1) is limited null record;

- procedure Test\_Coextension\_1 is

The\_Thing : Thing\_2(new Thing\_1);

begin

Put\_Line("Coextension directly

- initialized"); end Test\_Coextension\_1;

function Make\_Thing\_2 return Thing\_2 is begin

return (Other => **new** Thing\_1); **end** Make\_Thing\_2;

procedure Test\_Coextension\_2 is

The\_Thing : Thing\_2 := Make\_Thing\_2;

begin

Put\_Line("Coextension initialized

through build in place");

end Test\_Coextension\_2;

#### begin

Test\_Coextension\_1; Test\_Coextension\_2; Put\_Line("Test Finished"); end Hello;

#### Any thoughts?

[1] Ada 2012 tc1 RM 3.10.2(14.4/3) http://www.ada-auth.org/standards/ rm12 w tc1/html/RM-3-10-2.html#I2301

From: Jere <jhb.chat@gmail.com> Subject: Re: Potential Coextension Bug in GNAT Newsgroups: comp.lang.ada

Date: Thu, 20 Dec 2018 08:02:27 -0800 > [...]

~ [···]

Sorry, forgot to put the program output:

```

$gnatmake -o hello *.adb

```

gcc -c hello.adb

gnatbind -x hello.ali

gnatlink hello.ali -o hello

\$hello

Coextenson directly initialized

Finalize Thing\_1

Coextension initialized through build in

place

Test Finished

Finalize Thing\_1

Ada User Journal

From: Simon Wright <simon@pushface.org> Subject: Re: Potential Coextension Bug in GNAT Newsgroups: comp.lang.ada Date: Thu, 20 Dec 2018 16:56:11 +0000 > [\_]

Compiling with -gnatwa I see "warning: coextension will not be finalized when its associated owner is deallocated or finalized", so GNAT clearly meant to do it!

From: "Randy Brukardt" <randy@rrsoftware.com> Subject: Re: Potential Coextension Bug in GNAT Newsgroups: comp.lang.ada

Date: Thu, 20 Dec 2018 20:16:09 -0600

This message is nonsense, because a coextension is effectively part of the associated object. What they presumably mean to say is that the declaration in question is \*not\* a coextension, thus it will not be finalized with the owner.

P.S. I hate coextensions. One of the least necessary complications of Ada.

(Janus/Ada gives you a "feature not implemented" message if you try to create one.)

From: Jere <jhb.chat@gmail.com> Subject: Re: Potential Coextension Bug in GNAT

*Newsgroups: comp.lang.ada Date: Fri, 21 Dec 2018 03:24:43 -0800*

>[...]

> Compiling with -gnatwa I see "warning: coextension will not be finalized when its associated owner is deallocated or finalized", so GNAT clearly meant to do it!

that's pretty interesting. The compiler I was using did not give that warning when compiled with -gnatwa. You're right, that definitely looks intentional.

From: Simon Wright

<simon@pushface.org> Subject: Re: Potential Coextension Bug in GNAT

Newsgroups: comp.lang.ada

Date: Thu, 20 Dec 2018 17:58:11 +0000

>[...]

> procedure Test\_Coextension\_1 is

> The\_Thing : Thing\_2(new Thing\_1);

This is a case of 14.1/3, an allocator used to define the discriminant of an object,

> begin

> Put\_Line("Coextension directly

initialized");

> end Test\_Coextension\_1;

> function Make\_Thing\_2 return

Thing\_2 is

> begin

return (Other  $\Rightarrow$  new Thing 1);

I think GNAT thinks this is a case of 14.2/3, an allocator used to define the constraint in a subtype\_indication, though I'm hard put to it to see the difference from the first case.

From: "Randy Brukardt"

<randy@rrsoftware.com> Subject: Re: Potential Coextension Bug in GNAT

Newsgroups: comp.lang.ada Date: Thu, 20 Dec 2018 20:25:40 -0600

> This is a case of 14.1/3, an allocator used to define the discriminant of an object,

Right, because 14.2/3 says "subtype\_indication in any other context", meaning that 14.1/3 applies in an object declaration.

> I think GNAT thinks this is a case of 14.2/3, an allocator used to define the constraint in a subtype indication, though I'm hard put to it to see the difference from the first case.

That doesn't make any sense, since 14.2/3 is talking about a syntactic subtype\_indication, and there is no subtype\_indication in the above aggregate. 14.2/3 would be talking about a case like:

#### function Make\_Thing\_3 return Thing\_2 is subtype Silly is Thing\_2 (new Thing\_1); Some\_Thing : Silly;

begin return Some\_Thing; end Make Thing 3;

This function does NOT define a coextension.

So it does look like a GNAT bug. There is the possibility that they are associating the discriminant with the temporary object associated with the allocator, and not the return object, but that seems unnecessarily unfriendly of an interpretation. And it would be wrong for any type that requires built-in-place (I didn't look at the actual declaration of the type). I think the rules are supposed to prevent that interpretation, but whether they really do is an interesting question that I have no interest in exploring.

P.S. Did I mention I hate coextensions?? They provide an endless opportunity to puzzle over rules that really don't matter in the end (and most likely aren't quite right). I suppose they've helped me keep employed running the ARG. :-)

From: Jere <jhb.chat@gmail.com> Subject: Re: Potential Coextension Bug in

GNAT Newsgroups: comp.lang.ada Date: Fri, 21 Dec 2018 03:32:03 -0800

> So it does look like a GNAT bug. There is the possibility that they are associating the discriminant with the temporary object associated with the allocator, and not the return object, but that seems unnecessarily unfriendly of an interpretation. And it would be wrong for any type that requires builtin-place (I didn't look at the actual declaration of the type). I think the rules are supposed to prevent that interpretation, but whether they really do is an interesting question that I have no interest in exploring.

Ok, that makes me feel better. I was concerned I was misinterpreting the RM about the function return (for build in place). The type was limited, which I believe requires it to be built in place.

> P.S. Did I mention I hate coextensions?? They provide an endless opportunity to puzzle over rules that really don't matter in the end (and most likely aren't quite right). I suppose they've helped me keep employed running the ARG. :-)

Overall, they aren't super useful and are not very intuitive. I don't know the history for why they were added to the language though. I will say they do provide one thing to Ada that no other feature in the language seems to, so there is that. But I don't know the cost versus reward of them.

#### grpexec Tool

From: VM Celier <vmcelier@gmail.com> Subject: New tool "gprexec", basically "make with project file" Newsgroups: comp.lang.ada Date: Fri, 11 Jan 2019 14:00:10-0800

I am starting a new project that I have

been thinking for several years: gprexec. gprexec is a "Make build automation tool using GPR project files to describe goals, dependencies, and processes".

It uses a new package: Execution.

Here is an example of a project that can be used by gprexec:

project Toto is

- for Main use ("toto.adb"); package Execution is for Process ("display\_main") use ("cat", "toto.adb");

- for Dependency ("display") **use** ("display\_main"); for Process ("display") **use** ("cat",

"toto.gpr"); for Process ("date") use ("date");

- for Dependency ("default") use ("display", "toto", "date");

for Process ("default") use ("toto");

#### end Execution; end Toto:

Package Execution has these attributes:

- Dependency, to indicate the goals that need to be processed before the indexed goal. - Process, to indicate the process to be invoked, with its arguments, for the indexed goal.

gprexec needs to be invoked with a single project file and an optional goal. When no goal is specified on the command line, the goal "default" is implied.

For example with the project file toto.gpr above, invoking

gprexec toto.gpr

the goal default will be used, and according to the dependencies processes will be invoked in the following order:

(goal "display\_main): cat toto.adb

(goal "display"): cat toto.gpr

(goal "toto"): gprbuild -f -q toto.gpr

(goal "date"): date

(goal "default"): toto

After displaying the main toto.adb and the project file toto.gpr, toto.adb is compiled, bound and linked, the date is displayed and the executable "toto" is invoked.

gprexec uses the project file "gpr.gpr", part of the gprbuild repository.

I just created a public repository for gprexec on Github:

https://github.com/vmcelier/gprexec

Anybody interested?

-- Vincent Celier

(no longer associated with AdaCore)

From: Shark8

<onewingedshark@gmail.com>

Subject: Re: New tool "gprexec", basically

"make with project file"

Newsgroups: comp.lang.ada Date: Mon, 14 Jan 2019 13:06:35 -0800

Yes, but no.

Some of the ideas behind GPR are good, but if we're being honest its tendency to be "stringly-typed" is annoying given its obvious designed similarity to Ada -- and there are a lot of missed opportunities -and the sort-of configuration purposes which don't fully support producing an Ada executable (e.g. IIRC you have to use a completely separate configuration to handle DSA.)

From: VM Celier <vmcelier@gmail.com> Subject: Re: New tool "gprexec", basically "make with project file" Newsgroups: comp.lang.ada

Date: Mon, 14 Jan 2019 16:49:14 -0800

> Some of the ideas behind GPR are good, but if we're being honest its tendency to be "stringly-typed" is annoying given its obvious designed similarity to Ada

It is true that the syntax of the project language is similar to the one of Ada, but there is a big difference between the two languages: - Ada is an executable language

- the project language is a declarative language

You don't "execute" project files, you use it to describe a system for different tools. This is why there are almost no types in the project language because types are not really needed and they would complexify the language for no real benefit.

> -- and there are a lot of missed opportunities

Could you tell us one or two of these missed opportunities?

#### From: Shark8

<onewingedshark@gmail.com>

Subject: Re: New tool "gprexec", basically

"make with project file"

Newsgroups: comp.lang.ada

Date: Tue, 15 Jan 2019 08:41:01 -0800

- > It is true that the syntax of the project language is similar to the one of Ada, but there is a big difference between the two languages:

- > Ada is an executable language

- > the project language is a declarative language

This is actually less of an issue than might be thought; though some of the "fix-ups" might be a bit stifling to some. You could, for example, impose restrictions/mandatory-structure on the configuration and have all configurations be valid Ada.

> You don't "execute" project files, you use it to describe a system for different tools. This is why there are almost no types in the project language because types are not really needed and they would complexify the language for no real benefit.

No, real enumerations (and attendant Ada-like case-coverage) would be excellent for providing bounded alternations of the configuration.

- >> -- and there are a lot of missed opportunities

- > Could you tell us one or two of these missed opportunities?

Given Ada's strong generic-system configurations could be described as generic parameters [esp enumerations], which the tools could use to provide bounded options in the absence of defaults.

#### Package PROJECT\_NAME

#### From: Shark8

<onewingedshark@gmail.com>

Subject: Re: New tool "gprexec", basically

"were with any int flow"

"make with project file" Newsgroups: comp.lang.ada

Date: Tue, 15 Jan 2019 09:22:07 -0800

Sorry, I accidentally submitted the form while composing my example... which is here:

<sup>&</sup>gt;[...]

Package PROJECT\_NAME is Type Archetectures is ( x86, x86\_64, ARM, SPARC, MIPS\_V ); Type Node\_Type is (Storage, Processing); Type Partition\_Type is (Active, Passive); Type Compilation\_Parameters is record CPUs : Natural := 0; -- Use as many -- cores as available. Symbols : Boolean := True; -- Don't strip -- symbols. Target : Archetectures;

end record;

Type Partition( Params : Compilation\_Parameters; Style : Partition\_Type ) is record null; --... Other DSA parameters. end record;

Type Node( Style : Node\_type ) is record Archetecture : Archetectures; case Style is when Storage => null; --... when Processing => null; --... end case;

end record;

#### Generic

Params : Compilation\_Parameters; **Procedure** Compile;

--- CONCEPTUAL GENERIC PACKAGE Generic Partitions : Array (Positive range <>) of

not null access Partition; Package Compiler is Procedure Execute; End Compiler;

--- CONCEPTUAL BODY FOR COMPILER Package Body Compiler is

Procedure Execute is Begin

For P of Partitions loop

declare Procedure Make is new Compile( P.Params); begin Make; end;

#### End loop;

End Execute; End Compiler;

End PROJECT\_NAME;

Now, obviously there would have to be standardization -- and it would probably work better if "Archetectures" were a parameter to PROJECT\_NAME -because if all config-packages were generic we could "nest" dependencies:

#### Generic

Type STANDARD\_PARAM is limited private;

-- "Configuration standard param" with Package P1 is new Project\_1 (STANDARD\_PARAM); with Package P2 is new Project\_2 (STANDARD\_PARAM); -- P3 depends on P1&2

Ada User Journal

with Package P3 is new Project\_3 (STANDARD\_PARAM, P1, P2 );

Package Project\_4 is --... STANDARD STRUCTURE. End Project 4:

Now, all of that is operating with the idea of using Ada as a config-language, which is doable, but perhaps a bit ugly... It might be a bit better to sit down, think about configurations (esp. in the presence of DSA) and develop an Ada-like language for that. (Perhaps in conjunction with a new Ada IR similar to DIANA, such that this configuration-description "compiles down to" the proper generic-nodes which can then be interpreted by the compiler as the configuration[s] to use; or processed by tools to inter-operate with current tools [ie IR  $\rightarrow$  (GPR File, Gnatdist Configuration File) for GNAT].)

#### **Program entry in GPR**

From: Jesper Quorning <jesper.quorning@gmail.com> Subject: Package procedure as program entry in GPR project Newsgroups: comp.lang.ada Date: Fri, 25 Jan 2019 07:12:22 -0800 Hello All,

With the package specification:

package My\_Program\_Package is

procedure Program\_Entry\_Procedure;

end My\_Program\_Package;

How do i make Program\_Entry\_Procedure as the program entry procedure in a GPR project?

I think it is possible, but cannot find out how.

I know how to use a stand-alone procedure file as program entry and how to name the executable.

From: Jere <jhb.chat@gmail.com> Subject: Re: Package procedure as program entry in GPR project Newsgroups: comp.lang.ada Date: Fri, 25 Jan 2019 09:05:24 -0800

#### >[...]

With that specific setup, I am not sure. But if you are willing to change a couple of things you can do:

-- my\_program\_package.ads

- package My\_Program\_Package is

- -- Notice no declaration here for the

- -- procedure, but you can put other -- things if you like

- end My\_Program\_Package;

-- my\_program\_packageprogram\_entry\_procedure.adb procedure My\_Program\_Package. Program\_Entry\_Procedure is begin

-- your main stuff end My\_Program\_Package. Program\_Entry\_Procedure; Then you modify the GPR file to point to it as the main:

for Main use ("my\_program\_packageprogram\_entry\_procedure.adb");

I do something similar for my Gnoga GUI projects so I can have program level stuff in the top package but have the main a child of that top level package.

From: "Randy Brukardt"

<randy@rrsoftware.com>

Subject: Re: Package procedure as program entry in GPR project

Newsgroups: comp.lang.ada Date: Fri, 25 Jan 2019 15:42:12 -0600

>[...]

I realize you are asking for GPR, so by definition you don't care about portability, but:

Ada only requires Ada implementations to support library-level procedures as the main. See 10.2(29). A particular implementation can allow more, but there is no requirement.

So if you ever might want to use some other Ada compiler (I for one, hope so), use such a routine.

It's trivial to write one, after all:

with My\_Program\_Package; procedure My\_Program\_Main is begin

My\_Program\_Package. Program\_Entry\_Procedure; end My Program Main;

From: Jesper Quorning

<jesper.quorning@gmail.com>

Subject: Re: Package procedure as program

entry in GPR project

Newsgroups: comp.lang.ada Date: Fri, 25 Jan 2019 17:47:30 -0800

I just wanted a way to avoid the trivial main file.

I also considered

package simple is

procedure main

end simple;

package body simple is procedure main is begin

end main;

#### private main:

end simple;

But GPR would not do that either. I will stick to the simple procedure file.

From: Simon Wright <simon@pushface.org> Subject: Re: Package procedure as program entry in GPR project Newsgroups: comp.lang.ada Date: Sat, 26 Jan 2019 12:05:35 +0000 This isn't a GPR thing, it's a GNAT thing: GNAT has no extensions here beyond the requirement.

If you have a minimal bare-board project without any requirement for the Ada runtime system, it's possible to do what you ask: see Maciej Sobczak's 'Ada and SPARK on ARM Cortex-M' tutorial[1], in particular the 'First Chapter'[2].

It would be hard (and pointless) to attempt this for a program intended to run on a typical operating system.

[1] http://www.inspirel.com/articles/ Ada On Cortex.html

[2] http://www.inspirel.com/articles/ Ada\_On\_Cortex\_First\_Program.html

#### **GNAT Bug**

From: George Shapovalov <gshapovalov@gmail.com> Subject: Yet another gnat bug Newsgroups: comp.lang.ada Date: Fri, 1 Feb 2019 06:51:50-0800

This will probably sound more like venting frustration. Sorry if so. But how does anybody get anything done? gnat is \*the major\* Ada compiler and pretty much the only one implementing the standard in full. Yet I cannot seem to get it working past really small size in any project. As soon as I try to get any basic type composition done (only 3-4 inheritance levels, with, perhaps double interface overlay), I get that dreaded gnat bug message.. This is at least the 3rd one just within past week or two..

Specifically this:

https://github.com/gerr135/wann/tree/ gnat bug01

(the bug triggering code is in a separate branch pointed to by that link).

This is still early in design phase and far from being functional in any way, so I don't really expect much comments on the code itself (thus that "venting frustration" comment above). But the pattern that seems to universally trigger these gnat bugs is something along these lines:

type Base\_Interface is interface;

type Derived1\_Interface is new Base\_Interface and ..;

perhaps few more layers here ...

then

type Base\_impl1 is new Base\_Interface with

private;

type Derived1 is new Base\_impl1 and Derived1\_Interface with private..

basically trying to stitch together functional interface hierarchy (containing algorithmic stuff) and data storage type hierarchy. Somehow gnat very often just cannot handle this type of design :(.

(and yes, I am avoiding having to lay generics on top of other generics like Dmitry suggests - keeps design and compilation times sane, but apparently overloads gnat capacity to deal with abstraction).

So, I guess my question would be - how people deal with such situations (combining algorithmic and data representation type hierarchies) in their experience? Or, whether too many child modules makes any difference? I seem to have noticed that the more hierarchical my packages are (but this one is only like 3rd level child!) the more often I trigger that gnat bug message.. (but then keeping the code in one huge module is really messy too!)

And yeah, the specific message here is:

gprbuild -P wann.gpr

Compile

[Ada] run\_customnn.adb

+===GNAT BUG DETECTE===+ | Community 2018 (20180524-73)

(x86\_64-pc-linux-gnu) GCC error: |

| in gnat\_to\_gnu\_entity, at ada/gccinterface/decl.c:429 |

| Error detected at wann-nets-vectors.ads: 106:5 [run\_customnn.adb:23:5] |

| Please submit a bug report by email to report@adacore.com. |

| GAP members can alternatively use GNAT Tracker: |

$\mid$  http://www.adacore.com/ section 'send a report'.  $\mid$

See gnatinfo.txt for full info on procedure for submitting bugs.

|Use a subject line meaningful to you and us to track the bug.

| Include the entire contents of this bug box in the report.

| Include the exact command that you entered.

Also include sources listed below.

| Use plain ASCII or MIME attachment(s).

and the "please include" list of files lists pretty much all of them in the src dir.

But as I said, this is rather a pattern I observe, not just one-off situation..

This is with the latest FSF gnat compiler (2018 release based on gcc-7.3.1 backend, Gentoo Linux, relatively fresh everything else).

Sigh, I guess another report to file with AdaCore..

Sorry for disturbance here ...

From: "Dmitry A. Kazakov"

<mailbox@dmitry-kazakov.de> Subject: Re: Yet another gnat bug Newsgroups: comp.lang.ada Date: Fri, 1 Feb 2019 19:47:31 +0100

> So, I guess my question would be - how people deal with such situations (combining algorithmic and data representation type hierarchies) in their experience? Or, whether too many child modules makes any difference? I seem to have noticed that the more hierarchical my packages are (but this one is only like 3rd level child!) the more often I trigger that gnat bug message.

Do not panic. In many cases the bug is triggered by an illegal program. Try an older version of GNAT compiler to find what triggers it. In other cases you can work around it using minor code variations.

From: George Shapovalov <gshapovalov@gmail.com> Subject: Re: Yet another gnat bug Newsgroups: comp.lang.ada Date: Fri, 1 Feb 2019 13:32:52 -0800

>[...]