# The journal for the international Ada community

# Ada User Journal

Volume 42 Number 2 June 2021

101

105

109

113

117

121

125

| I PATTON BLL  | Editorial    |

|---------------|--------------|

| Quarterly Nev | ws Digest    |

| Conference    | $\mathbf{U}$ |

| Forthcomi     | ng Events    |

# Articles from the AEiC 2021 Work in Progress Session

A. Amurrio, E. Azketa, M. Aldea Rivas, J.J. Gutiérrez How Windows Size and Number can Influence the Schedulability of Hierarchically-Scheduled Time-Partitioned Real-Time Systems

> C. Castagna, D. Cancila, A. Cammi Adoption of ACPS in Nuclear Reactor Analysis

J.S. Kimmet Auto-generated Coherent Data Store for Concurrent Modular Embedded Systems

M. Aldea Rivas, H. Pérez Tijero M2OS for Arduino Uno: Ada Tasks and Arduino Libraries Working Together

> F. Siebert Fuzion — Safety through Simplicity

H. Pérez Tijero, D. García Prieto, J.J. Gutiérrez First Steps towards an IEEE 802.1AS Clock for EDF Scheduling in Distributed Real-Time Systems

# Puzzle

| J. Barnes                                                       |  |

|-----------------------------------------------------------------|--|

| J. Barnes<br>Pyramids, Reduction Expressions, and Final Puzzles |  |

# **Produced by Ada-Europe**

# **Editor in Chief**

António Casimiro

University of Lisbon, Portugal AUJ\_Editor@Ada-Europe.org

# Ada User Journal Editorial Board

| <b>Luís Miguel Pinho</b>                         | Polytechnic Institute of Porto, Portugal                                     |

|--------------------------------------------------|------------------------------------------------------------------------------|

| Associate Editor                                 | lmp@isep.ipp.pt                                                              |

| <b>Jorge Real</b><br>Deputy Editor               | Universitat Politècnica de València, Spain <i>jorge@disca.upv.es</i>         |

| <b>Patricia López Martínez</b>                   | Universidad de Cantabria, Spain                                              |

| Assistant Editor                                 | lopezpa@unican.es                                                            |

| Kristoffer N. Gregertsen                         | SINTEF, Norway                                                               |

| Assistant Editor                                 | kristoffer.gregertsen@sintef.no                                              |

| <b>Dirk Craeynest</b>                            | KU Leuven, Belgium                                                           |

| <i>Events Editor</i>                             | Dirk.Craeynest@cs.kuleuven.be                                                |

| <b>Alejandro R. Mosteo</b><br><i>News Editor</i> | Centro Universitario de la Defensa, Zaragoza, Spain <i>amosteo@unizar.es</i> |

### **Ada-Europe Board**

| <b>Tullio Vardanega</b> (President)<br>University of Padua                    | Italy          |

|-------------------------------------------------------------------------------|----------------|

| <b>Dirk Craeynest</b> (Vice-President)<br>Ada-Belgium & KU Leuven             | Belgium        |

| <b>Dene Brown</b> (General Secretary)<br>SysAda Limited                       | United Kingdom |

| Ahlan Marriott (Treasurer)<br>White Elephant GmbH                             | Switzerland    |

| <b>Luís Miguel Pinho</b> (Ada User Journal)<br>Polytechnic Institute of Porto | Portugal       |

| António Casimiro (Ada User Journal)<br>University of Lisbon                   | Portugal       |

# **Ada-Europe General Secretary**

Dene Brown SysAda Limited Signal Business Center 2 Innotec Drive BT19 7PD Bangor Northern Ireland, UK Tel: +44 2891 520 560 Email: Secretary@Ada-Europe.org URL: www.ada-europe.org

## Information on Subscriptions and Advertisements

Ada User Journal (ISSN 1381-6551) is published in one volume of four issues. The Journal is provided free of charge to members of Ada-Europe. Library subscription details can be obtained direct from the Ada-Europe General Secretary (contact details above). Claims for missing issues will be honoured free of charge, if made within three months of the publication date for the issues. Mail order, subscription information and enquiries to the Ada-Europe General Secretary.

For details of advertisement rates please contact the Ada-Europe General Secretary (contact details above).

# ADA USER JOURNAL

# Volume 42 Number 2 June 2021

n

# Contents

|                                                                                                                                                                                                     | Page        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Editorial Policy for Ada User Journal                                                                                                                                                               | 62          |

| Editorial                                                                                                                                                                                           | 63          |

| Quarterly News Digest                                                                                                                                                                               | 64          |

| Conference Calendar                                                                                                                                                                                 | 94          |

| Forthcoming Events                                                                                                                                                                                  | 99          |

| Articles from the AEiC 2021 Work-In-Progress Session                                                                                                                                                |             |

| A. Amurrio, E. Azketa, M. Aldea Rivas, J. J. Gutiérrez<br>"How Windows Size and Number Can Influence the Schedulability of Hierarchically-Schedu<br>Time-Partitioned Distributed Real-Time Systems" | ıled<br>101 |

| C. Castagna, D. Cancila, A. Cammi<br>"Adoption of ACPS in Nuclear Reactor Analysis"                                                                                                                 | 105         |

| J. S. Kimmet<br>"Auto-generated Coherent Data Store for Concurrent Modular Embedded Systems"                                                                                                        | 109         |

| M. Aldea Rivas, H. Pérez Tijero<br>"M2OS for Arduino Uno: Ada Tasks and Arduino Libraries Working Together"                                                                                         | 113         |

| F. Siebert<br>"Fuzion – Safety through Simplicity"                                                                                                                                                  | 117         |

| H. Pérez Tijero, D. García Prieto, J. J. Gutiérrez<br>"First Steps Towards an IEEE 802.1AS Clock for EDF Scheduling in Distributed<br>Real-Time Systems"                                            | 121         |

| Puzzle                                                                                                                                                                                              |             |

| J. Barnes<br>"Pyramids, Reduction Expressions, and Final Puzzles"                                                                                                                                   | 125         |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                                                                           | 126         |

| Ada-Europe Sponsors Inside B                                                                                                                                                                        | ack Cover   |

# Editorial Policy for Ada User Journal

### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

### **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

With this issue we bring what we believe are good news for most of our subscribers concerning the distribution of the physical copies of the AUJ. Copies will now be sent directly to each subscriber from the printer, instead of being sent firstly, in bulk, to each national body and then, from there, to each destination. For direct members nothing will change. We believe that this simplification is beneficial for everyone.

Concerning this June issue, we start the publication of the articles presented at Work-In-Progress (WiP) Session of the Ada-Europe International Conference on Reliable Software Technologies (AEiC 2021). This year the conference took place as a virtual event, which was a new and quite positive experience for many attendants. Hopefully it will be possible to regain the physical presence next year, but even if not, we can now rest assured that running the conference virtually is a viable option.

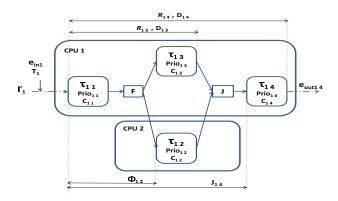

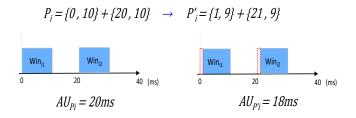

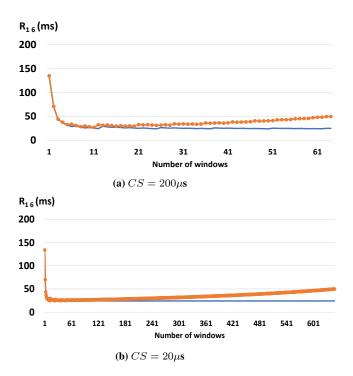

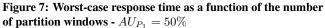

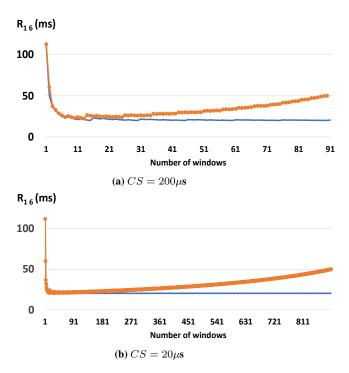

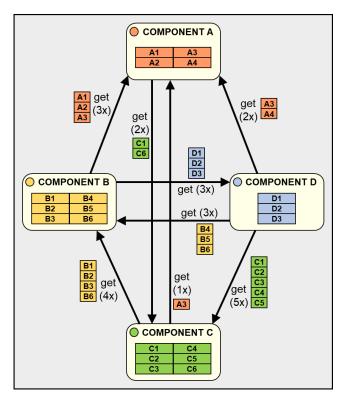

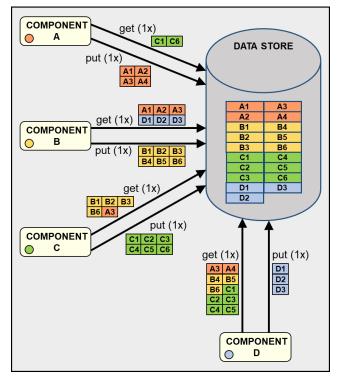

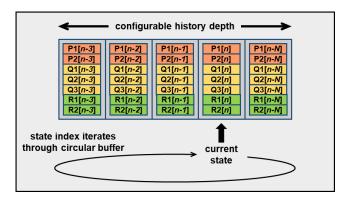

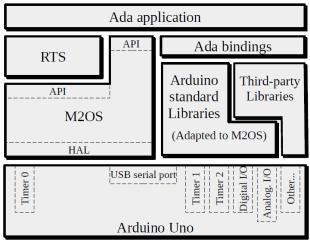

The six articles included in the issue are the following. Firstly, a contribution authored by A. Amurrio and E. Azketa from the Ikerlan Technology Research Centre, and by M. Aldea Rivas and J. Javier Gutiérrez, from the University of Cantabria. The article investigates the influence of partition windows on the task response time in hierarchically scheduled time partitioned distributed systems. Then, the article "Adoption of ACPS in Nuclear Reactor Analysis", authored by C. Castagna, D. Cancila and A. Cammi, looks at the problem of bounding the uncertainty in the design of these safety-critical CPS, which is made harder due to its multidisciplinary nature. The third article is single authored, by James S. Kimmet from Raytheon Missiles & Defense, describing a data store that was developed to be used in concurrent real-time systems, ensuring that the shared data is kept always coherent. The fourth article provides another contribution coming from the University of Cantabria, in this case authored by M. Aldea Rivas and H. Pérez Tijero. The article provides the status of an ongoing project that aims at porting M2OS, a small the real-time operating system, to the Arduino Uno platform. Then, the article "Fuzion – Safety through Simplicity", by Dr. Fridtjof Siebert from Tokiwa Software GmbH, introduces the Fuzion programming language, which provides several interesting features. The language combines a powerful syntax with safety features, meant for high-performance safety-critical applications. Finally, yet another paper from the University of Cantabria, by H. Pérez Tijero, D. García Prieto, and J. Javier Gutiérrez, that introduces a new solution for exploiting EDF scheduling and synchronized clocks in a distributed real-time system, to consider end-to-end global deadlines and achieve improvements in resource utilization.

As usual, the issue includes the Quarterly News Digest, prepared by Alejandro R. Mosteo, and the Calendar and Events sections, prepared by Dirk Craeynest. The issue closes with another and final note by John Barnes on puzzles that have been presented in past editions of the Ada-Europe conference. The solution for the pyramids puzzle from the March issue is provided, and the four puzzles mentioned at this year's conference, along with their solutions, are also included in the note. We are very grateful to John Barnes for his continued contribution to the AUJ over the past year. Thank you!

Antonio Casimiro Lisboa June 2021 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

# Alejandro R. Mosteo

Centro Universitario de la Defensa de Zaragoza, 50090, Zaragoza, Spain; Instituto de Investigación en Ingeniería de Aragón, Mariano Esquillor s/n, 50018, Zaragoza, Spain; email: amosteo@unizar.es

# Contents

| Preface by the News Editor | 64 |

|----------------------------|----|

| Ada-related Events         | 64 |

| Ada Semantic Interface     |    |

| Specification              | 67 |

| Ada and Education          | 68 |

| Ada-related Resources      | 68 |

| Ada-related Tools          | 69 |

| Ada and Operating Systems  | 77 |

| Ada and Other Languages    | 77 |

| Ada Practice               | 80 |

|                            |    |

[Messages without subject/newsgroups are replies from the same thread. Messages may have been edited for minor proofreading fixes. Quotations are trimmed where deemed too broad. Sender's signatures are omitted as a general rule. —arm]

# Preface by the News Editor

#### Dear Reader,

This period saw the celebration of the Ada-Europe conference, after a year of hiatus, and only in virtual form. This is cause for celebration and a signal of hope for Adaists to meet again in the future in this close-knit event where one can mingle with newcomers, old faces, and the "guiding lights" of the language alike. Announcements about the event, for the record, are found in this number [1].

Another yearly moment of excitement for the Ada open source community is the release of the GNAT Community Edition, which we witnessed at the end of May [2]. And, speaking of open source communities, I will mention the mass exodus from the Freenode chat network due to a change in ownership and policies. The dwellers of #ada have chosen, on the 20th anniversary of the channel, the Libera Chat network as a new home. The thread announcing the news [3] is also a reminiscence about other venerable technologies that, like IRC and Usenet, still are going around.

In another curious development, a mostly off-topic thread that had seen its last post in 2014 was somehow revived, and I cannot resist reading about the computing anecdotes of times long past, in this case framed in a "Pascal vs C" context [4].

The polemic topic about Ada itself in this number was Unicode, or Ada lackluster support thereof, according to some. Opinions, hopes for a brighter future, and insights on how it came to be in its present form are discussed in [5].

### Sincerely,

Alejandro R. Mosteo.

- "Ada-Europe Int. Conf. on Reliable Software Technologies, AEiC 2021", in Ada-related Events.

- [2] "GNAT CE 2021", in Ada-related Tools.

- [3] "Ada IRC Channel Migrates to Libera Chat", in Ada Practice.

- [4] "Pascal vs C Language Families", in Ada and Other Languages.

- [5] "Ada and Unicode", in Ada Practice.

# Ada-related Events

# Ada-Europe Int. Conf. on Reliable Software Technologies, AEiC 2021

[Past event, for the record. -arm]

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be> Subject: Ada-Europe Int.Conf. Reliable Software Technologies, AEiC 2021 Date: Tue, 27 Apr 2021 17:46:30 -0000 Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

#### Call for Participation

#### \*\*\* PROGRAM SUMMARY \*\*\*

25th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2021)

7-10 June 2021, Virtual Event

www.ada-europe.org/conference2021

- Organized by University of Cantabria and Ada-Europe in cooperation with ACM SIGAda, SIGPLAN, SIGBED

- and the Ada Resource Association (ARA)

#AEiC2021 #AdaEurope #AdaProgramming

#### General Information

The 25th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2021), initially scheduled to take place in Santander, Spain, will be held online from the 7th to the 10th of June 2021, using the underline.io conference platform.

The conference program includes parallel tutorials on Monday 7th, and a technical program and vendor exhibition from Tuesday to Thursday. The conference also includes breaks and virtual social events that will allow networking among the participants.

#### Overview of the Week

#### Monday 7th

- Welcome Social Event

- 5 Parallel Tutorials

- Ice-Breaking Social Event

#### Tuesday 8th

- Ice-Breaking Social Event and Opening

- Techn. Session 1: Scheduling and

- mixed-criticality systems

- Keynote 1

- Techn. Session 2: Software modeling

- Social Event

# Wednesday 9th

- Welcome Social Event

- Techn. Session 3: Autonomous systems

- Work-in-Progress Session

- Keynote 2

- Techn. Session 4: Ada issues and Ravenscar

- Social Event

- Thursday 10th

- Welcome Social Event

- Techn. Session 5: Validation and verification tools

- Techn. Session 6: Emerging applications with reliability requirements

- Keynote 3

- Techn. Session 7: Safety challenges

- Best Presentation Award, Closing Session and Party

The program runs between 12:30 and 18:30 CEST, to allow participation from different time zones. For full details and

up-to-date information, see the conference web page: http://www.ada-europe.org/ conference2021

#### Keynote Talks

In each of the three main conference days, a keynote will be delivered to address hot topics of relevance in the conference scope, with ample time for questions and answers. The keynotes will be:

- Ángel Conde, Data Analytics and Artificial Intelligence team leader at IKERLAN (Spain), who will present his work on "Software reliability in the Big Data era with an industry-minded focus".

- Alfons Crespo, who is with the Institute of Automation and Industrial Informatics of the Universitat Politècnica de València (Spain), will give an answer to the question "Why hypervisor-based approach is the best alternative for mixed-criticality systems".

- Tucker Taft, who is Director of Language Research at AdaCore (USA), will talk on "A sampling of Ada 2022".

### **Technical Sessions**

Given the current sanitary situation and the need to resort to a virtual format for the conference, we will all experience the advantages and benefits of exploring new formats. The technical sessions are designed with the flipped-conference concept, where the audience can access the pre-recorded presentation materials in advance and the live sessions are devoted to short presentations of the highlights of each contribution, allowing ample time for questions and answers with the presenter. The recorded materials will also be available for some time after their sessions. The technical sessions include papers submitted to the journal track that are heading towards final acceptance and open-access publication, together with industrial, invited and vendor presentations.

#### Work-in-Progress Session

The Work-in-Progress session contains contributions of evolving and early-stage ideas, or new research directions. They are presented in a special session consisting of a round of very short presentations of the highlights of each contribution, followed by a poster session in the same virtual space where the breaks are held.

#### Exhibition

From Tuesday to Thursday the conference platform will provide access to virtual booths where participants will be able to find information on the conference exhibitors and chat with them or request meetings. The virtual break lounge where the breaks and social events will take place will also have a space for meeting with the exhibitors.

### **Tutorials**

Five four-hour parallel tutorials are offered on Monday 7th:

- TU-1: Programming mobile robots with ROS2 and the RCLAda Ada client library, by Alejandro R. Mosteo

- TU-2: Introduction to the development of safety critical software, by Jean-Pierre Rosen

- TU-3: Parallel programming with Ada and OpenMP, by Sara Royuela, S. Tucker Taft, Luis Miguel Pinho

- TU-4: Timing verification from UML & MARTE design models: techniques & tools, by Laurent Rioux, Julio Medina and Shuai Li

- TU-5: Programming shared memory computers, by Jan Verschelde

### Social Program

The virtual conference platform will offer a space under the gather.town environment to allow informal and lively gathering of the participants. This space may have different areas, such as rooms, tables, and corners where a participant can approach to talk through videoconferencing with participants in the same virtual area. This facility will be used for the breaks, poster session, exhibition and social events. Particular themes for some of the social events will be announced in the conference platform and in the web page.

#### Further Information

Participation for the full event, including tutorials, is free for Ada-Europe members and only 60 EUR for all others. Registration is required for all. The conference web page will shortly give full and up-to-date details on the program, the registration process and the virtual platform: http://www.adaeurope.org/conference2021

### AEiC 2021 Sponsors

- AdaCore: https://www.adacore.com/

- Ellidiss: https://www.ellidiss.com/

- PTC: http://www.ptc.com/ developer-tools

- Universidad de Cantabria: https://web.unican.es/en/

- Vector: https://www.vector.com/at/en/

The conference is supported and sponsored by

- Ada-Europe: http://www.ada-europe.org/

and organized in cooperation with

- ACM SIGAda: http://www.sigada.org/

- ACM SIGBED: https://sigbed.org/

- ACM SIGPLAN: http://www.sigplan.org/

- ARA:

https://www.adaic.org/community/

Our apologies if you receive multiple copies of this announcement.

Please circulate widely.

Dirk Craeynest, AEiC 2021 Publicity Chair (aka Ada-Europe 2021)

Dirk.Craeynest@cs.kuleuven.be

(V4.1)

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be> Date: Fri, 30 Apr 2021 07:59:16 -0000

Registration site for AEiC2021 is online: registration.ada-europe.org.

Register now for the 25th Ada-Europe Int'l Conference on Reliable Software Technologies!

# Press Release - AEiC 2021, Ada-Europe Reliable Softw. Technol.

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be>

Subject: Press Release - AEiC 2021, Ada-Europe Reliable Softw. Technol. Date: Sun, 30 May 2021 16:22:28 -0000 Newsgroups: comp.lang.ada, fr.comp.lang.ada,comp.lang.misc

FINAL Call for Participation

\*\*\* UPDATED Program Summary \*\*\*

25th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2021)

7-10 June 2021, Virtual Event

www.ada-europe.org/conference2021

\*\*\* Check out tutorials! \*\*\*

- www.ada-europe.org/conference2021/ tutorials.html

- \*\*\* Don't miss the thematic social events on Tuesday and Wednesday \*\*\*

- \*\*\* Full Program available on the conference web site \*\*\*

\*\*\* Register now! \*\*\*

#AEiC2021 #AdaEurope #AdaProgramming

#### Press release:

25th Ada-Europe Int'l Conference on Reliable Software Technologies International experts meet in virtual conference hosted by Underline Santander, Spain (31 May 2021) - Ada-

Europe together with the University of Cantabria, Spain organize from 7 to 10 June 2021 the 25th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2021). The conference was initially scheduled to take place in Santander, Spain. According to the safety and sanitary measures under the COVID-19 pandemic, this year the conference will be a virtual event, hosted by Underline (https://underline.io). The event is in cooperation with the Ada Resource Association (ARA), and with ACM's Special Interest Groups on Ada (SIGAda), on Embedded Systems (SIGBED) and on Programming Languages (SIGPLAN).

The Ada-Europe series of conferences has over the years become a leading international forum for providers, practitioners and researchers in reliable software technologies. These events highlight the increased relevance of Ada in general and in safety- and securitycritical systems in particular, and provide a unique opportunity for interaction and collaboration between academics and industrial practitioners.

This year's conference offers 5 tutorials, 3 keynotes, a technical program of 7 sessions with refereed papers, invited and industrial presentations, a work-in-progress session, an industrial exhibition and vendor presentations, and a social program.

Five parallel tutorials are scheduled on Monday, targeting different audiences:

- "Programming mobile robots with ROS2 and the RCLAda Ada client library", by Alejandro R. Mosteo;

- "Introduction to the development of safety critical software", by Jean-Pierre Rosen;

- "Parallel programming with Ada and OpenMP", by Sara Royuela, S. Tucker Taft, Luis Miguel Pinho;

- "Timing verification from UML & MARTE design models: techniques & tools", by Laurent Rioux, Julio Medina and Shuai Li;

- "Programming shared memory computers", by Jan Verschelde.

Tutorial registration is complementary for conference participants.

The industrial exhibition opens Tuesday under the Expo area in the virtual platform and also in the Lounge, which is the networking area. It runs until the end of Thursday afternoon. Exhibitors include AdaCore, PTC Developer Tools, and Ada-Europe. All conference participants are invited to the exhibition as well as to the virtual social events.

Three eminent speakers have been invited to deliver a keynote at each of the core conference days:

- Ángel Conde, Data Analytics and Artificial Intelligence team leader at IKERLAN (Spain), who will present his work on "Software reliability in the Big Data era with an industry-minded focus";

- Alfons Crespo, who is with the Institute of Automation and Industrial Informatics of the Universitat Politècnica de València (Spain), will give an answer to the question "Why hypervisor-based approach is the best alternative for mixed-criticality systems";

- Tucker Taft, who is Director of Language Research at AdaCore (USA), will talk on "A sampling of Ada 2022".

The technical program from Tuesday to Thursday presents 13 refereed technical papers and 5 invited, 6 industrial and 4 vendor presentations in sessions on:

- Scheduling and mixed-criticality systems,

- Software modeling,

- Autonomous systems,

- Ada issues and Ravenscar,

- Validation and verification tools,

- Emerging applications with reliability requirements,

- Safety challenges.

In addition, there is a work-in-progress session including 8 presentations and associated posters.

Peer-reviewed papers have been submitted to a special issue of the Journal of Systems Architecture and are heading towards final acceptance as open-access publications. Industrial and work-inprogress presentations, together with tutorial abstracts, will be offered publication in the Ada User Journal, the quarterly magazine of Ada-Europe.

The social program is hosted in a space under the gather.town environment that allows informal and lively gathering of the participants. This space has different areas, such as rooms, tables, and corners where a participant can approach to talk through videoconferencing with participants in the same virtual area. This facility will be used for the breaks, poster session, exhibition and social events. Don't miss the thematic social events at the end of each core conference day.

The Best Presentation Award will be offered during the Closing session.

The full program is available on the conference web site. Online registration is still possible.

Latest updates:

The "Final Program" is available at www.ada-europe.org/conference2021 /final-program.pdf.

Check out the tutorials in the PDF program, or in the schedule at

www.ada-europe.org/conference2021/ tutorials.html.

Registration fees are lower than ever and the registration process is done on-line. Don't delay for all details, select "Registration" at www.ada-europe.org/ conference2021 or go directly to https://registration.ada-europe.org.

The technical sessions are designed with the flipped-conference concept, where the audience can access pre-recorded presentation materials in advance. The live sessions are devoted to short presentations of the highlights of each contribution, allowing ample time for questions and answers with the presenter. The recorded materials will also be available for some time after their sessions.

The program runs between 12:30 and 18:30 CEST, to allow participation from different time zones. For more info and latest updates see the conference web site at www.ada-europe.org/conference2021.

AEiC 2021 is sponsored by AdaCore (www.adacore.com), Ellidiss (www.ellidiss.com), PTC Developer Tools (www.ptc.com/developer-tools), Universidad de Cantabria (web.unican.es/en), and Vector (www.vector.com/at/en).

Help promote the conference by advertising it.

Recommended Twitter hashtags: #AdaEurope and/or #AEiC2021.

Our apologies if you receive multiple copies of this announcement.

Please circulate widely.

Dirk Craeynest, AEiC 2021 Publicity Chair (aka Ada-Europe 2021),

Dirk.Craeynest@cs.kuleuven.be

\* 25th Ada-Europe Int. Conf. Reliable Software Technologies (AEiC 2021)

\* June 7-10, 2021 \* online event \* www.ada-europe.org/conference2021 \*\*

(V6.1)

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be> Date: Sun, 6 Jun 2021 10:11:09 -0000

If you plan to attend one of the #AEiC2021 #tutorials on Mon 7 Jun, don't forget to check the prerequisites: you may have to download material preferably before the tutorial starts.

See you at #AdaEurope's #OnlineConference soon!

# Ada Semantic Interface Specification

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be> Date: Thu, 10 Jun 2021 07:43:05 -0000

#AEiC2021 #AdaEurope #OnlineConference #AdaProgramming

Don't miss today's keynote!

Tucker Taft will present "A sampling of Ada 2022"

#### Abstract:

The forthcoming Ada 2022 revision of the Ada standard includes significant new features, which together make the language more expressive and productive in a multicore context, while enhancing its safety and support for more complete abstractions with formal contracts.

This talk will introduce these key new features with a series of examples:

- parallel loops and blocks, coupled with static detection of data races and potential blocking

- iterator syntax for incorporating filters and user-defined iterator procedureslibraries for atomic operations, including fetch-and-add and compare-and-swap

- aggregates, literals, images, and mapreduce for user-defined types

- libraries for arbitrary precision integer and rational arithmetic

- more expressive contracts using delta aggregates and declare expressions

- the Jorvik profile as the next step up from the Ravenscar profile

# **Call for Paper in CodeLand**

#### From: Mockturtle

<framefritti@gmail.com> Subject: Call for Paper in CodeLand Date: Sat, 26 Jun 2021 09:04:37 -0700 Newsgroups: comp.lang.ada

I just "tripped over" a CFP for the event CodeLand (link at the end). They accept proposals for 15-minutes pre-recorded video talk; deadline 20th of July.

CodeLand's primary audience is earlycareer programmers and their mentors. Among the themes I see "Technical Deep Dives" and "Path to Programmer" that could maybe be suitable for something Ada-related.

Is maybe someone interested in proposing something? I am going to think about it...

Summary of the most important info

- \* When: September 23-24, 2021

- \* How: virtual only, pre-recorded video

- \* Deadline: July 20, 2021 at 11:59pm UTC.

- \* Acceptance/reject date: August 17, 2021.

- \* Themes

- Code for Good

- Early-career confidence

- Open source strong

- Path to programmer

- Technical deep dives

- \* More info:

https://cfp.codelandconf.com/events/ codeland-2021

Accepted speakers will be asked to participate in a panel session (suggested but not required). They should be prepared to answer moderated attendee questions about their talk.

# New Competition: Ada/SPARK Crate of the Year Award

From: Fabien Chouteau <fabien.chouteau@gmail.com> Subject: New competition: Ada/SPARK Crate Of The Year Award Date: Mon, 28 Jun 2021 03:11:38 -0700 Newsgroups: comp.lang.ada

I am happy to announce AdaCore's new programming competition: The Ada/SPARK Crate Of The Year Award!

The announcement is here: https://blog.adacore.com/announcing-thefirst-ada-spark-crate-of-the-year-award

And you can register here: https://github.com/AdaCore/ Ada-SPARK-Crate-Of-The-Year

From: Marius Amado-Alves <amado.alves@gmail.com> Date: Wed, 30 Jun 2021 04:44:18 -0700

A candidate project must be on github? (fair enough)

Any Alire crate project must be on github?

#### Thanks.

From: Fabien Chouteau <fabien.chouteau@gmail.com> Date: Wed, 30 Jun 2021 05:47:49 -0700

For the Alire community index, your crate can either be in tarball format and hosted anywhere you want, or it can be a commit in a git repo in which case we ask you to host it on GitHub, SourceForge, GitLab or Bitbucket.

# Ada Semantic Interface Specification (ASIS)

# ASIS and libadalang

From: J-P. Rosen <rosen@adalog.fr> Subject: ASIS for Gnat (was: Any chance of programming a web frontend in Ada 2012?

Date: Wed, 9 Jun 2021 07:02:40 +0200 Newsgroups: comp.lang.ada > I did some progress in this direction, but ASIS4GNAT is abandoned and my project is suspended.

ASIS4GNAT is not abandoned, it is just not part of the CE edition. Pro users have access to it.

Please drop me a note if you have developed an ASIS tool, or are using an ASIS-based tool. With enough protests, we may convince AdaCore to make ASIS4GNAT available to the community.

From: Stephen Leake

<stephen\_leake@stephe-leake.org> Date: Fri, 11 Jun 2021 11:47:12 -0700

> ASIS4GNAT is not abandoned, it is just not part of the CE edition. Pro users have access to it.

On the other hand, if you are starting a new project, libadalang is a better choice.

*From: J-P. Rosen <rosen@adalog.fr> Date: Fri, 11 Jun 2021 22:31:25 +0200*

> On the other hand, if you are starting a new project, libadalang is a better choice.

What makes you think so?

By all means, compare the specifications of an ASIS package (Asis.Statements, Asis.Declarations) to Libadalang.Analysis and see which one is more usable...

From: Rod Kay <rodakay5@gmail.com> Date: Sat, 12 Jun 2021 20:47:29 +1000

> Please drop me a note if you have developed an ASIS tool [...]

I switched from ASIS to libadalang for an Ada IDE project also, since I thought ASIS was abandoned.

*From: J-P. Rosen* <*rosen*@*adalog.fr> Date: Sat, 12 Jun 2021 16:04:19* +0200

If you want to analyze code while it is being typed, as is common in an IDE, Libadalang is certainly the way to go.

If you want to make sophisticated analysis tools, it's another story. Hopefully, my paper at AE will soon be available...

#### From: Shark8

<onewingedshark@gmail.com>

Date: Mon, 14 Jun 2021 05:37:57 -0700

Oh, I am looking forward to reading it.

BTW, I really liked your "Memory Management in Ada 2012" video; I've used it as a reference several times to explain to Rust-people that Ada is safer than expected because pointers aren't required for a lot of things, and so you don't have to worry about null-exclusion.

From: Marius Amado-Alves <amado.alves@gmail.com> Date: Tue, 15 Jun 2021 14:40:41 -0700

Is JGNAT reliable, updated, available?

Thanks.

*From: J-P. Rosen* <*rosen*@*adalog.fr> Date: Wed, 16 Jun 2021 10:41:31* +0200

> Is JGNAT

>reliable,

I didn' try it enough to answer this

> updated,

No. The latest version is 2013. Another one of the useful stuff abandoned by AdaCore.

> available?

Yes, from Adacore's community download page.

# Ada and Education

# Exercism.io Needs Ada

From: Bruce Axtens

<br/>

<br/>

<br/>

<br/>

Subject: Exercism.io needs Ada<br/>

Date: Sat, 19 Jun 2021 13:30:37 +0800<br/>

Newsgroups: comp.lang.ada

In case anyone is looking to encourage people to learn and use Ada, Exercism.io is a good place to learn. Lots of languages already but Ada isn't one of them. Become a maintainer or a mentor.

Maintainer: https://exercism.io/ become-a-maintainer

Mentor: https://exercism.io/ become-a-mentor#more-info

Bruce Axtens, vbnet maintainer and students of about 26 languages none of which are, sadly, Ada.

From: Andreas Zeurcher <zuercher\_andreas@outlook.com> Date: Mon, 28 Jun 2021 13:42:03 -0700

Since you are a maintainer of another language (Visual Basic .Net), what is the precise sequence of steps that one would need to perform to become the 1st maintainer of a new presence of Ada in Exercism.io? I think that the 1st maintainer is specifically the person who bootstraps up a new language's presence on exercism.io, correct? Apparently, the sequence of steps might begin:

Practice being a newbie student of some arbitrary existing(-onexercism.io) language's exercises to get the feel for how exercism.io is supposed to operate.

#### then

2) Contact another language's maintainer to be the 1st maintainer of Ada's fresh presence on exercism.io.

Are there more steps than that? For example, must the 1st maintainer recruit a separate 1st mentor or must the 1st maintainer act also as 1st mentor? Are those 2 steps perfectly stated or are they botched somehow? Does some sort of vetting occur for the quality of a maintainer at time of volunteering that could cause the 1st maintainer to be rejected? Does some sort of vetting for the desirability of a programming language occur up at exercism.io "corporate" that could cause Ada itself (independent of the 1st maintainer) to be rejected? It seems that Ada and (AdaSubset-with-) SPARK would be 2 separate languages on exercism.io (otherwise it gets confusing), correct? Why doesn't exercism.io have an overt webpage that answers these questions for how to bootstrap up a language's new presence on exercism.io (as this seems to be a separate & distinct topic to becoming the 2nd-or-subsequent-mentor that does have its own webpage explanation already)?

From: Marius Amado-Alves <amado.alves@gmail.com> Date: Tue, 29 Jun 2021 06:06:56 -0700

Should not the first step be an evaluation of this site by a programming master? Maybe this has been done; if so, please inform.

# **Ada-related Resources**

[Delta counts are from Apr 26th to Jul 22th. —arm]

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Ada on Social Media Date: Wed, 22 Jul 2021 11:13:21 +0100 To: Ada User Journal readership

Ada groups on various social media:

- LinkedIn: 3\_161 (+42) members [1]

- Reddit: 7\_104 (+678<sup>1</sup>) members

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[8]

- Stack Overflow: 2\_087 (+39) questions

- Libera.Chat: 76 (new<sup>2</sup>) users

- Freenode: 15 (-79<sup>2</sup>) users

- Gitter: 86 (+11) people

- Telegram: 128 (+7) users

- Twitter: 75 (+32) tweeters

- 74 (=) unique tweets

<sup>1</sup> Probably caused in part by confusion with the ADA cryptocurrency.

<sup>2</sup> Freenode has suffered a mass exodus due to a change in ownership. Most channels have migrated to Libera.Chat.

- [1] https://www.linkedin.com/groups/ 114211/

- [2] http://www.reddit.com/r/ada/

- [3] http://stackoverflow.com/questions/ tagged/ada

- [4] https://netsplit.de/channels/details.php ?room=%23ada&net=Libera.Chat

- [5] https://netsplit.de/channels/details.php ?room=%23ada&net=freenode

- [6] https://gitter.im/ada-lang

- [7] https://t.me/ada\_lang

- [8] http://bit.ly/adalang-twitter

# **Repositories of Open Source Software**

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Repositories of Open Source software Date: Wed, 22 Jul 2021 11:13:21 +0100 To: Ada User Journal readership Rosetta Code: 827 (+16) examples [1] 38 (=) developers [2] GitHub:  $763^1$  (=) developers [3] Sourceforge: 275 (+2) projects [4] Open Hub: 214 (=) projects [5]

- Alire: 171 (+15) crates

- Bitbucket: 89 (=) repositories [7]

[6]

- Codelabs: 52 (=) repositories [8]

- AdaForge: 8 (=) repositories [9]

<sup>1</sup> This number is unreliable due to GitHub search limitations.

- http://rosettacode.org/wiki/ Category:Ada

- [2] http://rosettacode.org/wiki/ Category:Ada\_User

- [3] https://github.com/search? q=language%3AAda&type=Users

- [4] https://sourceforge.net/directory/ language:ada/

- [5] https://www.openhub.net/tags? names=ada

- [6] https://alire.ada.dev/crates.html

- [7] https://bitbucket.org/repo/all? name=ada&language=ada

- [8] https://git.codelabs.ch/? a=project\_index

- [9] http://forge.ada-ru.org/adaforge

# Language Popularity Rankings

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Ada in language popularity rankings

*Date: Wed, 22 Jul 2021 11:13:21 +0100 To: Ada User Journal readership*

[Positive ranking changes mean to go up in the ranking. The IEEE ranking deltas are in regard to the 2019 edition, as it is updated annually. —arm]

- TIOBE Index: 28 (+2) 0.48% (-0.01%) [1]

- PYPL Index: 18 (-1) 0.75% (-0.06%)

- IEEE Spectrum (general): 39 (+4) Score: 32.8 (+8.0) [3]

[2]

- IEEE Spectrum (embedded): 12 (+1) Score: 32.8 (+8.0) [3]

- [1] https://www.tiobe.com/tiobe-index/

- [2] http://pypl.github.io/PYPL.html

- [3] https://spectrum.ieee.org/static/ interactive-the-top-programminglanguages-2020

# **Ada Domain Names**

From: Heziode

<heziode@protonmail.com> Subject: Ada domain names: who holds what, and for which purpose? Date: Thu, 24 Jun 2021 20:03:39 +0200 Newsgroups: comp.lang.ada

By curiosity, I have checked if there is some domain name related to Ada language. I mean, domains that can be officially used to represent the language (even though according to Wikipedia, it is adaic.org. Keep in mind, I am doing this out of curiosity).

I was being surprised to discover that several domains, that could be used as an "official" website (like \*lang.org, \*lang.org, \*.codes, where "\*" is the language name), is bought but not used, and not in sales.

Here is a table of my few research:

Domain: Owner: Registered: Country: State

ada-lang.com : AdaCore : 2016/09/20 : FR\*

adalang.com: ?: 2014/03/30: US: Florida

ada-lang.org : ? : 2020/02/11 : US : WA

adalang.org : ? : 2020/02/12 : US : WA

ada.codes : Steve Arnold : 2014/04/23 : US : CA

\* Point on "thinkx.net", so DNS issue with wrong IP?

We can see that "ada-lang.org" and "adalang.org" seem to be bought by the same person/entity, but these domains are not used, and not in sales. Looks like domain retention.

Does anyone know who is behind these domains?

From: Luke A. Guest <laguest@archeia.com> Date: Thu, 24 Jun 2021 19:27:45 +0100

Steve is nerdboy on irc/github.

The Ada Lang one seems to be her name as there is a photo on the contact page.

There is learn/getadanow.com which is David Botton's.

# Ada-related Tools

# SweetAda 0.3 through 0.8

[Six consecutive announcements have been merged in a single thread. —arm]

From: Gabriele Galeotti <gabriele.galeotti.xyz@gmail.com> Subject: SweetAda 0.3 released Date: Tue, 6 Apr 2021 09:09:52 -0700 Newsgroups: comp.lang.ada

I've just released SweetAda 0.3.

SweetAda is a lightweight development framework to create Ada systems on a wide range of machines. Please refer to https://www.sweetada.org.

First of all, please re-download toolchain packages; although timestamps do not change, they contain updated versions of GCC/GNAT wrappers which are essentials for a properly working build system which should have reached a stabilization point, and it seems rather efficient and free from major issues.

Release notes

- due to changes in RTSes, switch -gnatp (pragma Suppress (All\_Checks)) is again commented out (Makefile.tc.in), to bring in exception processing; re-enable it if the final object is too big for your setup

- initial implementation of a secondary stack in the SFP RTS (not fully operational yet)

- strict compiler conformance, -gnatE and -gnato are defaults in Makefile.tc.in

- suppress No\_Elaboration\_Code in gnat.adc

- console.ali was not dragged in under GPRbuild mode and is missing in some configurations, which could lead to undefined references

- build.gpr/configure.gpr now correctly process implicit .ali units

- configure.ads (auto-generated from configuration.in) is pragma Pure

- a kernel link phase is performed if linker script changed

- Makefile now has two more targets: "session-start" and "session-end"; like "run" and "debug" targets, they are associated with shell commands that you can define in the platform configuration.in and can be useful for starting and ending JTAG servers, remote communication, and so on; these targets have nothing special, the names are only placeholders and their purposes are completely defined by the shell commands carried on; see an example in the new platform FRDM-KL46Z, where the commands respectively define an OpenOCD server startup and shutdown action

- Makefile.tc.in could specify -gsplitdwarf; thus you can find \*.dwo DWARF files in the object directory

- still more Makefiles tweaks: now there should be no problem building in GPRbuild mode; furthermore, "make createkernelcfg" forces a distclean

- menu-dialog.sh is standardized and behaves like menu.[bat|sh], so there are now separate items "createkernelcfg" and "configure" (previously there was a single "configure" item which executed them sequentially)

- elftool has a new command switch to find a symbol value: elftool -c findsymbol= which returns the symbol value; it is used, e.g., in the FRDM-KL46Z platform to automatically find the \_start address in the executable image and instruct OpenOCD to run the target with a properly resume address; see an example as outlined in .../platforms/FRDM-KL46Z/ runopenocd.tcl

- mbr can read other partitions beyond the first

- mbr partition read could cause a misaligned access with some CPUs, so an assignment is replaced with a memory copy

- Dreamcast code runs on a real device, not just in the GXemul emulator; this requires:

- a HIT-0400 "BroadBand Adapter" Ethernet module

- a CDI CD-ROM burned with "Dreamcast CDI Burner" https://alexfree.github.io/dcdib/

- a dc-tool-ip utility http://napalmx.thegypsy.com/adk/dc/dcloadip/index.html

(the dc-tool-ip utility will be soon replaced by a Tcl script)

- MicroBlaze has now udivsi3 and umodsi3 LibGCC assembler routines

- MemecFX12 and Spartan3E platforms now have Tcl scripts to build, download and execute SweetAda kernel

- new target: FRDM-KL46Z

Freescale/NXP ARM-CortexM0 board (a.k.a. "Freedom"), only able to blink a LED (needs OpenOCD to communicate with the target from inside SweetAda)

- FS-UAE platform renamed as Amiga-FS-UAE

- typos, cosmetics and minor adjustments

# Quick notes

As usual, download the three packages core, RTS and LibGGC (since many changes are system-wide), and please save your work before overwriting the filesystem.

### Subject: SweetAda 0.4 released Date: Tue, 27 Apr 2021 03:53:57 -0700

I've just released SweetAda 0.4. [...]

#### Release notes

- SweetAda has a new toolchain, armebsweetada-eabi, to handle big-endian ARMs (previously this was not necessary since ZFP does not link against libraries); affected target is DigiConnectME — and eventually your own experimental target; ARM BE targets now not need to specify bigendian switches anymore, but they should explicitly specify armebsweetada-eabi as the toolchain name in the platform configuration.in, i.e.: TOOLCHAIN\_NAME := \$(TOOLCHAIN\_NAME\_ARMeb) whilst ARM LE takes the default toolchain

- the non-optimized versions of divsi3/modsi3 for MicroBlaze were not selected; this is now corrected

- the download script for Dreamcast bba.tcl — is now written in Tcl (note: requires Tcl UDP extension) and thus does not require the dc-tool-ip utility, quick'n'dirty, no error checking yet; if it is difficult to install a Tcl extensions, then stuck yourself with dc-tool-ip by just uncommenting its exec line, and do an exit

- remove useless return statements in various Tcl scripts

- use Bits.BigEndian/LittleEndian booleans in llutils unit

- ATmega328P has more MCU definitions (not complete yet)

- ArduinoUno:

- XTAL clock frequency is specified in configure.ads

- ZFP profile is forced in configuration.in to avoid problems with a small footprint memory, thus overriding the settings in the top-level configuration.in

- BSP does nothing; tests moved in application/test-ArduinoUno

- FRDM-KL46Z has more definitions; ZFP profile is forced in configuration.in to avoid problems with a small footprint memory, thus overriding the settings in the top-level configuration.in

- bits.ads: some Bits\_XX\_Mask corrected; added Bits\_XX\_RMask

- now RTSes have, in every CPU target, two more files: 1) Makefile.srcs.in, the list of source files used (not of particular use so far, just a reference);

- 2) Makefile.rts.in, contains CPU-wide switches (i.e., not dependent on the multilib selected) used during the RTS build; those switches, which normally are empty, are automatically imported in the master Makefile and added to the target platform CPU, thus assuring that

the compiler agrees on both RTS code and SweetAda/user code; as a consequence of this, there is no more need to specify, e.g., "-fno-leadingunderscore" in SuperH/SH4 targets, and MIPS targets inherit automatically a -G0 switch (they are the only switches which are actually used in the RTS for those targets)

- QEMU-MIPS was based on "mips" machine; this machine does not exist anymore in current QEMU and so the platform is now based on "mipssim", what changes is just the UART16450 base I/O address in monitor.S

- Nios II Terasic DE10-Lite now has a Tcl front-end (programmer.tcl) which automatically downloads the SOF bitstream and executes the SweetAda code by means of Quartus commandline utilities and jtagd daemon

- Nios II Terasic DE10-Lite exposes a configuration setup that explains practically how to override core units, i.e., it invalidates last\_chance\_handler in the core directory and redefines the same subprogram package in its own directory, so to avoid dragging in the entire console package (which is used by the standard implementation of last\_chance\_handler)

- all Tcl scripts that handle the download of code on a physical target board are possibly renamed to a standardized "programmer.tcl"

- menu-dialog.sh now always shows warnings (previously it used to show warnings only if the build failed due to hard errors)

- typos, cosmetics and minor adjustments

Subject: SweetAda 0.5 released Date: Tue, 4 May 2021 04:09:43 -0700

### [...]

### Release notes

- The SFP RTS now gets Ada.Tags installed, and so it should be possible to use Ada tagged types

- there are no more multiple Makefile.rts.in scattered in every multilib directory, only a single file is stored in the RTS root path of the toolchain target

- Master Makefile does not export FPU\_MODEL, corrected

- new target: Synergy-S5D9 ARM-CortexM4 board, only able to blink a LED (needs OpenOCD to communicate with the target from inside SweetAda)

- LibGCC now has adddi3/subdi3/negdi2/mulsi3/muldi3 implemented in pure Ada (although a bit superfluous, since in most cases these subprograms will be overridden by CPU's own LibGCC assembly routines)

- The MVME162-510A platform has now a little Tcl script to download a SweetAda S-record image by means of 162-Bug on-board monitor communication; very simple script (and at 19200 also very slow for big images, but good enough for testing)

- the hard disk images for some platforms (Amiga-FS-UAE, Malta, PC-x86, etc) got accidentally deleted, they are now re-integrated for testing purposes

- removed superfluous conversion in Address\_Displacement

- drivers/PC: PIC\_Init has now Vector\_Offset\_Master/Slave input parameters and can be used also from non-x86 targets

- Malta MIPS: use PIC code from PC unit rather than an ad-hoc piece of code

- drivers/PC: PIT\_Counter0\_Init has an input Count parameter

- drivers/PC: unit does not depend on configure.ads anymore, and so the entire drivers branch should be CPUindependent

- typos, cosmetics and minor adjustments

Subject: ANN: SweetAda 0.6 released Date: Wed, 19 May 2021 09:56:18 -0700

[...]

# Release notes

- spurious entry

core/last\_chance\_directory was not removed in the configuration.in for the core complex, and this causes a build failure in GPRbuild mode, corrected

- Makefile.tc.in: new ADAC\_SWITCHES\_WARNING switches: -gnatw.q - (Activate warnings on questionable layout of record types) gnatw\_r - (Activate warnings for out-oforder record representation clauses) (unused)

- Makefile.tc.in: added DISABLE\_STACK\_USAGE flag (some targets do not support stack usage computation, can be set from platformlevel configuration.in)

- menu-dialog.sh remains in menu until you exit explicitly (e.g., by pressing double-ESC), so you can perform various actions sequentially; if instead you specify an action as an argument in the command line then the behaviour is unchanged, exiting at once after execution

- qemu-ifup.sh/qemu-ifdown.sh are now a single common copy in libutils directory; Dreamcast makeip.tcl/scramble.tcl are now merged in makecdrom.tcl; pc-x86-bootX.tcl moved as a single copy in share directory

- package Definitions is now placed in modules directory

- more error checking in various Tcl scripts

- initial cleanup of cpus branch file layout, removed duplicate files

- new target: SiFive HiFive1 Rev B, only able to blink the on-board RGB LEDs (needs OpenOCD to download the executable)

- Synergy-S5D9: bsp.ads got accidentally deleted, corrected

- Synergy-S5D9: added SCI definitions so that it can output something on SCI (UART mode, very primitive)

- partial rewriting of the NE2000 driver, more register definitions

- removed all ugly, unpleasant, illdesigned temporary code from exceptions.adb in PC-x86 interrupt handling (which now processes, e.g., raw TCP/IP traffic from applications.adb); the same in Amiga-FS-UAE

- some changes in Ethernet FIFO queue to make it more efficient

- ATmega328P (ArduinoUno): more register definitions, timers and general purpose registers; added some low-level templates; deleted unuseful subprogram in proprietary core unit and its dependency on console

- drivers/pc:

- revised 8254 PIT; PIT\_Counter0\_Init now uses MODE 2 (rate generator) instead of MODE 3 (square wave generator) as a system timer

- simple stub for RTC handling

- IrqX renamed to PIC\_IrqX

- Irq0 aliased to PIT\_Interrupt

- Irq8 aliased to RTC\_Interrupt

- added -mno-red-zone to GCC switches in x86-64

- use rounding instead of floor integer division when computing timing counts, where appropriate

There is also a new release of QEMU emulator — 20210517 — providing QEMU 6.0.0 for Linux and Windows platforms, and QEMU 5.2.0 for OS X. The OS X version should work on El Capitan (tested on a VM, someone reported problems on later versions).

Subject: ANN: SweetAda 0.7 released Date: Tue, 1 Jun 2021 13:18:02 -0700

[...]

#### Release notes

- updated targets in master Makefile ("all" was tagged default instead of "help"); the targets "kernel\_info" and "kernel\_libinfo" are now exposed (kernel\_libinfo produces listings of library objects even if the kernel build is not successful)

- added implicit dependencies for console unit

- elftool will emit spaces instead of TABs when performing an ELF section dump, this will be noted in the next toolchain release

- the linker script filename can now be declared in the platform configuration.in by specifying "LD\_SCRIPT:= <linker\_script\_filename>", otherwise it takes a default "linker.lds"

- the C library now implements Ada stubs for malloc/free/calloc/realloc, so C code can call these Ada subprograms via stdlib wrappers; this has also the benefit of resolve references to malloc() when secondary stack tries to return heavy (i.e., unconstrained) objects, but be sure to add "USE\_LIBGCC := Y" and "USE\_CLIBRARY := Y" to the configuration.in file, either the generic one in the top-level directory, or the platform-dependent one

- SFP RTS: a-except: Raise\_Exception calls Last\_Chance\_Handler

- SFP RTS: added Ada.Assertions (for pragma Assert you need to turn on gnata in the "Ada Run-Time Checks switches" section of Makefile.tc.in)

- core/bits: added BITZERO/BITONE/BITL/BITH/BITO FF/BITON declarations

- core/console: Print (Boolean), emits "T" or "F"

- core/llutils: HexDigit\_To\_U8 uses a case instead of longer ifs

- modules/definitions: added a few definitions

- added various Volatile\_Full\_Access aspects here and there

- corrected some section wildcards in linker scripts for ARM platforms

- x86\_64 lacks some low-level CPU subprograms (but they are empty anyway) and so the build could fail with unresolved objects, added

- new libutils/libopenocd.tcl file, useful for small OpenOCD function helpers

- Digi Connect ME (NET+ARM NS7520): some more register definitions; adopted a Tcl script as frontend to OpenOCD

- Synergy S5D9: OpenOCD cfg file renamed to standard "openocd.cfg"

- Synergy S5D9: more register definitions, SCI almost completely parameterized

- platform Spartan3E renamed as Spartan3E-SK

- new target: Avnet Xilinx Spartan-3A Evaluation Kit (Spartan3A-EK, MicroBlaze v7.00.b), only able to blink a LED; the programmer.tcl front-end will download the bitstream by directly interfacing with the on-board Cypress

PSoC via USB protocol (no external tools needed in a Linux environment)

- targets involving OpenOCD (DigiConnectME, FRDM-KL46Z, HiFive1, MSP432P401R, STM32F769I, Synergy-S5D9) now should specify in the platform configuration.in the OpenOCD prefix (in Windows is the installation directory, i.e., that which is the parent of bin/, etc); the default is the \*nix path "/usr/local"

- in the top-level directory there are the two files .cproject and .project for Eclipse CDT; no big deal since you have absolutely no Ada support, but if you import the project and configure the \*.adb and \*.ads files as textual source files, you could do a make build cycle, with error signalling (clicking on the error shown in console should redirect you to the offending source line)

- typos, cosmetics and minor adjustments

Subject: ANN: SweetAda 0.8 released Date: Mon, 14 Jun 2021 07:46:15 -0700

[...]

Release notes @ https://www.sweetada.org/ release\_notes.html.

Downloads available @ https://sourceforge.net/projects/sweetada.

#### Release notes

- ADA\_MODE defaults to ADA20 (-gnat2020)

- now the RTS is not a single common archive, instead every target CPU has its own — i.e. you have to download sweetada-rts-<target>-0.8.tar.gz; this way you avoid to waste bandwidth downloading a large RTS for, e.g., the AVR, when you don't need it

- adjusted Lock\_Type definitions according to Ada 2020

- Tcl scripts: use "eq"/"ne" in place of "=="/"!="

- corrected a misinterpretation in the libopenocd.tcl proc version\_numeric

- various programmer.tcl front-ends do not inherited OPENOCD\_PREFIX, corrected

- change "adapter\_khz" to "adapter speed" in OpenOCD configurations

- NiosII RTS has -mgpopt=none switch, so it is inherited in those kind of platforms

- NiosII lacks interrupt subprograms declaration (body still TBD), declared

- adjusted linker scripts in NiosII platforms (Altera10M50GHRD, DE10-Lite)

- DigiConnectME has ARM vectors template in llkernel.s

- adjusted some values in VGA low-level register programming; the package now

can setup graphic mode 12h (640x480x16)

- burned in an EPROM, SweetAda correctly startups in a DECstation 5000/133 and output messages on the SCC8530 serial port, blinking also the rear LEDs

- added/removed some

Volatile\_Full\_Access aspects and

cleaned up record layouts that don't need

it (they are placed in the object

definition instead)

- every CPUs has eventually an empty LibGCC package spec (which overrides thecore one); this enforces a catch of package (mis-)using, which cause the compiler to flag an error (should you try to use it when the CPU really does not need it)

- corrected a Makefile target dependency (output listings could be out-of-synch if "make postbuild" is not explicitly called)

- typos, cosmetics and minor adjustments

#### Quick notes

As usual, download the three packages core, RTS and LibGCC (since many changes are system-wide), and please save your work before overwriting the filesystem.

# **GNAT LLVM, ACATS**

From: Simon Wright <simon@pushface.org> Subject: GNAT LLVM, ACATS Date: Wed, 07 Apr 2021 11:58:11 +0100 Newsgroups: comp.lang.ada

I recently had success building GNAT\_LLVM on macOS: see notes here [1].

Running ACATS 4.1 U via the ACATS Grading tools as patched for llvm-gnat [2], I get impressively successful results: out of 4092 tests, GCC 11.0.1 of 2021-03-31 has

Result: Overall, B-Tests, C-Tests, L-Tests, Other Tests

[...]

Total Failed: 44, 30, 14, 0, 0

Total Not-Applicable: 35, 0, 35, 0, 0

Total Special: 182, 141, 21, 10, 10

Total Passed: 3831, 1272, 2420, 61, 78

(L-tests "check that all library unit dependencies within a program are satisfied before the program can be bound and executed, that circularity among units is detected, or that pragmas that apply to an entire partition are correctly processed". 'Special' means human inspection needed.)

whereas llvm-gnat, built from the same GCC sources, has

Result: Overall, B-Tests, C-Tests, L-Tests, Other Tests

[...]

Total Failed: 48, 31, 17, 0, 0

Total Not-Applicable: 35, 0, 35, 0, 0

Total Special: 184, 141, 23, 10, 10

- Total Passed: 3825, 1271, 2415, 61, 78 [1] https://github.com/AdaCore/gnatllvm/ issues/20#issuecomment-809400426

- [2] https://github.com/simonjwright/ ACATS-grading/tree/llvm

# HAC V.0.095

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Subject: Ann: HAC v.0.095 Date: Wed, 7 Apr 2021 12:23:53 -0700 Newsgroups: comp.lang.ada

HAC (HAC Ada Compiler) is a small, quick, open-source Ada compiler, covering a subset of the Ada language. HAC is itself fully programmed in Ada.

Web site: http://hacadacompiler.sf.net/

Source repositories:

#1 svn: https://sf.net/p/hacadacompiler/ code/HEAD/tree/trunk/

#2 git: https://github.com/zertovitch/hac

\* Improvements since v.0.085:

Modularity: HAC recursively compiles all units needed to build a main program. Currently only procedures and functions bodies are supported - no packages yet, no separate specifications.

An example can be found in exm/unit\_a.adb

#### Enjoy!

*From: Stéphane Rivière <stef@genesix.fr> Date: Thu, 8 Apr 2021 10:26:00 +0200*

Well done Gautier!

In our company, we now use HAC here to replace many big Bash scripts in our servers cluster spread in 3 european DC. Big gain of productivity and maintainability.

Incidentally, HAC is up to 7 times faster than Bash for a much lower resource consumption. Surprising when you see the poverty of the syntax and semantics of Bash.

# UXStrings 20210405

From: Blady <p.p11@orange.fr> Subject: [ANN] UXStrings package available (UXS\_20210405). Date: Sun, 11 Apr 2021 10:45:53 +0200 Newsgroups: comp.lang.ada

A second POC implementation for UXStrings is provided. The source code

files end with the number 2 as for instance "uxstrings2.ads". https://github.com/Blady-Com/ UXStrings/blob/master/src/uxstrings2.ads

A GNAT project file "uxstrings2.gpr" is provided with some naming conventions for both packages UXString and UXStrings.Text\_IO.

Some API have been added to support ASCII 7 bits encoding for both version UXStrings 1 and 2. ASCII is a subset of UTF-8 thus no change with the internal UTF-8 representation.

However, in addition to UXStrings 1 implementation, the API is now aware if content is full ASCII. On one hand, this permits to access directly to the position of one character without iterating on UTF-8 characters. Thus this is a time improvement when content is full ASCII. On the other hand, when content is changing the API checks if the new content is full ASCII. Thus this is a time penalty when changes are not full ASCII.

English contents as programming text files are composed of lines in majority full ASCII but they may have some lines with characters out of the ASCII set. UXStrings is dealing with both.

Available on GitHub (https://github.com/Blady-Com/ UXStrings) and also on Alire (https://alire.ada.dev/crates/ uxstrings.html).

Feedback is welcome on the actual time improvement on your real use cases.

# **RAPID** New Maintainer

From: Thomas <fantome.forums.tdecontes@ free.fr.invalid> Subject: RAPID Date: Mon, 12 Apr 2021 18:56:52 +0200 Newsgroups: comp.lang.ada

Hi :-)

courtesy Oliver Kellogg, I'm officially the new RAPID maintainer :-)

I would like to know if there still exist some RAPID users :-)

I also would like to know if there are some users of other platforms than Unix or Windows who would like to use RAPID, even if it doesn't work until now.

I see that GtkAda supports at least Solaris/SPARC platform, in addition to Unix and Windows, but if no one is interested I won't waste time on a specific portability. Tell me :-)

#### **RAPID** maintainer

http://savannah.nongnu.org/projects/rapid/

From: Shark8 <onewingedshark@gmail.com> Date: Mon, 12 Apr 2021 10:58:22 -0700 I'm on Windows and Solaris and Linux here, we might get Macintosh from longterm visitors.

From: Thomas

<fantome.forums.tdecontes@ free.fr.invalid> Date: Mon, 12 Apr 2021 20:04:51 +0200

ok :-)

What's your relation with RAPID? (Are you a user? Are you interested? ...)

From: Shark8

<onewingedshark@gmail.com>

Date: Mon, 12 Apr 2021 13:01:00 -0700

Not a user, currently.

But interested, and having a nice crossplatform common-UI would make things a lot nicer for some prospective softwareupgrades at work.

One such possible nicety would be a universal administration tool, another would be a data-management/-analysis tool for visiting scientists, another possibility would be decoupling several control-programs (codebases in everything from C to VB to C#) used to operate the instrumentation here from their host-systems and increase portability.

# SparForte 2.4.1

From: Ken Burtch <koburtch@gmail.com> Subject: ANN: SparForte 2.4.1 Released Date: Sat, 1 May 2021 05:13:35 -0700 Newsgroups: comp.lang.ada

SparForte 2.4.1 has been released. This mainly contains fixes for the new tab completion system.

SparForte is my Ada-based shell, scripting language and web template engine.

SparForte can be downloaded at https://www.sparforte.com

The change log is located at https://www.sparforte.com/news/2021/ news\_may2021.html

SparForte is a hobby and relies on contributions from volunteers.

# Simple Components v4.56

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Subject: ANN: Simple Components v4.56 Date: Sun, 2 May 2021 14:55:01 +0200 Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, streams, multiple connections server/client designing tools and protocols implementations. The library is kept conform to the Ada 95, Ada 2005, Ada 2012 language standards.

http://www.dmitry-kazakov.de/ada/ components.htm

Changes to the version 4.55:

- The packages Persistent.Streams and Persistent.Streams.Dump were added to implement streams backed by a fail-safe file;

- ELV/e-Q3 MAX! cube client was changed to work around cube firmware problems.

# GCC 11.1.0 for MacOS

From: Simon Wright <simon@pushface.org> Subject: ANN: GCC 11.1.0 for macOS Date: Sun, 02 May 2021 17:28:09 +0100 Newsgroups: comp.lang.ada

GCC 11.1.0 x86\_64-apple-darwin for macOS is available at: https://sourceforge.net/projects/gnuada/ files/GNAT\_GCC%20Mac%20OS%20X/ 11.1.0/native

The release no longer supports ASIS.

Libadalang and tools (gnatmetric, gnatpp, gnatstub, gnattest) are included.

Please note:

- \* This release is made as an installer package. Because I don't have a signing ID, you can't double-click on it; instead, right-button, Open, and ignore the warnings. Sorry.

- \* In the past, I've included modified versions of the compiler specs files. This time, such a modified specs file wouldn't run on El Capitan, so I've supplied the compiler as-built; if you're on Mojave or later, you need to set SDKROOT to pick up the place where Apple provides them. This means that the compiler won't automatically look in /usr/local/include (affects C, C++) or /usr/local/lib (affects all languages).

See the release notes at Sourceforge.

From: Simon Wright <simon@pushface.org> Date: Thu, 10 Jun 2021 17:21:57 +0100

This release contains versions of gnatstub, gnattest, gnatpp and gnatmetric which fail to load:

\$ /opt/gcc-11.1.0/bin/gnattest —help

dyld: Library not loaded: @rpath/libgnarl-11.dylib

Referenced from: /opt/gcc-11.1.0/bin/gnattest Reason: image not found

Abort trap: 6

Workaround: export DYLD\_FALLBACK\_LIBRARY\_PATH =/opt/gcc-11.1.0/lib/gcc/ x86\_64-apple-darwin15/11.1.0/adalib

You may not be aware that gprbuild now lets you specify building standalone static libraries "for Library\_Interface use (listof-units);"

- this doesn't work on macOS, and in fact cannot work, because it uses features of binutils object binaries that aren't available in Mach-O. The effect of this is that a static link against such a library will fail if the library involves any tasking. If you try to fix this by using the relocatable version, and then move the executable, it won't find the GNAT runtime dylibs.

I wonder why the GNAT runtime dylibs are all the way down there without a symlink in \$prefix/lib?

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Sun, 2 May 2021 18:54:25 +0200

Thanks Simon!

As a side note. The version 11 brings new incompatibilities breaking old code. In some cases X'Access is no longer accepted and needs to be replaced by X'Unchecked\_Access.

I am too lazy to analyze whether that is a bug or feature, just be aware.

I dare say that every Ada style guideline should require 'Unchecked\_Access everywhere. The issue became a permanent maintenance nightmare.

From: J-P. Rosen <rosen@adalog.fr> Date: Mon, 3 May 2021 10:29:38 +0200

> The release no longer supports ASIS.

That's unfortunate. Actually, GNAT FSF could be a good opportunity to continue support for ASIS.

> Libadalang and tools (gnatmetric, gnatpp, gnatstub, gnattest) are included.

But I guess not gnatcheck, since it needs ASIS.

From: Simon Wright <simon@pushface.org>

Date: Mon, 03 May 2021 12:14:11 +0100

> But I guess not gnatcheck, since it needs ASIS.

gnatcheck isn't in any of the recent releases of CE. [1], see the [Tools] section at the end, says it's not.

The [Tools] section also says ASIS is available as an add-on. But it says that about GNATtest.

[1] https://www.adacore.com/gnatpro/ comparison From: Luke A. Guest <laguest@archeia.com> Date: Mon, 3 May 2021 11:46:51 +0100

> That's unfortunate. Actually, GNAT FSF could be a good opportunity to continue support for ASIS.

Why? ASIS is dead, even the WG don't bother anymore.

From: J-P. Rosen <rosen@adalog.fr> Date: Mon, 3 May 2021 13:50:38 +0200

> Why? ASIS is dead, even the WG don't bother anymore.

Many tools depend on ASIS, and there might well be an update of the standard. It is still supported by GnatPro (and PTC).

From: Bill Findlay

<findlaybill@blueyonder.co.uk> Date: Mon, 03 May 2021 16:16:50 +0100

> GCC 11.1.0 x86\_64-apple-darwin for macOS is available at:

Thanks for that Simon.

My KDF9 emulator (~25KSLOC of Ada 2012) compiles and runs correctly, but the (stripped) object code is about 10% bigger and runs about 10% slower than a version compiled with GNAT CE 2020.

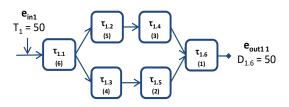

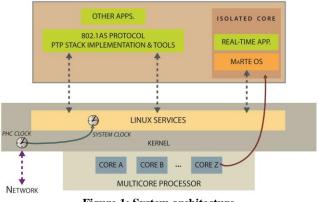

Is an Apple Silicon compiler a reasonable thing to hope for in the not too distant future? (Hint 8-)