### The journal for the international Ada community

# Ada User Journal

Volume 43 Number 2 June 2022

| 80  | Editorial                                                                                                                                         |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 81  | Quarterly News Digest                                                                                                                             |

| 82  | Conference Calendar                                                                                                                               |

| 10  | Forthcoming Events                                                                                                                                |

|     |                                                                                                                                                   |

|     | Articles from AEiC 2022 Work-in-Progress Session                                                                                                  |

| 11  | S.T. Taft, S. Baird, C. Dross<br>Defining a Pattern Matching Language Feature for Ada                                                             |

| 11  | S.T. Taft<br>A Work Stealing Scheduler for Ada 2022, in Ada                                                                                       |

| 11: | J. Zou, X. Dai, J.A. McDermid<br>Resilience-Aware Mixed-Criticality DAG Scheduling<br>on Multi-cores for Autonomous Systems                       |

| 11: | I. Sousa, A. Casimiro, J. Cecilio<br>Artificial Neural Networks<br>for Real-Time Data Quality Assurance                                           |

| 12  | J. Loureiro, J. Cecilio<br>Deep Learning for Reliable Communication Optimization<br>on Autonomous Vehicles                                        |

| 12  | M. Solé, L. Kosmidis<br>Compiler Support for an AI-Oriented SIMD Extension<br>of a Space Processor                                                |

| 129 | A. Jover-Álvarez, I. Rodríguez, L. Kosmidis, D. Steenari<br>Space Compression Algorithms Acceleration<br>on Embedded Multi-core and GPU Platforms |

| 13  | Z. Boukili, H.N. Tran, A. Plantec<br>Fine-Grained Runtime Monitoring<br>of Real-Time Embedded Systems                                             |

|     |                                                                                                                                                   |

### **Produced by Ada-Europe**

#### **Editor in Chief**

António Casimiro

University of Lisbon, Portugal AUJ Editor@Ada-Europe.org

#### Ada User Journal Editorial Board

| <b>Luís Miguel Pinho</b>                  | Polytechnic Institute of Porto, Portugal                                     |

|-------------------------------------------|------------------------------------------------------------------------------|

| Associate Editor                          | lmp@isep.ipp.pt                                                              |

| <b>Jorge Real</b><br>Deputy Editor        | Universitat Politècnica de València, Spain <i>jorge@disca.upv.es</i>         |

| <b>Patricia López Martínez</b>            | Universidad de Cantabria, Spain                                              |

| Assistant Editor                          | lopezpa@unican.es                                                            |

| Kristoffer N. Gregertsen                  | SINTEF, Norway                                                               |

| Assistant Editor                          | kristoffer.gregertsen@sintef.no                                              |

| <b>Dirk Craeynest</b>                     | KU Leuven, Belgium                                                           |

| <i>Events Editor</i>                      | Dirk.Craeynest@cs.kuleuven.be                                                |

| <b>Alejandro R. Mosteo</b><br>News Editor | Centro Universitario de la Defensa, Zaragoza, Spain <i>amosteo@unizar.es</i> |

#### **Ada-Europe Board**

| <b>Tullio Vardanega</b> (President)<br>University of Padua                    | Italy          |  |

|-------------------------------------------------------------------------------|----------------|--|

| <b>Dirk Craeynest</b> (Vice-President)<br>Ada-Belgium & KU Leuven             | Belgium        |  |

| <b>Dene Brown</b> (General Secretary)<br>SysAda Limited                       | United Kingdom |  |

| Ahlan Marriott (Treasurer)<br>White Elephant GmbH                             | Switzerland    |  |

| <b>Luís Miguel Pinho</b> (Ada User Journal)<br>Polytechnic Institute of Porto | Portugal       |  |

| António Casimiro (Ada User Journal)<br>University of Lisbon                   | Portugal       |  |

#### **Ada-Europe General Secretary**

Dene Brown SysAda Limited Signal Business Center 2 Innotec Drive BT19 7PD Bangor Northern Ireland, UK Tel: +44 2891 520 560 Email: Secretary@Ada-Europe.org URL: www.ada-europe.org

#### Information on Subscriptions and Advertisements

Ada User Journal (ISSN 1381-6551) is published in one volume of four issues. The Journal is provided free of charge to members of Ada-Europe. Library subscription details can be obtained direct from the Ada-Europe General Secretary (contact details above). Claims for missing issues will be honoured free of charge, if made within three months of the publication date for the issues. Mail order, subscription information and enquiries to the Ada-Europe General Secretary.

For details of advertisement rates please contact the Ada-Europe General Secretary (contact details above).

## ADA USER JOURNAL

### Volume 43 Number 2 June 2022

### Contents

|                                                                                                                                                 | Page       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Editorial Policy for Ada User Journal                                                                                                           | 80         |

| Editorial                                                                                                                                       | 81         |

| Quarterly News Digest                                                                                                                           | 82         |

| Conference Calendar                                                                                                                             | 103        |

| Forthcoming Events                                                                                                                              | 108        |

| Articles from the AEiC 2022 Work-in-Progress Session                                                                                            |            |

| S. T. Taft, S. Baird, C. Dross<br>"Defining a Pattern Matching Language Feature for Ada"                                                        | 111        |

| S. T. Taft<br>"A Work Stealing Scheduler for Ada 2022, in Ada"                                                                                  | 112        |

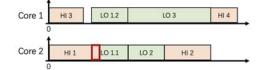

| J. Zou, X. Dai, J. A. McDermid<br>"Resilience-Aware Mixed-Criticality DAG Scheduling on Multi-cores for Autonomous Syste                        | ems" 113   |

| I. Sousa, A. Casimiro, J. Cecílio<br>"Artificial Neural Networks for Real-Time Data Quality Assurance"                                          | 117        |

| J. Loureiro, J. Cecílio<br>"Deep Learning for Reliable Communication Optimization on Autonomous Vehicles"                                       | 121        |

| M. Solé, L. Kosmidis<br>"Compiler Support for an AI-oriented SIMD Extension of a Space Processor"                                               | 125        |

| A. Jover-Alvarez, I. Rodriguez, L. Kosmidis, D. Steenari<br>"Space Compression Algorithms Acceleration on Embedded Multi-core and GPU Platforms | s" 129     |

| Z. Boukili, H. N. Tran, A. Plantec<br>"Fine-Grained Runtime Monitoring of Real-Time Embedded Systems"                                           | 133        |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                       | 134        |

| Ada-Europe Sponsors Inside B                                                                                                                    | Back Cover |

|                                                                                                                                                 |            |

### Editorial Policy for Ada User Journal

#### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

#### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

#### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

#### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

#### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

#### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

### Editorial

I would like to start this editorial by celebrating the fact that the Ada-Europe International Conference on Reliable Software Technologies (AEiC-2022) is taking place once again as a physical event, this time in Ghent, Belgium, on June 14-17. The conference features an excellent and diversified technical program, also including a rich set of opportunities for socializing, namely by participating in very interesting cultural and social events.

Coincidentally, but not surprisingly, in this issue of the Ada User Journal we start the publication of the AEiC-2022 Work-in-Progress Session proceedings. We include eight contributions, covering a set of quite diverse topics related to the development of reliable embedded systems, or to the Ada language.

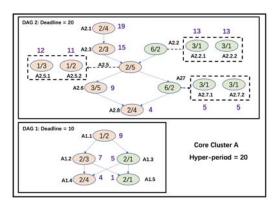

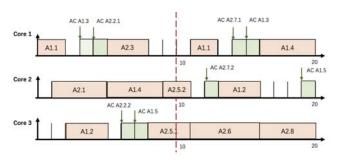

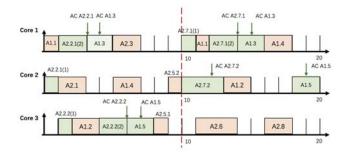

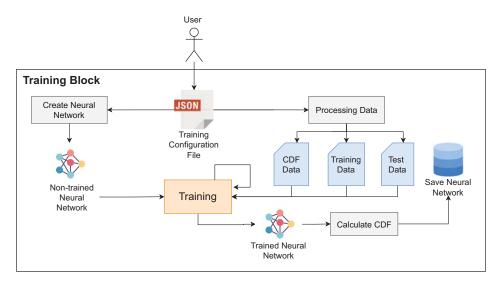

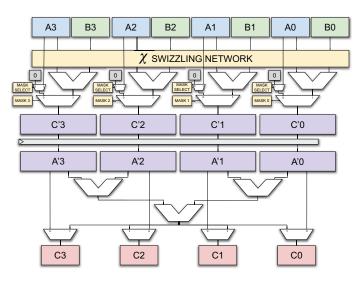

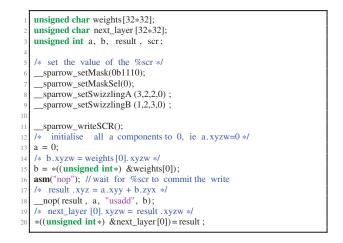

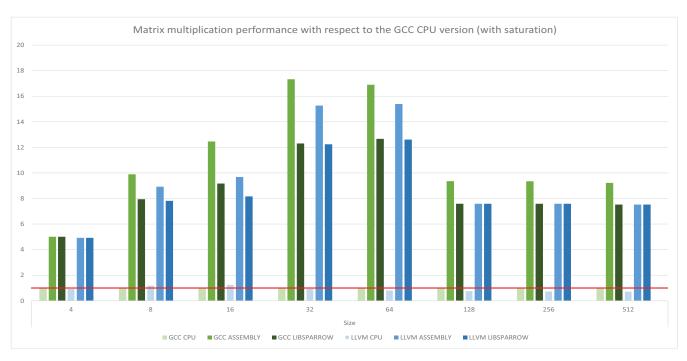

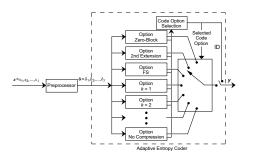

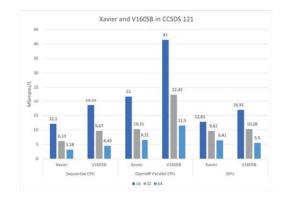

The first two papers address Ada-related features and are both written by authors from AdaCore (USA and France). They report on work in progress concerning the definition of a pattern-matching feature for Ada, and the definition of a work-stealing scheduler for the lightweight threads supporting the Ada 2022 parallel programming features. Then, a paper describing a new scheduling method for mixed-criticality systems is presented. The work, by authors from the University of York, UK, is developed for multi-core systems and considers the survivability of low criticality tasks, to achieve consistent schedules for different operation modes. After that, two papers by authors from the Faculty of Sciences of the University of Lisbon are included. In both cases, machine learning techniques are used for improving aspects of embedded systems operation, either the quality of sensor data or the communication reliability. The following paper is authored by Marc Solé and Leonidas Kosmidis, who are affiliated with the Barcelona Supercomputing Center (BSC) and the Polytechnic University of Catalonia (UPC). They report on their experience using the GCC and LLVM compilers, which were extended with the necessary support for the SPARROW hardware, an AI-oriented SIMD Extension. Then we include another paper authored by BSC/UPC researchers, but in this case co-authored by David Steenari, from the European Space Agency. The paper presents ongoing work concerning the acceleration of data compression, considering two different embedded GPU platforms for space systems for evaluation purposes. It is shown that despite the typically sequential nature of data compression tasks, it is possible to achieve performance improvements through parallelization. Finally, this first part of the AEiC-2022 WiP proceedings is closed with a paper authored by Zineb Boukili, Hai Nam Tran and Alain Plantec, from the University of Brest. The paper presents a new approach for runtime timing monitoring of real-time systems, which is based on the definition of fine-grained program blocks and on code instrumentation on defined monitoring points.

In this AUJ issue we also include, as usual, the News Digest section prepared by Alejandro R. Mosteo, and the Calendar and Events sections, prepared by Dirk Craeynest.

Antonio Casimiro Lisboa June 2022 Email: AUJ\_Editor@Ada-Europe.org

### Quarterly News Digest

#### Alejandro R. Mosteo

Centro Universitario de la Defensa de Zaragoza, 50090, Zaragoza, Spain; Instituto de Investigación en Ingeniería de Aragón, Mariano Esquillor s/n, 50018, Zaragoza, Spain; email: amosteo@unizar.es

#### Contents

| Preface by the News Editor<br>Ada-related Events<br>Ada-related Resources<br>Ada-related Tools<br>Ada and Operating Systems<br>Ada Inside<br>Ada and Other Languages | 82<br>82<br>86<br>87<br>89<br>90<br>90 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Ada Practice                                                                                                                                                         | 90<br>94                               |

|                                                                                                                                                                      |                                        |

[Messages without subject/newsgroups are replies from the same thread. Messages may have been edited for minor proofreading fixes. Quotations are trimmed where deemed too broad. Sender's signatures are omitted as a general rule. —arm]

### Preface by the News Editor

#### Dear Reader,

It is a recurrent topic that the several GNAT versions with differing licensing conditions are [not] a hindrance to Ada adoption. Well, AdaCore has announced that, moving forward, their open source oriented compiler offering will be unique and based on the FSF source tree, hence with similar licensing as other GCC languages [1]. Let us hope this puts to rest the FUD of the past. No doubt, a remarkable piece of news and a valiant bet on the future of Ada with the backing of a healthy open source community.

Likewise on the open source front, the HAC compiler continues making steady progress [2], with several versions released in close succession, each one bringing more Ada features into its supported subset.

This issue has seen a livelier than usual section on Ada and other languages. I always find interesting the examination of the interrelations between languages, and how Ada fits in the past, present and future of programming languages. Will Ada ever regain a spot in the top-10 more popular languages [3]? Perhaps we should devise our own ranking using Metrics that Really Matter<sup>TM</sup>;-)

Sincerely, Alejandro R. Mosteo.

- [1] "A New Era for Ada/SPARK Open Source Community", in Ada-related Tools.

- [2] "HAC v.0.2", in Ada-related Tools.

- [3] "When Ada Was the Most Popular Language", in Ada and Other Languages.

#### Ada-related Events

#### Ada Monthly Meeting Proposal

From: Fernando Oleo Blanco <irvise\_ml@irvise.xyz> Subject: Ada Monthly Meeting proposal Date: Tue, 26 Apr 2022 21:59:32 +0200 Newsgroups: comp.lang.ada

#### Ada Monthly meeting

A lot of programming languages and libraries have meetings/meetups which allow the community to come together and have a chat, share ideas, proposals and better utilise and prioritise resources. I would like to propose such a thing for Ada. Below is the rationale and some ideas and issues.

#### Motivation

The Ada community does not have many members when compared to other morewell-known communities. However, there is still some interest in having such type of meetings. This was recently made clear after some people pointed out they would like to have such a thing in the Ada channel over at Gitter. Personally, I have been playing with such an idea and that is what motivated me to volunteer to drive the FOSDEM Ada devroom. I would like the Ada community to be more wellknown and to have the same "resources" as other communities have. Meetups are a great way to have fun while discussing what we like.

In meetups, generally speaking, users and developers can have the opportunity to come together, discuss topics, organise resources and help each other. Graybeards can help those who still have colour in their hair; people with different sets of skills can propose solutions to problems that one may not have thought about; authors can present their work or improvements, etc. I would like to use the Fortran community as an example of what meetups can be used for. Here is their April monthlymeetup [1]. Their meetups are very focused on the language and "core" tooling... it is quite formal, which may not be what I had in mind, but we will see.

#### Who is this meant for?

Everybody who is interested.

I would love to see some participation of the "Industrial users". But I understand that a lot of people see Ada (and many other things) as a tool that brings food to the table, nothing more. So I would not expect much participation from this group.

Newbees and beginners are also more than welcome. They could see what people are doing and ask questions that are better answered in real-time by a person, instead of a Stackoverflow for example.

Though, I must be honest, it is mostly intended for people who are interested in the Ada environment and open side of things. This is due to the nature of an open discussion and building a community. I have to be clear and state that I am biased towards the libre community, so feel free to point out any unfairness.

#### How would it work? What would it be like?

#### THIS IS JUST A PROPOSAL, SO TAKE THIS AS SUCH.

I thought about having a Jitsi room (libre conference system that runs on your browser, same one used in FOSDEM) [2] where people can just join and take part of the meetup. Jitsi allows for moderation too, so that speakers can talk without getting interrupted and it has a built in chat too.

So, what could be discussed? Here is a short list of ideas that I have:

- Monthly news: new releases, milestones, etc.

- Presentations: attendees may want to present their work or do a demonstration. They may also want to have a discussion about a specific topic (for example, the use of Ada 2022 features).

- General libre software coordination: improvements to tools, feedback, questions, past goals discussion, etc.

- General Q&A related to Ada and open to everybody.

- Finally, a beer.

I think this could take place between 30 min to 2 hours, depending on the load of that day. Presentations would obviously be much more casual and easy when compared to an actual conference.

#### Potential issues

1. Not enough interest.

2. Timezones! Users are mostly concentrated in Asia-Pacific/EU/USA, which makes coordination an absolute pain. A compromise could be found, or a different schedule each month in such a way that everybody benefits (and gets screwed) equally.

3. Organisation: there needs to be a main organiser and a second in command-

4. There also needs to be a medium in which to spread the word. C.L.A is a good starting point, but may not reach the wider community. It could be announced everywhere every month, but that is a tedious task.

#### Feedback

I have probably said enough, even if not everything has been said. So I would like to ask for your feedback and specially know if you would be interested.

Thank you for your time, Fer

#### References

[1] https://invidious-us.kavin.rocks/ watch?v=8-\_ll4f0gN8

[2] https://meet.jit.si/

From: Maxim Reznik

<reznikmm@gmail.com> Date: Wed, 27 Apr 2022 03:34:13 -0700

I would give it a try!

From: Anton F. <imantonmeep@gmail.com> Date: Wed, 27 Apr 2022 05:57:49 -0700

I would participate, this is a great idea!

From: Yossep Binyoum <yossep237@gmail.com> Date: Thu, 28 Apr 2022 13:41:03 -0700

From Senegal, I totally agree with you. I give it a try

From: Stéphane Rivière <stef@genesix.org> Date: Fri, 29 Apr 2022 16:38:39 +0200

#### Great idea!

From: Stephen Leake <stephen\_leake@stephe-leake.org> Date: Fri, 29 Apr 2022 11:29:47 -0700 > \* Ada Monthly meeting

Sounds interesting. I maintain Emacs Ada mode; this might be a good forum to get less formal feedback than the ada-mode mailing list provides, and to hear what other IDEs are doing for Ada.

> 1. There also needs to be a medium in which to spread the word. C.L.A is a good starting point, but may not reach the wider community. It could be announced everywhere every month, but that is a tedious task.

This sounds like a job for a bot; post the same announcement to a list of channels.

#### Anyone have a bot written in Ada?

From: Maxim Reznik <reznikmm@gmail.com> Date: Fri, 29 Apr 2022 21:04:15 -0700

> Anyone have a bot written in Ada?

I have a bot in Ada for Telegram. It is a bridge between Telegram, Jabber, IRC channel. It also checks whether telegram newcomers are not bots.

I can write another one for announcements, but I'm not sure if announcing once a month is worth the time :)

#### From: Ada Forge <adaforge2022@gmail.com> Date: Sat, 30 Apr 2022 06:57:40 -0700

> \* Ada Monthly meeting

Nice initiative!

Take me into account ;-)

Some subjects I'd love to debate with connoisseurs:

\* UTF8-Unicode-UCS: a lot of libraries are offering strings manipulation. State of the art? (Gnat extensions, GnatColl, Matreska, Gnoga, ...)

\* OS system usage (as (system shell) scripts, in place of Perl, Python, ...): GNAT extensions; Florist; GnatColl; SoWebIO; ...

\* Windowing (2D) systems: future of GTK/Glade; Qt6/Qt Design Studio; GWindows; Apple new SwiftUI MV paradigm; wxWidgets; Tk/TCL

\* How let anyone collaborate to AdaForge's new up-todate 2022 Ada resources gathered all over the internet ;-) Through GitHub?

Cheers, with a fresh Belgian Ada 10° William

From: Rod Kay <rodakay5@gmail.com> Date: Sun, 1 May 2022 02:33:47 +1000

#### > Nice initiative!

Agree. Count me in Fer :).

> Some subjects I'd love to debate with connoisseurs:

If by 'OS system usage' you mean using Ada to write shell-like scripts then you may be interested in aShell. It builds on Florist to allow Ada applets to more easily call and interact with OS commands.

The last release allowed OS commands to be called but only from a single Ada task. Atm, work is being done on supporting task safe commands (via a spawn manager).

The next release will contain the task safe commands and be Alire enabled, and should occur in the next month or so (Lady Ada willing).

From: Luke A. Guest <laguest@archeia.com> Date: Sat, 30 Apr 2022 18:01:24 +0100

- > Some subjects I'd love to debate with connoisseurs:

- \* UTF8-Unicode-UCS: a lot of libraries are offering strings manipulation. State of the art? (Gnat extensions, GnatColl, Matreska, Gnoga, ...)

- \* Windowing (2D) systems: future of GTK/Glade; Qt6/Qt Design Studio; GWindows; Apple new SwiftUI MV paradigm; wxWidgets; Tk/TCL

Oh, I suppose I'll have to attend given I have experience with those.

From: Fernando Oleo Blanco <irvise\_ml@irvise.xyz> Date: Tue, 3 May 2022 21:06:21 +0200

Thank you all for your answers :)

It seems that there is some interest to have a meeting from time to time. Other communication channels where this proposal was posted did have other people who liked the idea. For this reason, I would like to share some extra bits.

- I think the duration of such a monthly meeting could last for an hour, an hour and a half.

- Could take place monthly in a varying schedule to suite some people better than other depending on the month.

- The level of preparation is much much lower than FOSDEM or similar venues. This is more about building community than actually making this a serious thing.

- The structure could be the following:

- < 5 mins to share important news and announcements.

- < 30 mins reserved for already predefined talks/topics. More on this later.

- < 15 min discussion topic. Maybe there is something that needs a few words, it's the topic of the day.

- < 15 mins to let people share their work or improvements.

- The main meeting ends here.

- Open questions and answers and general discussion/beer.

- The main section of the meeting (without Q&A and open discussion) could be recorded and uploaded to video hosting sites. I know a few people already reupload the videos from FOSDEM, so I could as them to do the same for us. This would allow us to keep a log of the meetings:)

- We could use Jitsi, a libre conference software. I know it has recording capabilities, but I think only for Youtube... :/ We will see whether Jitsi actually works or not...

If this works, I think we could start inviting people to share their work and reserve time for their presentations. That is what the second section of the proposed schedule is about. At the beginning, obviously, we will focus on making sure that the meetings work and see if there is enough recurring interest in them.

Regarding the actual planning. I will not make it for the month of May unless someone steps and helps a fair bit. On a personal note, I have a lot of work and it will just keep increasing so I cannot ensure that I will be able to pull something like this alone. FOSDEM was already a bit exhausting :P

I also want to see what you have to offer both in direct help or if you have projects that you want to talk about, presentations, etc. Some of you already commented on it, so I am happy.

What is your opinion about this? I would need feedback :)

Also, please, feel free to repost this to other social media. The more Ada users and people interested in Ada the better! If you want a contact, feel free to email me at "irvise(AT)irvise.xyz".

Bye now :D Fer

#### CFP: ACM SIGAda HILT 2022 Workshop at ASE '22, October 14, 2022

From: Tucker Taft

<tucker.taft@gmail.com> Subject: CFP: ACM SIGAda HILT 2022 Workshop at ASE '22, October 14, 2022 Date: Thu, 12 May 2022 18:30:15 -0700 Newsgroups: comp.lang.ada

Please consider contributing to this workshop sponsored by ACM SIGAda: HILT-2022 - Supporting a Rigorous Approach to Software Development

This is the seventh in the HILT series of conferences and workshops focused on the use of High Integrity Language Technology to address challenging issues in the engineering of highly complex critical software systems. High Integrity Language Technologies have been tackling the challenges of building efficient, safe, reliable software for decades. Critical software as a domain is quickly expanding beyond embedded real-time control applications to the increasing reliance on complex software for the basic functioning of businesses, governments, and society in general.

For its 2022 edition, HILT will be a workshop of the 37th IEEE/ACM International Conference on Automated Software Engineering, ASE'2022. The workshop will be held on October 14th 2022.

See ASE'2022 (https://conf.researchr.org/ home/ase-2022) for details on the venue and registration.

#### Topics

HILT 2022 will focus on the increasing synergies between formal methods (theorem provers, SAT, SMT, etc.), advanced static analysis (model checking, abstract interpretation), software design and modeling, and safety-oriented languages. From separate fields of research, we now observe a stronger interconnection between formal methods, advanced analytics, modeling and design of software, and safety features in programming languages. Programming languages for safety-critical systems now routinely integrate theorem proving capabilities like C/ACSL or Ada/SPARK2014. Theorem provers such as Coq, Lean, or Isabelle have established themselves as a viable strategy to implement compilers or properly define the semantics of domain-specific languages. Tools for verifying modeling languages such as AADL, Lustre, and Simulink are becoming more widely available, and with the emergence of the Rust language and the release of Ada 2022, safety is rising to the top of concerns for critical systems developers.

The HILT'2022 workshop seeks to explore ways High Integrity Language Technologies leverage recent advances in practical formal methods and language design to deliver the next generation of safety-critical systems.

#### Call for Papers

This workshop is focused on the practical use of High Integrity languages, technologies, and methodologies that enable expedited design and development of software-intensive systems.

Key areas of interest include experience and research into:

Practical use of formal methods at industrial scale

IDE-support for formal methods

Model-level analysis tools for systems like SysML, AADL, Lustre, or Simulink

Continuous Integration and Deployment based on advanced static analysis tools

Safety-Oriented Programming Language features \*Qualification of Language Tools for critical systems use

The workshop accepts either short abstracts (2-3 pages) for presentation, or full papers (up to 8 pages).

Submissions should conform, at time of submission, to the ACM Proceedings Template: https://www.acm.org/publications/ proceedings-template.

The workshop proceedings will be published in the ACM Ada Letters. Authors of accepted papers will be invited to contribute to a special issue of the Springer Journal on Software and Tools for Technology Transfer (STTT).

#### Paper submission

Submit your paper through Easychair at https://easychair.org/conferences/ ?conf=hilt22

#### Important Dates

Submission Deadline: July, 1 2022

Notification to authors: August, 1 2022

Workshop Date: October 14th 2022.

#### From: Tucker Taft

<tucker.taft@gmail.com> Date: Thu, 12 May 2022 18:34:51 -0700

> Please consider contributing to this workshop sponsored by ACM SIGAda: HILT-2022 - Supporting a Rigorous Approach to Software Development

Website is:

https://conf.researchr.org/home/hilt-2022

#### Press Release - AEiC 2022, Ada-Europe Reliable Softw. Technol.

[The event took place during 14-17 June, so this announcement is for the record. —arm]

From: Dirk Craeynest

<dirk@orka.cs.kuleuven.be> Subject: Press Release - AEiC 2022, Ada-Europe Reliable Softw. Technol. Date: Sun, 12 Jun 2022 20:59:37 -0000 Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

#### FINAL Call for Participation

\*\*\*UPDATED Program Summary \*\*\*

26th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2022)

14-17 June 2022, Ghent, Belgium

www.ada-europe.org/conference2022

Organized by Ada-Europe in cooperation with ACM SIGAda, SIGPLAN, SIGBED,

the Ada Resource Association (ARA), and Ghent University

> #AEiC2022 #AdaEurope #AdaProgramming

\*\*\* Final Program available on the conference web site \*\*\*

\*\*\* Add tutorials and/or a workshop to your conference registration \*\*\*

www.ada-europe.org/conference2022/ tutorials.html

\* Welcome Event on Tuesday evening \*

Press release:

26th Ada-Europe Int'l Conference on Reliable Software Technologies.

International experts meet in Ghent.

Ghent, Belgium (12 June 2022) - Ada-Europe together with the University of Ghent, Belgium, organizes from 14 to 17 June 2022 the 26th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2022). The event is in cooperation with the Ada Resource Association (ARA), and with ACM's Special Interest Groups on Ada (SIGAda), on Embedded Systems (SIGBED) and on Programming Languages (SIGPLAN).

The Ada-Europe series of conferences has over the years become a leading international forum for providers, practitioners and researchers in reliable software technologies. These events highlight the increased relevance of Ada in general and in safety- and securitycritical systems in particular, and provide a unique opportunity for interaction and collaboration between academics and industrial practitioners.

This year's conference offers 4 tutorials, a keynote and an invited presentation, a technical program of 7 sessions with refereed papers industrial, work-in-progress, and vendor presentations, a social program with exciting sightseeing, 2 workshops and a Birds-of-a-Feather session.

Four tutorials are scheduled on Tuesday, targeting different audiences:

- "Moving up to Ada 2022", by S. Tucker Taft, AdaCore, USA;

- "Numerics for the non-numerical analyst", by Jean-Pierre Rosen, Adalog, France;

- "The ALiRe Package Manager", by Fabien Chouteau, France, and Alejandro Mosteo, Spain;

- "The HAC Ada Compiler", by Gautier de Montmollin, Switzerland.

Vendors and organisations will be present in the networking area on Wednesday and Thursday include AdaCore, VECTOR, and Ada-Europe.

Two eminent speakers have been invited to deliver a talk on each of the core conference days:

- on Wed Jun 15, a spotlight talk (remote) by Anita Carleton, Software Engineering Institute, Carnegie Mellon University, USA, about "Envisioning the Future of Software Engineering";

- on Thu June 16, a keynote talk by Cristina (Crista) Lopes, School of Computer Sciences, University of California at Irvine, USA, who will present her study on "The Curious Case of Code Duplication in Github".

The technical program on Wednesday and Thursday presents 7 sessions with 9 journal-track refereed technical papers, 9 industrial, 12 work-in-progress, and 2 vendor presentations in sessions on: Uses of Ada, Real-Time Systems 1, Development Challenges, Advanced Systems, Special-Purpose Systems, Verification Challenges, Real-Time Systems 2.

On Friday the conference hosts for the 7th year the workshop on "Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering" (DeCPS 2022), as well as the International Workshop "AADL Unveiled by its Practitioners (ADEPT), and a Birds-of-a-feather (BoF) Meeting on the "Future of ASIS and Vendor Independent Tools".

Peer-reviewed papers have been submitted to a special issue of the Journal of Systems Architecture and are heading towards final acceptance as open-access publications. Industrial and work-inprogress presentations, together with tutorial abstracts, will be offered publication in the Ada User Journal, the quarterly magazine of Ada-Europe.

The social program includes for all tutorial and conference participants on Tuesday evening a Welcome Aperitif with beer tasting (sponsored by VECTOR) in the "Il Trovatore" lounge, a restored medieval cellar. On Wednesday evening, a private visit to the Gothic-style St Bavo's Cathedral and its artistic treasures including the world-famous Lam Gods altarpiece, followed by the Conference Banquet in the Abt, the only brasserie from the famous Orval Trappist beer brewery. And on Thursday evening a boat tour in the canals that encircle the medieval center of Ghent, followed by a conference dinner at the Carlos Quinto restaurant, a short walk across the heart of town from the boat pier.

The Best Presentation Award will be offered during the Closing session.

The full program is available on the conference web site.

Online registration is still possible.

Latest updates:

The 16-page "Final Program" is available at www.ada-europe.org/conference2022/ docs/AEiC\_2022\_Final\_Program.pdf.

Check out the tutorials in the PDF program, or in the schedule at www.ada-europe.org/conference2022/ tutorials.html.

Registration is done on-line. For all details, select "Registration" at www.adaeurope.org/conference2022 or go directly to https://registration.ada-europe.org.

A printed Conference Booklet with abstracts of all technical papers

and industrial presentations will be included in every conference

handout, and is available at www.ada-europe.org/conference2022/ docs/AEiC\_2022\_Booklet\_of\_ Presentations.pdf.

AEiC 2022 is sponsored by Ada-Europe (www.ada-europe.org), AdaCore (www.adacore.com), and VECTOR (www.vector.com/int/en/products/ products-a-z/software/vectorcast).

Help promote the conference by advertising it.

Recommended Twitter hashtags: #AEiC2022 #AdaEurope #AdaProgramming.

Our apologies if you receive multiple copies of this announcement.

Please circulate widely.

Dirk Craeynest, AEiC 2022 Publicity Chair

Dirk.Craeynest@cs.kuleuven.be

\* 26th Ada-Europe Int. Conf. Reliable Software Technologies (AEiC 2022)

\* June 14-17, 2022, Ghent, Belgium \* www.ada-europe.org/conference2022

(V6.1)

### Ada/SPARK Crate of the Year 2022

From: Fabien Chouteau

<fabien.chouteau@gmail.com> Subject: Ada/SPARK Crate Of The Year is back!

Date: Tue, 28 Jun 2022 05:55:20 -0700 Newsgroups: comp.lang.ada

https://blog.adacore.com/announcing-the-2022-ada-spark-crate-of-the-year-award

[AdaCore offers 3 prizes of \$2,000 each for the following categories: best overall

Ada crate, best crate written in SPARK and/or contributing to the SPARK ecosystem, and best Ada or SPARK crate for embedded software. Candidates can be submitted until the end of the year. —arm]

#### Ada-related Resources

[Delta counts are from May 9th to July 18th. —arm]

#### Ada on Social Media

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Ada on Social Media Date: 18 Jul 2022 14:53 CET To: Ada User Journal readership

Ada groups on various social media:

| LinkedIn: 3_328 (+26) members            | [1] |

|------------------------------------------|-----|

| Reddit: 8_078 (+73) members              | [2] |

| Stack Overflow:<br>2 238 (+26) questions | [3] |

- 2\_238 (+26) questions

- Libera.Chat: 75 (=) concurrent users [4]

- Gitter: 123 (+8) people

- Telegram: 143 (+4) users

- Twitter: 30 (=) tweeters

- 75 (+22) unique tweets

[5]

[6]

[7]

[7]

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

- [1] https://www.linkedin.com/groups/ 114211/

- [2] http://www.reddit.com/r/ada/

- [3] http://stackoverflow.com/questions/ tagged/ada

- [4] https://netsplit.de/channels/ details.php?room=%23ada& net=Libera.Chat

- [5] https://gitter.im/ada-lang

- [6] https://t.me/ada\_lang

- [7] http://bit.ly/adalang-twitter

### **Repositories of Open Source Software**

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Repositories of Open Source software Date: 18 Jul 2021 15:16 CET To: Ada User Journal readership Rosetta Code: 915 (+15) examples 39 (+1) developers GitHub: 763\* (=) developers Sourceforge: 244 (-30) projects Open Hub: 214 (=) projects

- Alire: 260 (+17) crates

- Bitbucket: 87 (-1) repositories

Codelabs: 53 (=) repositories

AdaForge: 8 (=) repositories

\*This number is unreliable due to GitHub search limitations.

[9]

- [1] http://rosettacode.org/wiki/ Category:Ada

- [2] http://rosettacode.org/wiki/ Category:Ada User

- [3] https://github.com/search? q=language%3AAda&type=Users

- [4] https://sourceforge.net/directory/ language:ada/

- [5] https://www.openhub.net/tags? names=ada

- [6] https://alire.ada.dev/crates.html

- [7] https://bitbucket.org/repo/all? name=ada&language=ada

- [8] https://git.codelabs.ch/? a=project\_index

[9] http://forge.ada-ru.org/adaforge

#### Language Popularity Rankings

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Ada in language popularity rankings

Date: 18 Jul 2021 15:51 +0100 To: Ada User Journal readership

[Positive ranking changes mean to go up in the ranking. —arm]

- TIOBE Index: 30 (-3) 0.38% (-0.08%)

- PYPL Index: 17 (=) 0.86% (+0.05%) [2]

[1]

- IEEE Spectrum (general): 31 (=) Score: 38.8 (=) [3]

- IEEE Spectrum (embedded): 9 (=) Score: 38.8 (=) [3]

- [1] https://www.tiobe.com/tiobe-index/

- [2] http://pypl.github.io/PYPL.html

- [3] https://spectrum.ieee.org/ top-programming-languages/

### Source-code Hosting with Ada Build Tools?

From: Niklas Holsti <niklas.holsti@tidorum.invalid> Subject: Source-code hosting with Ada build tools? Date: Fri, 25 Mar 2022 18:56:56 +0200 Newsgroups: comp.lang.ada

I'm planning to move a biggish Ada project from being hosted on my own website to some hosting service, such as GitHub or OSDN. Are there any such services that, in addition to a source-code repository, bug reporting, etc., also offer access to Ada compilers (that is, gnat) for building the SW, ideally on several platforms? At the moment, my main candidate is OSDN, but they explicitly do not provide any compilers.

TIA for any suggestions, whether with build tools or without.

From: Simon Wright <simon@pushface.org> Date: Fri, 25 Mar 2022 21:00:58 +0000

Github Actions do this; though I've never set them up for myself.

From: Niklas Holsti <niklas.holsti@tidorum.invalid> Date: Sat. 26 Mar 2022 21:15:16 +0200

> Github Actions do this; though I've never set them up for myself.

Are you sure that they provide Ada compilers that can be called in an Action?

I tried to find out on the GitHub website, but could not find any list of all the supported languages, and the specific languages they mentioned did not include Ada, and the Search function found nothing about Ada compilation.

From: Luke A. Guest <laguest@archeia.com> Date: Fri, 25 Mar 2022 21:01:31 +0000

> Github Actions do this; though I've never set them up for myself.

AdaCore has one for GNAT.

From: Luke A. Guest <laguest@archeia.com> Date: Sat, 26 Mar 2022 21:04:13 +0000

- > Are you sure that they provide Ada compilers that can be called in an Action?

- https://github.com/marketplace/actions/ ada-actions-toolchain

- From: Niklas Holsti <niklas.holsti@tidorum.invalid> Date: Sat, 26 Mar 2022 23:46:26 +0200

- > https://github.com/marketplace/actions/ ada-actions-toolchain

Thanks! Looks like GitHub will be my choice, although I am usually a bit Microsoft-allergic.

From: Luke A. Guest <laguest@archeia.com> Date: Sun, 27 Mar 2022 16:59:47 +0100

> Thanks! Looks like GitHub will be my choice, although I am usually a bit Microsoft-allergic.

#### Aren't we all?

From: Tero Koskinen <tero.koskinen@iki.fi> Date: Tue, 29 Mar 2022 21:38:09 +0300

I have my Ahven library and other things at Sourcehut.org:

https://hg.sr.ht/~tkoskine/ahven/

They offer generic build service also. For example see one build log from Ahven: https://builds.sr.ht/~tkoskine/job/675294

The build configurations are Yaml files: https://hg.sr.ht/~tkoskine/ahven/browse/ .builds?rev=tip

Of course, the software on the build service is limited to open source operating systems and compilers (Linux, \*BSDs, GNAT).

Commercial Ada compilers (like ObjectAda or Janus/Ada) are not supported.

For commercial Ada compilers, I run internal homelab network with Jenkins master on RPi4 and couple of Windows build slaves, which fetch the source code from Sourcehut periodically.

And before starting to use Sourcehut, read the caveats page:

https://sourcehut.org/alpha-details/

I also think that Sourcehut doesn't support hosting of "random" binaries, like handcrafted release tar balls. These kinds of things I locate on a separate virtual server.

#### Ada-related Tools

#### HAC v.0.0996

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Subject: Ann: HAC v.0.0996 Date: Sat, 22 Jan 2022 01:41:09 -0800 Newsgroups: comp.lang.ada

HAC (HAC Ada Compiler) is a small, quick, open-source Ada compiler, covering a subset of the Ada language. HAC is itself fully programmed in Ada.

Web site: http://hacadacompiler.sf.net/

Source repositories:

#1 svn: https://sf.net/p/hacadacompiler/ code/HEAD/tree/trunk/

#2 git: https://github.com/zertovitch/hac

\* Main improvements since v.0.095:

- range checks on discrete subtype assignment (:=) and conversion

- short-circuit logical operators: "and then", "or else"

- for S = Scalar subtype: S'First, S'Last, S'Succ, S'Pred, S'Pos, S'Val, S'Image, S'Value, S'Range attributes

- for A = array object or array subtype: A'First [(N)], A'Last [(N)], A'Range [(N)], A'Length [(N)] attributes

- "&", "<", ">", "=", "/=" operators defined for the String type (additionally to HAL.VString type)

- CASE choices admit ranges

- forward declarations for subprograms

#### Enjoy!

PS: for Windows there is an integrated editor that embeds HAC: LEA: http://l-e-a.sf.net

#### HAC v.0.1

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Subject: Ann: HAC v.0.1 Date: Sat, 14 May 2022 05:35:55 -0700 Newsgroups: comp.lang.ada

[Omitted common info to previous HAC announcements. —arm]

\* Main improvements since v.0.0996:

- packages and subpackages are now supported

- modularity: packages and subprograms can be standalone library units, stored in individual files with GNAT's naming convention, and accessed from other units via the WITH clause

- validity checks were added for a better detection of uninitialized variables.

Package examples and modularity tests have been added. Particularly, a new PDF producer package with a few demos is located in the ./exm/pdf directory.

Enjoy! Gautier

PS: for Windows, there is an integrated editor that embeds HAC:

LEA: http://l-e-a.sf.net

PPS: HAC will be shown at the Ada-Europe conference (presentation + tutorial)

http://www.ada-europe.org/ conference2022/

From: Doctor Who <doc@tardis.org> Date: Sat, 14 May 2022 18:05:55 +0200

Which subset of the Ada language is covered?

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Date: Sat, 14 May 2022 22:24:04 -0700

> which subset of the Ada language is covered?

Quoting from ./doc/hac.txt (section "Language subset"):

"The available Ada language subset supported by HAC is so far, roughly, the "Pascal subset", plus tasking, plus packages, less pointers. From a different perspective, HAC supports Ada 83, less pointers, less generics, less unconstrained types, plus a few items from Ada 95 and 2005. Recursion and nested subprograms are supported."

and: "Tasks are implemented, but not working yet."

#### From: Leo Brewin

<leo.brewin@monash.edu> Date: Sun, 15 May 2022 10:14:41 +1000

I just tested this on macOS Monterey 12.3.1 and it works perfectly out of the box (as expected for Ada code :).

#### Great work Gautier!

From: Bill Findlay <findlaybill@blueyonder.co.uk> Date: Sun, 15 May 2022 02:39:36 +0100

> I just tested this on macOS Monterey 12.3.1 and it works perfectly out of the box (as expected for Ada code :)

You beat me to it by an hour!

> Great work Gautier!

Ditto.

#### HAC v.0.2

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Subject: Ann: HAC v.0.2 Date: Sat, 25 Jun 2022 00:43:14 -0700 Newsgroups: comp.lang.ada

[Omitted common info to previous HAC announcements. —arm]

\* Main improvements since v.0.1:

- a program run by HAC can exchange data with the program running HAC, through dynamically registered call-backs

- see package HAC\_Sys.Interfacing and demos: src/apps/exchange\_native\_side.adb src/apps/exchange\_hac\_side.adb

- the compiler checks that all choices in a CASE statement are covered

- the compiler performs more compiletime range checks and optimizes away useless run-time checks when it's safe to do so.

#### AdaStudio-2022 Rel. 12/04/2022 Free Edition

From: Leonid Dulman

<leonid.dulman@gmail.com>Subject: Announce: AdaStudio-2022 release

12/04/2022 free edition Date: Wed, 13 Apr 2022 01:19:51 -0700 Newsgroups: comp.lang.ada

I'm pleased to announce AdaStudio-2022.

It's based on Qt-6.3.0-everywher opensource (expanded with modules from Qt-5.15: qtgraphicaleffects qtgamepad qtspeech qtx11extras qtwinextras), VTK-9.1.0, FFMPEG-5.1, OpenCV-4.5.5, SDL2-2.0.20, MDK-SDK (wang-bin) Qt6ada version 6.3.0 open source and qt6base.dll, qt6ext.dll (win64), libqt6base.so, libqt6txt.so (x86-64) built with Microsoft Visual Studio 201 x64 Windows, gcc amd64 in Linux. Package tested with GNAT gpl 2020 Ada compiler in Windows 64bit, Linux amd64 Debian 11.1 AdaStudio-2022 includes next modules: qt6ada, vtkada, qt6mdkada, qt6cvada (with face recognition) and voice recognizer.

Qt6Ada is built under GNU LGPLv3 license

https://www.gnu.org/licenses/ lgpl-3.0.html.

Qt6Ada modules for Windows, Linux (Unix) are available from Google drive https://drive.google.com/drive/folders/ 0B2QuZLoe-yiPbmNQRI83M1dTRVE? resourcekey=0-b-M35gZhynB6-LOQww33Tg&usp=sharing

WebPage is https://r3fowwcolhrzycn2yzlzzwon.drv.tw/AdaStudio/index.html

[List of detailed files omitted. -arm]

The full list of released classes is in "Qt6 classes to Qt6Ada packages relation table.pdf"

The simple manual how to build Qt6Ada application can be read in "How to use Qt6ada.pdf"

If you have any problems or questions, let me know.

Leonid (leonid.dulman@gmail.com)

#### **Generic Image Decoder v.10**

From: Gautier Write-Only Address <gautier\_niouzes@hotmail.com> Subject: Ann: Generic Image Decoder v.10 Date: Sun, 17 Apr 2022 03:26:25 -0700 Newsgroups: comp.lang.ada

There is a new release of GID - the Generic Image Decoder.

Home page: http://gen-img-dec.sf.net/

Project page #1: http://sf.net/projects/gen-img-dec/

Project page #2: https://github.com/zertovitch/gid

#### New in V.10

- \* Added a decoder for the QOI (Quite OK Image) format

- \* Added an "all RGB" demo

#### About GID

The Generic Image Decoder (GID) is an Ada package for decoding a broad variety of image formats, from any data stream, to any kind of medium, be it an inmemory bitmap, a GUI object, some other stream, arrays of floating-point initial data for scientific calculations, a browser element, a device...

Animations are supported.

#### Features

- \* Standalone (no dependency on other libraries, bindings...)

- \* Unconditionally portable code: OS-, CPU-, compiler- independent code.

- \* Multi-platform, but native code built

- \* Task safe

- \* Endian-neutral

- \* Use of generics and inlining at multiple nesting levels for fast execution

- \* Free, open-source

Currently supported formats are: BMP, GIF, JPEG, PNG, PNM (PBM, PGM, PPM), QOI, TGA.

#### **SparForte 2.5**

From: Ken Burtch <koburtch@gmail.com> Subject: ANN: SparForte 2.5 Date: Wed, 27 Apr 2022 06:00:12 -0700 Newsgroups: comp.lang.ada

SparForte is my Ada-based shell, scripting language and template engine.

Version 2.5 is available from www.sparforte.com.

Changes since 2.4:

New features/examples: 23

Changes: 8

Fixes: 26

Known Issues:

On Raspian Bullseye, the calendar package has rounding errors. Possibly due to increased precision of time values in the kernel.

On FreeBSD 13, "environment corrupt" errors are being reported when the spar command runs another spar command. Possibly due to out-of-data GCC Ada for FreeBSD.

Tab completion does not work correctly on directory names containing spaces.

Change Log can be viewed here: https://www.sparforte.com/news/2022/ news apr2022.html

A summary of new features can be viewed here: https://www.pegasoft.ca/coder/ coder\_january\_2022.html

SparForte is my hobby and is built with the support of volunteers. It is open source and is about 123,000 lines of code. It has been in development since 2001.

#### GCC 12.1.0

From: Simon Wright <simon@pushface.org> Subject: ANN: GCC 12.1.0 Date: Wed, 11 May 2022 17:58:26 +0100 Newsgroups: comp.lang.ada

Find GCC 12.1.0 & tools for Intel silicon (will run on M1 silicon under Rosetta) at https://github.com/simonjwright/ distributing-gcc/releases/tag/ gcc-12.1.0-x86\_64

Built on High Sierra with Python 3.8 (because Apple have withdrawn 2.7 in Monterey).

### GCC 12.1.0 for Apple Silicon (aarch64)

From: Simon Wright <simon@pushface.org> Subject: [ANN] GCC 12.1.0 for Apple silicon (aarch64) Date: Fri, 27 May 2022 14:05:19 +0100 Newsgroups: comp.lang.ada

Find at

https://github.com/simonjwright/ distributing-gcc/releases/tag/ gcc-12.1.0-aarch64-1

#### SweetAda 0.10

From: Gabriele Galeotti <gabriele.galeotti.xyz@gmail.com> Subject: ANN: SweetAda 0.10 Date: Thu, 12 May 2022 14:54:29 -0700 Newsgroups: comp.lang.ada

I've just released SweetAda 0.10.

SweetAda is a lightweight development framework to create Ada systems on a wide range of machines. Please refer to https://www.sweetada.org.

Release notes @ https://www.sweetada.org/ release\_notes.html.

Downloads available @ https://sourceforge.net/projects/sweetada.

This release comes with a huge cleanup of the whole system, with many changes in all areas. The build system seems pretty efficient and stable, with no redundant actions, and is able to accommodate a large set of configuration.

The profile agrees with Ravenscar, and all platforms tested run OK, albeit many of them in a very simple manner. Interrupt handling is for some CPUs still only a placeholder, but many of them are able to handle at least a simple timer in order to have a raw notion of time.

There is a Monitor module (very exemplary) to do user interaction and the Srecord module that could be used as a built-in tool to execute fragments of code. The Time module should provide basic capabilities in order to manipulate a datetime.

Many other changes, large cosmetic refinements and an improved documentation. Syntax changes to adhere Ada 2012/202x and some generics removed from I/O layers to simplify the code and gain speed.

With SweetAda 0.10, I also provide new toolchains based on GCC 11.3.0 (release-20220429), you can find them at SweetAda home or at SourceForge. QEMU emulators are bumped to 7.0.0 (release-20220504).

Unfortunately, I can no longer provide OS X toolchains due to increasing difficulties in building the software (GCC and LLVM disagree on the syntax of some CPU instructions), and lack of time, sorry. But this shouldn't be a problem since SweetAda should be toolchain-agnostic.

#### Simple Components v4.62

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Subject: ANN: Simple Components v4.62 Date: Sat, 21 May 2022 12:03:59 +0200 Newsgroups: comp.lang.ada

The current version provides implementations of smart pointers, directed graphs, sets, maps, B-trees, stacks, tables, string editing, unbounded arrays, expression analyzers, lock-free data structures, synchronization primitives (events, race condition free pulse events, arrays of events, reentrant mutexes, deadlock-free arrays of mutexes), pseudorandom non-repeating numbers, symmetric encoding and decoding, IEEE 754 representations support, streams, multiple connections server/client designing tools and protocols implementations.

http://www.dmitry-kazakov.de/ada/ components.htm

Changes to the previous version:

- Pipe stream implementation added;

- GNAT 12.1 bugs worked around in several package, in particular, in GNAT.Sockets.Server;

- Bug fix in Generic\_Set procedure Replace, parameter Updated unset;

- Bug fix in Tables.UTF8\_Names procedure Replace, parameter Offset unset under circumstances.

#### PragmAda Reusable Components

From: Pragmada Software Engineering <pragmada@ pragmada.x10hosting.com> Subject: [Reminder] The PragmAda

Reusable Components Date: Wed, 1 Jun 2022 12:23:50 +0200

Newsgroups: comp.lang.ada

The PragmARCs are a library of (mostly) useful Ada reusable components provided as source code under the GMGPL or BSD 3-Clause license at https://github.com/jrcarter/PragmARC.

This reminder will be posted about every six months so that newcomers become aware of the PragmARCs. I presume that those who want notification when the PragmARCs are updated have used Github's notification mechanism to receive them, so I no longer post update announcements. Anyone who wants to receive notifications without using Github's mechanism should contact me directly.

#### A New Era for Ada/SPARK Open Source Community

From: Fabien Chouteau <fabien.chouteau@gmail.com> Subject: AdaCore Blog: A New Era For Ada/SPARK Open Source Community Date: Mon, 6 Jun 2022 01:56:27 -0700

I am sharing this here for people who might not have seen it yet:

Newsgroups: comp.lang.ada

https://blog.adacore.com/a-new-era-forada-spark-open-source-community

[The blog post announces the relicensing of several AdaCore libraries as Apache 2.0 and the discontinuation of the Community Edition in favor of the FSF branch distributed through Alire. —arm]

I will be at the Ada-Europe conference next week if someone wants to talk live about these announcements.

From: Stephen Leake <stephen\_leake@stephe-leake.org> Date: Mon, 06 Jun 2022 09:03:25 -0700

Thanks for posting this.

I hope this will reduce the differences among the GNAT versions available in the various OS releases; they've been causing headaches for Emacs ada-mode. But probably not.

#### Alire 1.2.0

From: Fabien Chouteau <fabien.chouteau@gmail.com> Subject: [ANN] Alire 1.2.0 Date: Mon, 6 Jun 2022 01:57:09 -0700 Newsgroups: comp.lang.ada

The new release is here: https://github.com/alire-project/alire/ releases/tag/v1.2.0

#### **Adalog Components**

From: J-P. Rosen <rosen@adalog.fr> Subject: [Ann] Adalog components Date: Mon, 27 Jun 2022 18:23:18 +0200 Newsgroups: comp.lang.ada

I have added a new component to ease processing of CSV files. Moreover, I have renamed package Debug to Tracer, there were too many packages called Debug around!

More details from Adalog's components page:

https://adalog.fr/en/components.html

### Ada and Operating Systems

#### **Building GNAT-FSF on FreeBSD**

From: William <william@sterna.io> Subject: Building GNAT-FSF on FreeBSD Date: Sat, 12 Feb 2022 21:09:54 +0100 Newsgroups: comp.lang.ada

I did succeed to build a modern gcc (with Ada-GNAT FSF) on my FreeBSD 13.0 serveur. :-)

Fernando Oleo Blanco was very inspiring to me (NetBSD porting), and I use Simon J. Wright portings to macOS for my Hackingtosh.

So I decided to do it too!

For now I did a quick try with plain gcc «out of the box»: (story short)

- Install gcc6-aux pkg from FreeBSD port (2014 -- Last Updated on 2022-01-26). (see also http://www.dragonlace.net)

- 2. get gcc 10.3 src from GNU.org and compile it with gcc6-aux (gnat compiler seems OK)

- 3. get gcc 11.2 src from GNU.org and compile it with the just installed gcc/gnat 10.3

In the first place I thought it would not be successful ...

Now it's time to build) and run the ACATS 4.1y

I took a look at Simon's ACATS Testsuite on SourceForge, but I need to understand those automated scripts.

I'd like to parallelise a maximum of ACATS sub-projects in order to reduce time.

#### WIP!!

See you later, William

From: Simon Wright <simon@pushface.org> Date: Mon, 14 Feb 2022 09:52:31 +0000

The section "Testing in GCC" in the README tells how to run the tests within the GCC framework that allows parallel running. Note, you'll probably have to hammer C-c to abort a parallel run, the script doesn't respond well to that.

I would have liked to get parallelising working, but those scripts! eww!

From: Simon Wright <simon@pushface.org> Date: Mon, 14 Feb 2022 11:45:05 +0000!

See this thread: https://gcc.gnu.org/ pipermail/gcc/2018-July/226729.html [This thread discusses how to interrupt Ada tests, as Ctrl-C fails sometimes. –arm]

I'm not sure, but I think that GCC/Ada folk regard the ACATS (2.6, I think) in GCC as more of a confidence thing (DEC used to call it an IVP, Installation Verification Procedure) than a full check.

[...]

#### Ada Inside

#### **Controlling ST7789 Screen** on a RPi Pico

From: Björn Lundin

<br/>

<b.f.lundin@gmail.com><br/>

Subject: Controlling st7789 screen from<br/>

Ada on a rpi Pico?<br/>

Date: Tue, 15 Feb 2022 22:18:44 +0100

Newsgroups: comp.lang.ada

So, I got my first Raspberry Pico :-)

I also got a 'Pico Explorer Base' device at https://shop.pimoroni.com/products/ pico-explorer-base

This thing has a st7789 screen. I got it to work with Python.

Now - I see that there is work done with the Pico and Ada - the https://pico-doc.synack.me seems to be a good place to start.

I wonder if there is any port done already for this screen in Ada? Google points me to some python and some c/c++implementations (whereof Pimoroni's Github has some)

I also came across uGUI http://embeddedlightning.com/ugui/ which looks interesting. Same question there. Ada-port?

I hesitate to start translating one of the clibraries - butI probably will when time permits if nothing is already in place.

From: jer...@synack.me <jeremy@synack.me> Date: Tue, 15 Feb 2022 18:03:26 -0800

The Pimoroni Picosystem uses a ST7789 screen, I have a driver for it in picosystem\_bsp: https://github.com/JeremyGrosser/ picosystem\_bsp/tree/master/src

I didn't implement every feature or video mode that the controller supports, so you may need to modify it to suit your needs.

From: Björn Lundin <b.f.lundin@gmail.com> Date: Wed, 16 Feb 2022 08:19:07 +0100

Perfect - just what I was looking for - thanks.

And thanks for the effort of bringing Ada to the Pico

From: Fabien Chouteau <fabien.chouteau@gmail.com> Date: Fri, 18 Feb 2022 01:31:20 -0800

> I also came across uGUI <http://embeddedlightning.com/ugui/> which looks interesting

I have an Ada binding [1] for the excellent lvgl GUI library [2]. You can get it from Alire: [3].

It is not in a very beginner friendly shape, but it works. I am trying to do a new version that should be easier to integrate into existing projects.

Don't hesitate to say hello on the Ada Gitter chat if you want a little help setting it up.

[1] https://github.com/ Fabien-Chouteau/lvgl-ada

[2] https://github.com/lvgl/lvgl

[3] https://alire.ada.dev/crates/ lvgl\_ada.html

#### Ada in James Webb Space Telescope? (Cont.)

[Refer to AUJ 43-1: Ada in James Webb Space Telescope? —arm]

From: 姚飞 <yaofei509@gmail.com> Subject: Re: is Ada used in James Webb Space Telescope software?

Date: Sat, 23 Apr 2022 02:17:05 -0700 Newsgroups: comp.lang.ada

Interesting. I hadn't heard of the MA31750 but it appears to be a 16 bit processor that implements the MIL-STD-1750A instruction set(!), which I didn't know about either. Apparently it was made in the 1980s but has since been superseded by SPARC architecture cpu's.

MAS31750 + XGC M1750-Ada is a very wonderful combination, we use them for several large satellites, and they are working in orbit now.

### Ada and Other Languages

#### **Comparing Languages wrt Energy, Speed, and Memory Use**

From: Jerry <list\_email@icloud.com> Subject: Comparing languages wrt energy,

speed, and memory use Date: Sun, 20 Feb 2022 14:59:29 -0800 Newsgroups: comp.lang.ada

This paper comparing 27 languages with respect to energy use, speed, and memory use is interesting. Of course Ada fares very well.

https://greenlab.di.uminho.pt/ wp-content/uploads/2017/10/sleFinal.pdf It is linked from this Slashdot page which I'm sure is full of useless chatter.

https://developers.slashdot.org/story/22/ 02/20/0143226/is-it-more-energyefficient-to-program-in-rust

From: Fernando Oleo Blanco <irvise\_ml@irvise.xyz> Date: Tue, 22 Feb 2022 21:10:15 +0100

I am going to leave a few comments regarding this paper that I believe everybody should know. Most if not all of these points are known and have been discussed pretty much everywhere; but a lot of people still don't know them or decide to not know.

The programs are taken from the Programming Language Benchmark Game. It is a really cool place that has been providing relevant performance data for a lot of languages and comparisons between them.

Here are a few issues:

- 1. Quite a few languages are not using heavily optimised code. Ada is one of them. Some of those programs are written as direct translations from other languages from people that did not know the target language.

- 2. Quite a few of those implementations have not been touched in years. Some of the improvements that may have taken place in the language/compiler/tools may not be taken advantage of. For example, the Ada examples are compiled with -gnatNp. Can anybody say what that flag does? x)

- 3. C/C++/Rust programs are competing on getting the best results. Other languages are lagging behind. For example, Fortran could do much better. For a couple of years, the Fortran community has been improving the code little by little and they have managed to improve their results.

- 4. There are a few controversies. Some languages are not allowed to use higher performance libraries while others are allowed their stl or equivalent that do actually use the same tools as those libraries. There are a few other examples.

As the very Game page says, do not take the benchmark seriously. But the communities whose languages are on top, they do not care. Ada has been left behind since very few or nobody is actually taking a look at the code and optimising it...

We may want to improve some of these tests as a community :)

Here are some relevant links:

- Benchmark game:

- https://benchmarksgameteam.pages.debian.net/benchmarksgame/

Source code: https://salsa.debian.org/ benchmarksgame-team/ benchmarksgame

From: J-P. Rosen <rosen@adalog.fr> Date: Tue, 22 Feb 2022 21:49:25 +0100

> [good remarks snipped]

Let me add another one: this benchmark does not consider the energy (electrical and human) needed to write and debug the program... That could also make a difference for Ada!

Real ecological balance, taking everything into account, is tricky...

#### From: G.B.

<br/>

<bauhaus@notmyhomepage.invalid><br/>

Date: Thu, 24 Feb 2022 08:42:40 +0100

> Here are a few issues:

One issue is Isaac Gouy's clever approach. (Not complaining. I sometimes didn't see the point, though, of adopting another new thing. For example, when a new regex library was introduced (at some point) that wins hands down by using optimization techniques you'd associate with JIT compilers or with data based optimization. Worth knowing about, but how does it help comparing languages when all you can do is link it to your program?)

> 1. Quite a few languages are not using heavily optimised code

Can you be specific? For example, at least one program currently leads by making extensive use of x86 intrinsic ops.

Some use OMP with intrinsic 128bit ops. Does GNAT have a similar parallel loop in the language yet?

> 2. Quite a few of those implementations have not been touched in years.

Yet, some Ada program versions #N+m used to run faster than #N. They now have their speed difference wiped out or even reversed... I see -march=ivybridge now, so the hardware has likely changed.

> For example, the Ada examples are compiled with -gnatNp. Can anybody say what that flag does? x)

GNAT User's Guide explains. (su-p-press and front end i-N-lining)

> 3. C/C++/Rust program are competing on getting the best results. Other languages are lagging behind. For example, Fortran could do much better.

How would Fortran do much better? Can Ada learn from that?

[...]

From: Fernando Oleo Blanco <irvise\_ml@irvise.xyz> Date: Thu, 24 Feb 2022 10:13:46 +0100

> Can you be specific? For example, at least one program currently leads by making extensive use of x86 intrinsic ops.

> Some use OMP with intrinsic 128bit ops. Does GNAT have a similar parallel loop in the language yet?

Yes, take a look at https://benchmarksgameteam.pages.debian.net/benchmarksgame/ program/nbody-gnat-2.html

it is taken from the Pascal implementation and uses intrinsics. My point is that some of these programs are not very Ada-like. As far as I remember, there was one ported from Lua.

Ada 2022 will have a parallel keyword. However, it is still not supported in FSF GNAT, which is the one being used. Also, the benchmarks are Ada 2012.

> GNAT User's Guide explains. (suppress and front end i-N-lining)

Correct, but that switch has been deprecated for years, it is no longer documented anywhere in the new GNAT releases:

https://gcc.gnu.org/onlinedocs/ gcc-11.2.0/gnat\_ugn.pdf

> How would Fortran do much better? Can Ada learn from that?

Fortran is using Intel's compiler, which is known to be one of the best. Fortran compilers can much more easily generate SIMD code and parallelise loops automatically if the code is idiomatic.

Also, Fortran was not fourth in the race a while ago. For example Ada overtook Fortran for a small while. December 2018:

https://web.archive.org/web/ 20181204085050/ https://benchmarksgameteam.pages.debian.net/benchmarksgame/ which-programs-are-fast.html

Ada is fourth; while it was fifth in April of that same year

https://web.archive.org/web/ 20180406194535/ https://benchmarksgameteam.pages.debian.net/benchmarksgame/ which-programs-are-fastest.html

A year later, December 2019, Fortran could be fourth if it were not for that outlier

https://web.archive.org/web/ 20191225172425/ https://benchmarksgameteam.pages.debian.net/benchmarksgame/ which-programs-are-fastest.html

These are the current results:

https://benchmarksgameteam.pages.debian.net/benchmarksgame/ box-plot-summary-charts.html Take a look at the evolution of the language podium. It has always been C/C++/Rust, but starting from the fourth position there has been quite a bit of rivalry.

[...]

Some Ada programs could use better algorithms, data structures, more up-todate syntax and parallelism. Some programs could also be made a bit prettier.

The crux of the issue is that you can pretty much always get peak performance for non-GC languages if you use the same techniques, libraries, algos, state of the art compilers, etc. And in a lot of real world cases, even GC languages are not an issue, see Go, Erlang, Julia, Lisp (SBCL), Nim...

But as someone (I believe it was the dean of TUM (Technische Universität München)) once said: "Everybody knows that rankings are flawed, but it is always better to be on top." The benchmark game is, after all, a game. But some people took it too seriously. It is just like Football hooligans.

From: 25.Bx943 <25bz493@nada.net> Date: Sat, 26 Feb 2022 22:31:19 -0500

After 30+ years, I started messing around with FORTRAN again. One of the things I noticed in the various help notes online was that programmers were actually comparing the numbers of cycles and executables size for various ways of solving any particular problem.

This sort of thinking is rarely seen these days except in the microcontroller universe - and less even there because the RAM/ROM and speed of those devices has increased.

Ada is another language where overall "efficiency" gets at least some consideration.

With energy costs rising, maybe it's time to see MORE of these discussions and comparisons. Global warming be damned - this is a MONEY issue :-)

Oh, and rising power costs may disappear the crypto sector. Those boxes full of GPUs calculating like mad - the power usage is stupendous. Once the energy-in begins to exceed the value of the Bitcoins-out - it's all over.

From: Robin Vowels <robin.vowels@gmail.com> Date: Sun, 27 Feb 2022 00:05:48 -0800

> This paper comparing 27 languages with respect to energy use, speed, and memory use is interesting.

Has this anything to do with reality?

What of the design, testing, and maintainability of programs?

#### From: Jeffrey R.Carter

<spam.jrcarter.not@spam.acm.org.not> Date: Sun, 27 Feb 2022 09:56:12 +0100

> What of the design, testing, and maintainability of programs?

There are a couple of obvious problems with this study. First, the same data structures, algorithms, and checks for validity of input and so on, in any imperative language, should give very similar machine code. Robert Dewar famously had a collection of equivalent Ada and C programs that produced identical machine code when compiled with gcc. The kind of differences reported between C and Ada or C++ shows that they are comparing apples to orangutans.

Second, there are hard data that show that, compared to low-level languages like C, Ada requires 1/2 the effort to reach deployment, and 1/40 the effort to correct post-deployment errors. The energy consumption for that additional effort should swamp the kind of small differences during execution that this study concentrates on.

#### **Ruby and Ada**

From: Mockturtle <framefritti@gmail.com> Subject: Ruby and Ada Date: Sat, 14 May 2022 01:46:06 -0700 Newsgroups: comp.lang.ada

As you can guess, my language of choice is Ada, but for small things (often "fast and dirty") or to extract stuff from text files, I use Ruby which I prefer over its direct competitor (much more popular) Python.

Then I read this [1]