# The journal for the international Ada community

# Ada User Journal

Volume 45 Number 1 March 2024

| Quarterly News Digest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Conference Calendar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                |

| Forthcoming Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                |

| Proceedings of the ADEPT: AADL by its Practitioners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

| Workshop of AEiC 2023<br>H. N. Tran et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| ADEPT 2023 Workshop Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                |

| K. Bae, P. C. Ölveczky                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| Formal Model Engineering of Synchronous CPS Designs in AADL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                |

| B. R. Larson, E. Ahmad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| BLESS Behavior Correctness Proof as Convincing Verification Artifact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                |

| J. Hughes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                |

| Mechanizing AADL in Coq – Extended Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

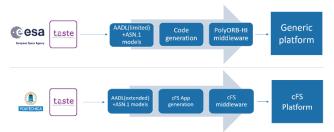

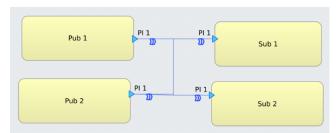

| H. Valente, M. A. de Miguel, A. G. Pérez, et . al.<br>Extension of the TASTE Toolset to Support Publisher-Subscriber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51                |

| L. Kosmidis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

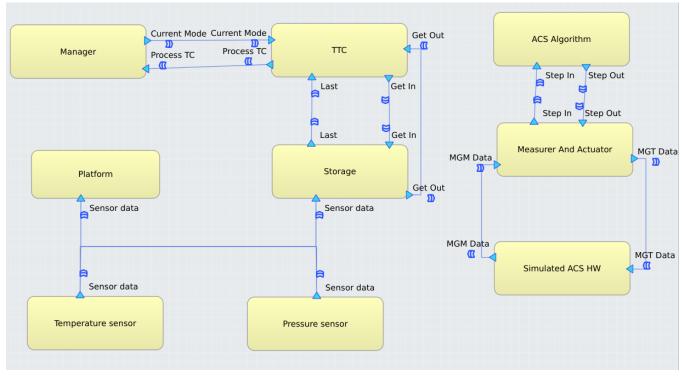

| METASAT's Model Based Design Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                |

| R. Mittal, D. Blouin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

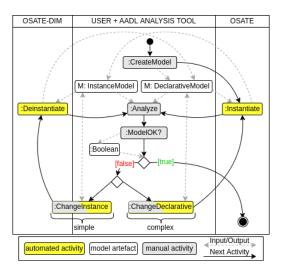

| Facilitating AADL Model Processing and Analysis with OSATE-DIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                |

| P. Dissaux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                |

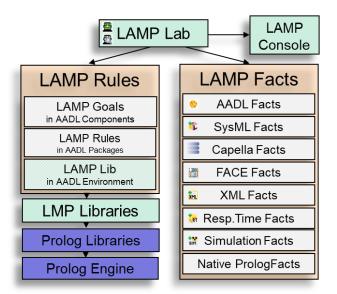

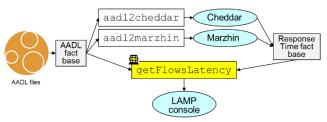

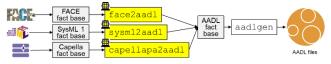

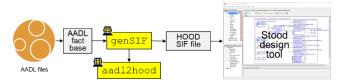

| LAMP: to Shed Light on AADL Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                |

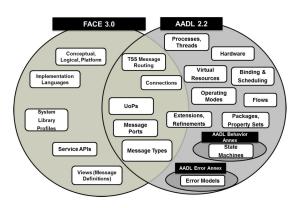

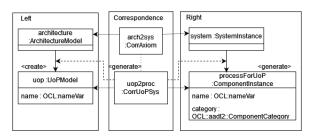

| D. Blouin, A. Bhobe, L. Pautet<br><i>Challenges in Model Synchronization for Information Preservation</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| Illustrated with the FACE and AADL Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63                |

| A DESCRIPTION OF A | The second second |

### **Produced by Ada-Europe**

#### **Editor in Chief**

António Casimiro

University of Lisbon, Portugal AUJ Editor@Ada-Europe.org

#### Ada User Journal Editorial Board

Luís Miguel Pinho Associate Editor

Jorge Real Deputy Editor

**Patricia López Martínez** Assistant Editor

**Dirk Craeynest** *Events Editor*

Alejandro R. Mosteo News Editor Polytechnic Institute of Porto, Portugal *lmp@isep.ipp.pt*

Universitat Politècnica de València, Spain *jorge@disca.upv.es*

Universidad de Cantabria, Spain *lopezpa@unican.es*

KU Leuven, Belgium Dirk.Craeynest@cs.kuleuven.be

Centro Universitario de la Defensa, Zaragoza, Spain *amosteo@unizar.es*

#### **Ada-Europe Board**

**Tullio Vardanega** (President) University of Padua

**Dirk Craeynest** (Vice-President) Ada-Belgium & KU Leuven

**Dene Brown** (General Secretary) SysAda Limited

Ahlan Marriott (Treasurer) White Elephant GmbH

Luís Miguel Pinho (Ada User Journal) Polytechnic Institute of Porto

António Casimiro (Ada User Journal) University of Lisbon Belgium United Kingdom Switzerland Portugal Portugal

Italy

#### **Ada-Europe General Secretary**

Dene Brown SysAda Limited Signal Business Center 2 Innotec Drive BT19 7PD Bangor Northern Ireland, UK Tel: +44 2891 520 560 Email: Secretary@Ada-Europe.org URL: www.ada-europe.org

#### Information on Subscriptions and Advertisements

Ada User Journal (ISSN 1381-6551) is published in one volume of four issues. The Journal is provided free of charge to members of Ada-Europe. Library subscription details can be obtained direct from the Ada-Europe General Secretary (contact details above). Claims for missing issues will be honoured free of charge, if made within three months of the publication date for the issues. Mail order, subscription information and enquiries to the Ada-Europe General Secretary.

For details of advertisement rates please contact the Ada-Europe General Secretary (contact details above).

# ADA USER JOURNAL

# Volume 45 Number 1 March 2024

# Contents

|                                                                                                                                                                                                                | Page              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                                                                                          | 2                 |

| Editorial                                                                                                                                                                                                      | 3                 |

| Quarterly News Digest                                                                                                                                                                                          | 4                 |

| Conference Calendar                                                                                                                                                                                            | 17                |

| Forthcoming Events                                                                                                                                                                                             | 25                |

| Proceedings of the "ADEPT: AADL by its Practitioners Workshop" of AEiC 2023                                                                                                                                    |                   |

| H. N. Tran et al<br><i>"ADEPT 2023 Workshop Summary"</i><br>K. Bae, P. C. Ölveczky                                                                                                                             | 28                |

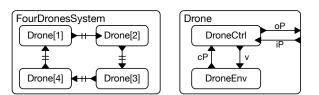

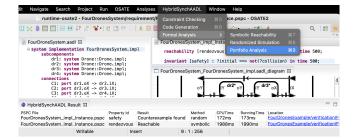

| K. Bae, P. C. Olveczky<br>"Formal Model Engineering of Synchronous CPS Designs in AADL"                                                                                                                        | 31                |

| B. R. Larson, E. Ahmad<br>"BLESS Behavior Correctness Proof as Convincing Verification Artifact"                                                                                                               | 35                |

| J. Hughes<br>"Mechanizing AADL in Coq – Extended Abstract"                                                                                                                                                     | 47                |

| <ul> <li>H. Valente, M. A. de Miguel, A. G. Pérez, A. Alonso, J. Zamorano, J. A. de la Pue<br/><i>"Extension of the TASTE Toolset to Support Publisher-Subscriber Communication</i><br/>L. Kosmidis</li> </ul> |                   |

| "METASAT's Model Based Design Solutions"                                                                                                                                                                       | 54                |

| R. Mittal, D. Blouin<br>"Facilitating AADL Model Processing and Analysis with OSATE-DIM"                                                                                                                       | 55                |

| P. Dissaux<br>"LAMP: to Shed Light on AADL Models"                                                                                                                                                             | 59                |

| D. Blouin, A. Bhobe, L. Pautet<br>"Challenges in Model Synchronization for Information Preservation Illustrated wi<br>FACE and AADL Standards"                                                                 | <i>ith the</i> 63 |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                                                                                      | 68                |

| Ada-Europe Sponsors                                                                                                                                                                                            | Inside Back Cover |

|                                                                                                                                                                                                                |                   |

# Editorial Policy for Ada User Journal

#### Publication

Ada User Journal — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

#### Aims

Ada User Journal aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at *www.ada-europe.org/auj*.

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at *www.ada-europe.org/auj*.

#### **Original Papers**

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

#### **Proceedings and Special Issues**

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

#### **News and Product Announcements**

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

#### **Reprinted Articles**

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

#### Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length – inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

#### **Announcements and Reports**

We are happy to publicise and report on events that may be of interest to our readers.

#### Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

#### **Submission Guidelines**

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

My initial words in this editorial, the first in 2024, are about the significant changes that are happening in our Ada ecosystem. I'm referring to the integration of SIGAda (the ACM Special Interest Group on Ada) in SIGPLAN (the SIG on Programming Languages). Despite this change, SIGAda's sister publication, Ada Letters, will continue to exist in online form and share content with the Ada User Journal. Therefore, we still hope that at some point, possibly by the end of 2024, it may be possible to entail conversations with the ACM on how and in which terms a single publication may come to life. As a side note, but also very importantly, a consequence of the extinction of SIGAda is that a new global association is being created, aiming to become a solid home base for Ada friends from all over the world. The plans, as explained in a letter from the Ada-Europe Board to all Ada-Europe members, are grounded on several principles. The one directly relevant to the AUJ is that, and I quote, "The merger of our Ada User Journal with Ada Letters into a single quarterly magazine, attributed to the new association and shared with Ada-Europe's membership base, should be swiftly finalized". I will probably come back to this topic in the next editorial.

Concerning the technical contents of this issue, it provides the Proceedings of the "ADEPT: AADL by its Practitioners Workshop" of AEiC 2023, which took place in Lisbon, Portugal, last June. It was the second edition of the workshop, and again a successful event. The proceedings include eight technical contributions and a summary paper prepared by the workshop organizers H. N. Tran and F. Singhoff from the University of Brest, in France, and J. Hugues from Carnegie Mellon University in the USA. The workshop features contributions that somehow explore or are related to the Architecture Analysis and Design Language (AADL), which is an SAE International Standard dedicated to the precise modelling of complex embedded systems, which allows, among other things, to perform reliability analysis of the modelled systems. The reader is invited to read the summary paper to get a complete perspective of the contents of these proceedings.

As usual, the issue includes the News Digest section prepared by Alejandro R. Mosteo and the Calendar and Events section prepared by Dirk Craeynest.

Antonio Casimiro Lisboa March 2024 Email: AUJ\_Editor@Ada-Europe.org

# Quarterly News Digest

4 4

8

9

9

#### Alejandro R. Mosteo

Centro Universitario de la Defensa de Zaragoza, 50090, Zaragoza, Spain; Instituto de Investigación en Ingeniería de Aragón, Mariano Esquillor s/n, 50018, Zaragoza, Spain; email: amosteo@unizar.es

#### Contents

[Messages without subject/newsgroups are replies from the same thread. Messages may have been edited for minor proofreading fixes. Quotations are trimmed where deemed too broad. Sender's signatures are omitted as a general rule. —arm]

# Preface by the News Editor

Dear Reader,

Once more, the flagship Ada conference is upon us [1], this year taking place in Barcelona, Spain. Furthermore, among its satellite activities is an "Ada Developers Workshop" [2] that aims to fill in for the sorely missed "Ada Developer Room" of FOSDEM past.

For lovers of Ada nitty-gritty details, this period includes a discussion of Container and Cursor semantics [3] with headbutting positions, so the reader can take sides (or hold their unopposed personal truth at home ;-)).

#### Sincerely,

Alejandro R. Mosteo.

- [1] "AEiC 2024 Ada-Europe Conference - Deadlines Approaching", in Adarelated Events.

- [2] "Ada Developer Workshop @ AEiC 2024, a New "FOSDEM DevRoom" for the Community", in Ada-related Events.

- [3] "Re: Map Iteration and Modification", in Ada Practice.

#### **Ada-related Events**

#### Ada-Europe Conference - 31 Jan Journal Track Extended Deadline

From: Dirk Craeynest

<dirk@orka.cs.kuleuven.be> Subject: Ada-Europe conference - 31 Jan Journal Track Extended Deadline Date: Mon, 8 Jan 2024 10:43:48 -0000 Newsgroups: comp.lang.ada, fr.comp.lang.ada, comp.lang.misc

UPDATED Call for Contributions

28th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2024)

11-14 June 2024, Barcelona, Spain

www.ada-europe.org/conference2024

\*\*\* Journal track deadline EXTENDED to 31 January 2024 \*\*\*

> \*\*\* Other submissions by 26 February 2024 \*\*\*

Organized by Ada-Europe and Barcelona Supercomputing Center (BSC), in cooperation with ACM SIGAda, ACM SIGBED, ACM SIGPLAN, and Ada Resource Association (ARA)

> #AEiC2024 #AdaEurope #AdaProgramming

#### General Information

The 28th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2024) will take place in Barcelona, Spain.

AEiC is a leading international forum for providers, practitioners, and researchers in reliable software technologies. The conference presentations will illustrate current work in the theory and practice of the design, development, and maintenance of long-lived, high-quality software systems for a challenging variety of application domains. The program will also include keynotes, Q&A and discussion sessions, and social events. Participants include practitioners and researchers from industry, academia, and government organizations active in the development of reliable software technologies.

The topics of interest for the conference include but are not limited to (more specific topics are described on the conference web page):

- \* Formal and Model-Based Engineering of Critical Systems;

- \* High-Integrity Systems and Reliability;

- \* AI for High-Integrity Systems Engineering;

- \* Real-Time Systems;

- \* Ada Language;

- \* Applications in Relevant Domains.

The conference comprises different tracks and co-located events:

- \* Journal track papers present research advances supported by solid theoretical foundation and thorough evaluation.

- \* Industrial track contributions highlight industrial open challenges and/or the practitioners' side of a relevant case study or industrial project.

- \* Work-in-progress track papers illustrate novel research ideas that are still at an initial stage, between conception and first prototype.

- \* Tutorials guide attenders through a hands-on familiarization with innovative developments or with useful features related to reliable software.

- \* Workshops provide discussion forums on themes related to the conference topics.

- \* Vendor presentations and exhibitions allow for companies to showcase their latest products and services.

#### Important Dates

31 January 2024 EXTENDED submission deadline for journal track papers

26 February 2024 Deadline for submission of industrial track papers, work-in-progress papers, tutorial and workshop proposals

22 March 2024 First round notification for journal track papers, and notification of acceptance for all other types of submissions

11-14 June 2024 Conference

Call for Journal Track Submissions

Following a journal-first model, this edition of the conference includes a journal track, which seeks original and

high-quality papers that describe mature research work on the conference topics. Accepted journal track papers will be published in a Special Issue of Elsevier JSA - the Journal of Systems Architecture (Q1 ranked, CiteScore 8.5, impact factor 4.5). Accordingly, the conference is listed as "Journal Published" in the latest update of the CORE Conference Ranking released in August 2023. Contributions must be submitted by 31 January 2024. Submissions should be made online at https://www.editorialmanager.com/jsa/, selecting the "Ada-Europe AEiC 2024" option (submission page open from 15 November 2023) as article type of the paper. General information for submitting to the JSA can be found at the Journal of Systems Architecture website.

JSA has adopted the Virtual Special Issue model to speed up the publication process, where Special Issue papers are published in regular issues, but marked as SI papers. Acceptance decisions are made on a rolling basis. Therefore, authors are encouraged to submit papers early, and need not wait until the submission deadline. Authors who have successfully passed the first round of review will be invited to present their work at the conference. The abstract of the accepted contributions will be included in the conference booklet.

The Ada-Europe organization will waive the Open Access fees for the first four accepted papers (whose authors do not already enjoy Open Access agreements). Subsequent papers will follow JSA regular publishing track. Prospective authors may direct all enquiries regarding this track to the corresponding chairs, Bjorn Andersson

(baandersson@sei.cmu.edu) and Luis Miguel Pinho (lmp@isep.ipp.pt).

#### Call for Industrial Track Submissions

The conference seeks industrial practitioner presentations that deliver insight on the challenges of developing reliable software. Especially welcome kinds of submissions are listed on the conference website. Given their applied nature, such contributions will be subject to a dedicated practitioner-peer review process. Interested authors shall submit a 1-to-2 pages abstract, by 26 February 2024, via EasyChair at https://easychair.org/my/conference?conf =aeic2024, selecting the "Industrial Track". The format for submission is strictly in PDF, following the Ada User Journal style. Templates are available at http://www.ada-europe.org/auj/guide.

The abstract of the accepted contributions will be included in the conference booklet. The corresponding authors will get a presentation slot in the prime-time technical program of the conference and will also be invited to expand their contributions into full-fledged articles for publication in the Ada User Journal, which will form the proceedings of the industrial track of the Conference. Prospective authors may direct all enquiries regarding this track to its chairs Luciana Provenzano (luciana.provenzano@mdu.se) and Michael Pressler (Michael.Pressler@de.bosch.com).

(Michael.Pressier@de.bosch.com).

#### Call for Work-in-Progress Track Submissions

The work-in-progress track seeks two kinds of submissions: (a) ongoing research and (b) early-stage ideas. Ongoing research submissions are 4-page papers describing research results that are not mature enough to be submitted to the journal track. Early-stage ideas are 1-page papers that pitch new research directions that fall within the scope of the conference. Both kinds of submissions must be original and shall undergo anonymous peer review. Submissions by recent MSc graduates and PhD students are especially sought. Authors shall submit their work by 26 February 2024, via EasyChair at https://easychair.org/my/conference?conf

eacic2024, selecting the "Work-in-Progress Track". The format for submission is strictly in PDF, following the Ada User Journal style. Templates are available at http://www.adaeurope.org/auj/guide.

The abstract of the accepted contributions will be included in the conference booklet. The corresponding authors will get a presentation slot in the prime-time technical program of the conference and will also be offered the opportunity to expand their contributions into 4-page articles for publication in the Ada User Journal, which will form the proceedings of the WiP track of the Conference. Prospective authors may direct all enquiries regarding this track to the corresponding chairs Alejandro R. Mosteo (amosteo@unizar.es) and Ruben Martins (rubenm@andrew.cmu.edu).

#### Awards

The organization will offer an honorary award for the best technical presentation, to be announced in the closing session of the conference.

#### Call for Tutorials

The conference seeks tutorials in the form of educational seminars on themes falling within the conference scope, with an academic or practitioner slant, including hands-on or practical elements. Tutorial proposals shall include a title, an abstract, a description of the topic, an outline of the presentation, the proposed duration (halfday or full-day), the intended level of the contents (introductory, intermediate, or advanced), and a statement motivating attendance. Tutorial proposals shall be submitted at any time but no later than the 26 February 2024 to the respective chair Maria A. Serrano

(maria.serrano@nearbycomputing.com), with subject line: "[AEiC 2024: tutorial proposal]". Once submitted, each tutorial proposal will be evaluated by the conference organizers as soon as possible, with decisions from January 1st. The authors of accepted full-day tutorials will receive a complimentary conference registration, halved for half-day tutorials. The Ada User Journal will offer space for the publication of summaries of the accepted tutorials.

#### Call for Workshops

The conference welcomes satellite workshops centred on themes that fall within the conference scope. Proposals may be submitted for half- or full-day events, to be scheduled at either end of the AEiC conference. Workshop organizers shall also commit to producing the proceedings of the event, for publication in the Ada User Journal. Workshop proposals shall be submitted at any time but no later than the 26 February 2024 to the respective chair Sergio Saez (ssaez@disca.upv.es), with subject line: "[AEiC 2024: workshop proposal]". Once submitted, each workshop proposal will be evaluated by the conference organizers as soon as possible, with decisions from January 1st.

#### Academic Listing

The Journal of Systems Architecture, publication venue of the journal track proceedings of the conference, is Q1 ranked, with CiteScore 8.5 and Impact Factor 4.5. The Ada User Journal, venue of all other technical proceedings of the conference, is indexed by Scopus and by EBSCOhost in the Academic Search Ultimate database.

#### Call for Exhibitors and Sponsors

The conference will include a vendor and technology exhibition with the option of a 20 minutes presentation as part of the conference program. Interested providers should direct inquiries to the Exhibition & Sponsorship Chair Ahlan Marriot (ahlan@ada-switzerland.ch).

#### Venue

The conference will take place in Barcelona, Spain. Barcelona is a major cultural, economic, and financial centre, known for its architecture, culture, and Mediterranean atmosphere, a hub for technology and innovation. There's plenty to see and visit in Barcelona, so plan in advance!

#### Organizing Committee

- Conference Chair

Sara Royuela, Barcelona Supercomputing Center, Spain sara.royuela@bsc.es - Journal Track Chairs Bjorn Andersson, Carnegie Mellon University, USA baandersson@sei.cmu.edu Luis Miguel Pinho, ISEP & INESC TEC,

Portugal lmp@isep.ipp.pt

- Industrial Track Chairs

Luciana Provenzano, Mälardalen University, Sweden luciana.provenzano@mdu.se

Michael Pressler, Robert Bosch GmbH, Germany Michael.Pressler@de.bosch.com

- Work-In-Progress Track Chairs Alejandro R. Mosteo, CUD Zaragoza,

Spain amosteo@unizar.es

Ruben Martins, Carnegie Mellon University, USA rubenm@andrew.cmu.edu

- Tutorial Chair

Maria A. Serrano, NearbyComputing, Spain maria.serrano@nearbycomputing.com

- Workshop Chair

Sergio Saez, Universitat Politècnica de València, Spain ssaez@disca.upv.es

- Exhibition & Sponsorship Chair

Ahlan Marriott, White Elephant GmbH, Switzerland ahlan@Ada-Switzerland.ch

- Publicity Chair

Dirk Craeynest, Ada-Belgium & KU Leuven, Belgium Dirk.Craeynest@cs.kuleuven.be

- Webmaster Hai Nam Tran, University of Brest, France hai-nam.tran@univ-brest.fr

- Local Chair

Nuria Sirvent, Barcelona Supercomputing Center, Spain nuria.sirvent@bsc.es

Journal Track Committee

Al Mok, University of Texas at Austin, USA

Alejandro Mosteo, CUD Zaragoza, Spain Alwyn Godloe, NASA, USA

António Casimiro, University of Lisbon,

Portugal Barbara Gallina, Mälardalen University, Sweden

Bernd Burgstaller, Yonsei University, South Korea

C. Michael Holloway, NASA, USA

Cristina Seceleanu, Mälardalen University, Sweden Doug Schmidt, Vanderbilt University, USA Frank Singhoff, University of Brest, FR George Lima, Universidade Federal da Bahia, Brazil Isaac Amundson, Rockwell Collins, USA Jérôme Hugues, CMU/SEI, USA José Cruz, Lockeed Martin, USA Kristoffer Nyborg Gregertsen, SINTEF Digital, Norway Laurent Pautet, Telecom ParisTech, France Leonidas Kosmidis, Barcelona Supercomputing Center, Spain Mario Aldea Rivas, University of Cantabria, Spain Matthias Becker, KTH - Royal Institute of Technology, Sweden Patricia López Martínez, University of Cantabria, Spain Sara Royuela, Barcelona Supercomputing Center, Spain Sergio Sáez, Universitat Politècnica de València, Spain Tucker Taft, AdaCore, USA Tullio Vardanega, University of Padua, Italy Xiaotian Dai, University of York, England Industrial Track Committee Aida Causevic, Alstom, Sweden Alexander Viehl, Research Center for Information Technology, Germany Ana Rodríguez, Silver Atena, Spain Aurora Agar, NATO, Netherlands Behnaz Pourmohseni, Robert Bosch GmbH, Germany Claire Dross, AdaCore, France Elena Lisova, Volvo CE, Sweden Enricco Mezzeti, Barcelona Supercomputing Center, Spain Federico Aromolo, Scuola Superiore Sant'Anna, Italy Helder Silva, Edisoft, Portugal Hugo Torres Vieira, Evidence Srl, Italy Irune Agirre, Ikerlan, Spain Jordi Cardona, Rapita Systems, Spain José Ruiz, AdaCore, France Joyce Tokar, Raytheon, USA

Luciana Alvite, Alstom, Germany Marco Panunzio, Thales Alenia Space, France

Patricia Balbastre Betoret, Valencia Polytechnic University, Spain Philippe Waroquiers, Eurocontrol NMD, Belgium

Raúl de la Cruz, Collins Aerospace, Ireland

Santiago Urueña, GMV, Spain Stef Van Vlierberghe, Eurocontrol NMD, Belgium

Work-in-Progress Track Committee Alan Oliveira, University of Lisbon, Portugal

J. Javier Gutiérrez, University of Cantabria, Spain

Jérémie Guiochet, LAAS-CNRS, France

Kalinka Branco, University of São Paulo, Brazil

Katherine Kosaian, University of Iowa, USA

Kevin Cheang, AWS, USA

Kristin Yvonne Rozier, Iowa State University, USA

Leandro Buss Becker, University of Manchester, UK

Li-Pin Chang, National Yang Ming Chiao Tung University, Taiwan

Mathias Preiner, Stanford University, USA

Raffaele Romagnoli, Carnegie Mellon University, USA

Robert Kaiser, RheinMain University of Applied Sciences, Germany

Sara Abbaspour, Mälardalen University, Sweden

Sergi Alcaide, Barcelona Supercomputing Center, Spain

Simona Bernardi, Unizar, Spain

Stefan Mitsch, School of Computing at DePaul University, USA

Teresa Lázaro, Aragon's Institute of Technology, Spain

Tiago Carvalho, ISEP, Portugal

Yannick Moy, AdaCore, France

#### Previous Editions

Ada-Europe organizes annual international conferences since the early 80's. This is the 28th event in the Reliable Software Technologies series, previous ones being held at Montreux, Switzerland ('96), London, UK ('97), Uppsala, Sweden ('98), Santander, Spain ('99), Potsdam, Germany ('00), Leuven, Belgium ('01), Vienna, Austria ('02), Toulouse, France ('03), Palma de Mallorca, Spain ('04), York, UK ('05), Porto, Portugal ('06), Geneva, Switzerland ('07), Venice, Italy ('08), Brest, France ('09), Valencia, Spain ('10), Edinburgh, UK ('11), Stockholm, Sweden ('12), Berlin, Germany ('13), Paris, France ('14), Madrid, Spain ('15), Pisa, Italy ('16), Vienna, Austria ('17), Lisbon, Portugal ('18), Warsaw, Poland ('19), online from Santander, Spain ('21),

Ghent, Belgium ('22), and Lisbon, Portugal ('23).

Information on previous editions of the conference can be found at www.adaeurope.org/confs/ae.

Our apologies if you receive multiple copies of this announcement.

Please circulate widely.

Dirk Craeynest, AEiC 2024 Publicity Chair

Dirk.Craeynest@cs.kuleuven.be

\* 28th Ada-Europe Int. Conf. Reliable Software Technologies (AEiC 2024)

\* June 11-14, 2024, Barcelona, Spain, www.ada-europe.org/conference2024

(V4.1)

#### AEiC 2024 - Ada-Europe Conference - Deadlines Approaching

From: Dirk Craeynest <dirk@orka.cs.kuleuven.be> Subject: AEiC 2024 - Ada-Europe conference - Deadlines Approaching Date: Fri, 16 Feb 2024 19:07:10 -0000 Newsgroups: comp.lang.ada, fr.comp.lang.ada,comp.lang.misc

UPDATED Call for Contributions -Additional Tracks

28th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2024)

11-14 June 2024, Barcelona, Spain

\*\*\* DEADLINES approaching: 26 February and 4 March 2024 \*\*\*

www.ada-europe.org/conference2024

\*\*\* Submission DEADLINE 26 February 2024 \*\*\*

Workshops: submit to Workshop Chair, Sergio Saez ssaez@disca.upv.es subject "[AEiC 2024: workshop proposal]"

Tutorials: submit to Tutorial and Education Chair, Maria A. Serrano maria.serrano@nearbycomputing.com subject "[AEiC 2024: tutorial proposal]"

\*\*\* EXTENDED submission DEADLINE 4 March 2024 \*\*\*

Industrial- and Work-in-Progress-track: submit via https://easychair.org/my/ conference?conf=aeic2024 select "Industrial Track" or "Work in Progress Track"

For more information please see the full Call for Papers at www.ada-europe.org/ conference2024/cfp.html Organized by Ada-Europe and Barcelona Supercomputing Center (BSC), in cooperation with ACM SIGAda, ACM SIGBED, ACM SIGPLAN, and Ada Resource Association (ARA)

> #AEiC2024 #AdaEurope #AdaProgramming

Our apologies if you receive multiple copies of this announcement.

Please circulate widely.

Dirk Craeynest, AEiC 2024 Publicity Chair

Dirk.Craeynest@cs.kuleuven.be

\* 28th Ada-Europe Int. Conf. Reliable Software Technologies (AEiC 2024)

\* June 11-14, 2024, Barcelona, Spain, www.ada-europe.org/conference2024

(V6.1)

#### Ada Developer Workshop @ AEiC 2024, a New "FOSDEM DevRoom" for the Community

From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz> Subject: Ada Developer Workshop @ AEiC 2024, a new "FOSDEM DevRoom" for the community Date: Sat, 24 Feb 2024 22:30:03 +0100

Newsgroups: comp.lang.ada

Dear Ada community,

I come with great news! For the past two years, there was no Ada DevRoom over @ FOSDEM, a place where the Ada community used to meet and share their work and projects. Some of us wanted to keep having such experience as we believed it to be a greatly beneficial aspect to the wider Ada community.

For this reason, Fabien Chouteau, Dirk Craeynest and Fernando Oleo Blanco, made a proposal to the Ada-Europe International Conference on Reliable Software Technologies (AEiC 2024 aka Ada-Europe 2024) in order to have a "devroom" for the wider Ada community, just like in FOSDEM.

We were accepted and you can already find all the information over at the Ada Developer Workshop webpage [1]!

I would encourage everybody to take a look at it! Nonetheless, here is a quick summary highlighting some of the points:

- It will take place on Friday, 14th of June in Barcelona. Friday was chosen in order to minimise the amount of free days/holidays that we would need to take off from our jobs and allow us to then use the weekend to visit and enjoy Barcelona.

- The cost will be lower than for the main conference. Our goal is to make it completely free, just like FOSDEM, but this is still a Work-In-Progress (WIP).

- The nature of the event is similar to any past DevRoom that took place @ FOSDEM. The main difference is that now, being an open-source project will not be a requirement.

- March 31st, 2024 is the (current) deadline for submissions. If you would like to present your work or discuss topics, please, please please, keep this date in mind!

We are eager to hear from all of you. And if you have any questions, please, let us know!

[1] https://www.ada-europe.org/ conference2024/adadev.html

From: Streaksu <streaksu@mailbox.org> Date: Tue, 27 Feb 2024 06:51:03 +0100

That sounds amazing! Thank you so much for your work and to the people at AEiC for making it happen.

> The cost will be lower than for the main conference.

That would be a huge deal. I have not checked this edition's registrations, but if 2023's are anything to go by, as a hobbyist Ada developer, I don't think I can justify it for myself. But a cheaper event would be a great alternative. Please do keep us updated!

From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz> Date: Fri, 22 Mar 2024 19:18:04 +0100

Hi Ada community!

This is a kind reminder that you can still submit any talks to the Ada Developer Workshop that will take place during the

AEiC 2024, on the 14th of June in

Barcelona! Entry prices should be published shortly in the AEiC website. Nonetheless, we are still looking for some sponsorships :)

For more information see http://www.ada-europe.org/ conference2024/adadev.html or email any of the organisers (Fabien, Dirk and Fernando).

From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz> Date: Mon, 25 Mar 2024 23:18:42 +0100

Great news everybody! This was posted by Dirk on the Ada-Lang forum.

Hot news! Thanks to AdaCore sponsoring the Ada Developer Workshop in Barcelona, the early registration fee for in-person participation will be only 10 EUR, including lunch and coffee breaks.

That's as low-cost as attending an Ada Developer Room at FOSDEM in

Brussels, as you easily spend 10 EUR on food and drinks there...;)

Registration info, for the conference, tutorials, workshops, social events, will shortly be added to the conference website at Ada-Europe 2024 [1].

Hope to see many of you there!

And remember, submissions are still welcome!

[1] http://www.ada-europe.org/ conference2024/

#### Ada Monthly Meetup 2024

From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz> Subject: Ada Monthly Meetup 2024 Date: Sun, 3 Mar 2024 20:31:05 +0100 Newsgroups: comp.lang.ada

Dear all, this is just a quick reminder that the next Ada Monthly Meetup will take place on Saturday 9th of March!

No topics were proposed for this meetup. Nonetheless, I will take the opportunity to talk a bit about FOSDEM (and WolfSSL), the newly proposed Ada Developer Workshop during AEiC, remind people about the newly released Alire v2.0-RC1 and a few other topics if we have time.

From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz> Date: Sun, 17 Mar 2024 10:10:26 +0100

Hello everybody!

I would like to announce the April (2024) Ada Monthly Meetup which will be taking place on the 6th of April at \*\*13:00 UTC time (15:00 CEST)\*\*. As always the meetup will take place over at Jitsi. The Meetup will also be livestreamed to Youtube.

If someone would like to propose a talk or a topic, feel free to do so! We currently have no topics :wink:

Though I will try to focus more on Ada and I would like to bring people's attention to [Tsoding's Ada livestreams] (https://forum.ada-lang.io/t/ making-a-game-in-ada-with-raylib/704).

Here are the connection details from previous posts: The meetup will take place over at Jitsi, a conferencing software that runs on any modern browser. The link is [Jitsi Meet] (https://meet.jit.si/AdaMonthlyMeetup) The room name is "AdaMonthlyMeetup" and in case it asks for a password, it will be set to "AdaRules".

I do not want to set up a password, but in case it is needed, it will be the one above without the quotes. The room name is generally not needed as the link should take you directly there, but I want to write it down just in case someone needs it.

Best regards and see you soon! Fer

P.S: it is that time of year when clocks have their time changed. So please, take a look at whether this affects you. (Central) Europe will now go from CET to CEST, so +2h. USA and related countries already had their time changed last week.

#### Ada-related Resources

[Delta counts are from February 19th to May 28th. —arm]

#### Ada on Social Media

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Ada on Social Media Date: 28 May 2024 13:23 CET To: Ada User Journal readership

Ada groups on various social media:

- Reddit: \_705 (+144) members

- LinkedIn: 3\_509 (+30) members

- Stack Overflow: 2\_405 (+12) questions

- Gitter: 253 (+10) people

- Ada-lang.io: 219 (+37) users

- Telegram: 201 (+28) users

- Libera.Chat: 75 (-1) concurrent users [7]

- [1] http://old.reddit.com/r/ada/ [2] https://www.linkedin.com/

- groups/114211/

- [3] http://stackoverflow.com/questions/ tagged/ada

- [4] https://app.gitter.im/#/room/ #ada-lang\_Lobby:gitter.im

- [5] https://forum.ada-lang.io/u

- [6] https://t.me/ada\_lang

- [7] https://netsplit.de/channels/details.php ?room=%23ada&net=Libera.Chat

#### **Repositories of Open Source** Software

From: Alejandro R. Mosteo <amosteo@unizar.es> Subject: Repositories of Open Source software Date: 28 May 2024 13:33 CET To: Ada User Journal readership GitHub: >1\_000\* (=) developers

Rosetta Code: 950 (+10) examples [2]

42 (+4) developers

- 1\_048 (new) releases

- Sourceforge: 251 (+3) projects

- Open Hub: 214 (=) projects

- Codelabs: 57 (=) repositories

- Bitbucket: 38 (+1) repositories

\*This number is a lower bound due to GitHub search limitations.

- [1] https://github.com/search? q=language%3AAda&type=Users

- [2] https://rosettacode.org/wiki/ Category:Ada

- [3] https://rosettacode.org/wiki/ Category:Ada\_User

- [4] https://alire.ada.dev/crates.html

- [5] `alr search --list --full`

- [6] https://sourceforge.net/directory/ language:ada/

- [7] https://www.openhub.net/ tags?names=ada

- [8] https://git.codelabs.ch/? a=project\_index

- [9] https://bitbucket.org/repo/all? name=ada&language=ada

#### Language Popularity **Rankings**

From: Alejandro R. Mosteo

[1]

[2]

[3]

[4]

[5]

[6]

[1]

[3]

[4]

[5]

[6]

[7]

[9]

- <amosteo@unizar.es> Subject: Ada in language popularity

- rankings Date: 28 Feb 2024 13:43 CET

- To: Ada User Journal readership

[Positive ranking changes mean to go up in the ranking. —arm]

[1]

- TIOBE Index: 22 (+3) 0.83% (+0.06%)

- PYPL Index: 19 (-4) 0.82% 1.08% [2] (-0.26%)

- Languish Trends: 180 (new) 0.01% [3]

- Stack Overflow Survey: 42 (=) 0.77% (=)[4]

- IEEE Spectrum (general): 36 (=) Score: 0.0107 (=) [5]

- IEEE Spectrum (jobs): 29 (=) Score: 0.0173 (=) [5]

- IEEE Spectrum (trending): 30 (=) Score: 0.0122 (=) [5]

- [1] https://www.tiobe.com/tiobe-index/

[2] http://pypl.github.io/PYPL.html

- [3] https://tjpalmer.github.io/languish/

- [4] https://survey.stackoverflow.co/2023/

- [5] https://spectrum.ieee.org/topprogramming-languages/

#### Certificate Error Accessing Adapower.com

- From: Juanmiuk <juanmiuk@gmail.com> Subject: Certificate Security Error when. access adapower.com

- Date: Wed, 24 Jan 2024 05:30:39 -0800 Newsgroups: comp.lang.ada

- [8] When I tried to access adapower.com

- from the last version of Chrome and

Alire: 405 (+12) crates

NordVPN VPN the browser shows me this error:

Your connection isn't private. The web page you are trying to enter is not certified by a known certifying authority. Attackers might be trying to steal your information (for example, passwords, messages, or credit cards).

This error did not happen with Safari or Microsoft Edge (last version)

#### What's going on?

From: Stéphane Rivière <stef@genesix.org> Date: Wed, 24 Jan 2024 16:11:42 +0100

Simply no TLS certificates (see the padlock status before the URL)

This site is in ruins, out of date and should no longer exist.

What's more, a Google search turns up some dubious links.

#### Ada-related Tools NeoVim Plugin to Publish

### Alire Packages

From: Tama Mcglinn

<t.mcglinn@gmail.com> Subject: NeoVim plugin to publish Alire packages

Date: Sat, 17 Feb 2024 00:01:47 -0800 Newsgroups: comp.lang.ada

In case there's any NeoVim users who also publish Alire packages, I wrote a plugin for that;

https://github.com/

TamaMcGlinn/nvim-alire-tools

allows you to bind or call `:AlirePublish` which handles everything for your Alire toml file, and intelligently sees where you are in the version publishing process.

#### Aunit.Checks

From: Simon Wright <simon@pushface.org> Subject: AUnit.Checks Date: Sun, 24 Mar 2024 09:19:38 +0000 Newsgroups: comp.lang.ada

Has anyone come across this package? AFAICT it doesn't appear in the AUnit repo on Github.

Even the spec would be invaluable!

From: Simon Wright <simon@pushface.org> Date: Sun, 24 Mar 2024 11:17:06 +0000

Cancel that! It's in Stephe Leake's AUnit extensions, encountered in ada-mode.

#### Ada Practice

#### **Re: Map Iteration and Modification**

[Continues from AUJ 44-4, December 2023. The discussion initially addressed how to modify a container during iteration, to later move onto iteration semantics. —arm]

From: G.B.

<bauhaus@notmyhomepage.invalid><br/>Subject: Re: Map iteration and modification<br/>Date: Mon, 1 Jan 2024 20:27:51 +0100<br/>Newsgroups: comp.lang.ada

- >> Suppose that there is a way of orderly proceeding from one item to the next. It is probably known to the implementation of map. Do single steps guarantee transitivity, though, so that an algorithm can assume the order to be invariable?

- > An insane implementation can expose random orders each time.

An implementation order should then not be exposed, right? What portable benefits would there be when another interface is added to that of map, i.e., to Ada containers for general use? Would it not be possible to get these benefits using a different approach? I think the use case is clearly stated:

First, find Cursors in map  $=: C^*$ .

Right after that, Delete from map all nodes referred to by C\*.

> Unless removing element invalidates all cursors. Look, insanity has no bounds. Cursors AKA pointers are as volatile as positions in certain implementations. Consider a garbage collector running after removing a pair and shuffling remaining pairs in memory.

> [...]

> you assume that cursors are ordered and the order is preserved from call to call. [...]

Yes, given the descriptions of Ordered\_Maps, so long as there is no tampering, a Cursor will respect an order. Likely the one that the programmer has in mind.

[...]

From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de> Date: Mon, 1 Jan 2024 21:55:12 +0100

> An implementation order should then not be exposed, right?

IMO, an order should be exposed. Not necessarily the "implementation order" whatever that might mean.

From: Randy Brukardt <randy@rrsoftware.com> Date: Tue, 2 Jan 2024 21:15:01 -0600

- >> There is no "natural" order to the key/element pairs; they are effectively unordered.

- > Iteration = order. It is the same thing. If you provide iteration of pairs in the mapping by doing so you provide an order of.

Certainly not. An iteration presents all of the elements in a container, but there is no requirement that there is an order. Indeed, logically, all of the elements are presented at the same time (and parallel iteration provides an approximation of that).

If you try to enforce an order on things that don't require it, you end up preventing useful parallelism (practically, at least, no one has succeeded at providing useful parallelism to sequential code and people have been trying for about 50 years -- they were trying when I was a university student in the late 1970s).

- >> [...] Certainly, no concept of "forward" or "reverse" applies to such an ordering (nor any stability requirement).

- > It does. You have a strict total order of pairs which guarantees existence of previous and next pairs according to.

Again, this is unrelated. Iteration can usefully occur in unordered containers (that is, "foreach"). Ordering is a separate concept, not always needed (certainly not in basic structures like maps, sets, and bags).

[...]

Ada requires that cursors continue to designate the same element through all operations other than deletion of the element or movement to a different container. Specific containers have additional invariants, but this is the most general one. No other requirement is needed in many cases.

> Yes, position is a property of enumeration.

Surely not. This is a basis for my disagreement with you here. The only requirement for enumeration is that all elements are produced. The order is an artifact of doing an inherently parallel operation sequentially. We don't care about or depend on artifacts.

- >> You have some problem with an iterator interface as opposed to an array interface??

- > Yes, I am against pointers (referential semantics) in general.

This is nonsense - virtually everything is referential semantics (other than components). Array indexes are just a

<sup>[...]</sup>