# 21st International Conference on RELIABLE SOFTWARE TECHNOLOGIES

# **ADA-EUROPE 2016**

13-17 June 2016, Pisa, Italy

# **ADVANCE PROGRAM**

http://www.ada-europe.org/conference2016

In cooperation with

### **PRESENTATION**

In 2016, the 21st International Conference on Reliable Software Technologies takes place in Pisa, Italy, from 13 to 17 of June. The conference is the latest in a series of annual international conferences started in the early 80's, under the auspices of Ada-Europe, the international organization that promotes knowledge and use of Ada and Reliable Software in general.

The conference offers an international forum for researchers, developers and users of reliable software technologies. Presentations cover applied and theoretical work conducted to support the development and maintenance of reliable software systems. The conference program includes three keynote talks, a three-day technical program of refereed papers, two sessions with industrial presentations, one special session on Ada and Parallelism, an industrial

exhibition and two days of tutorials. The program of

the conference is complemented with posters and presentations from projects and initiatives and from students of the "ITS EASY Post Graduate School", co-located with the conference. Also co-located with the conference, the program includes on Friday the 3<sup>rd</sup> satellite workshop on "Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering".

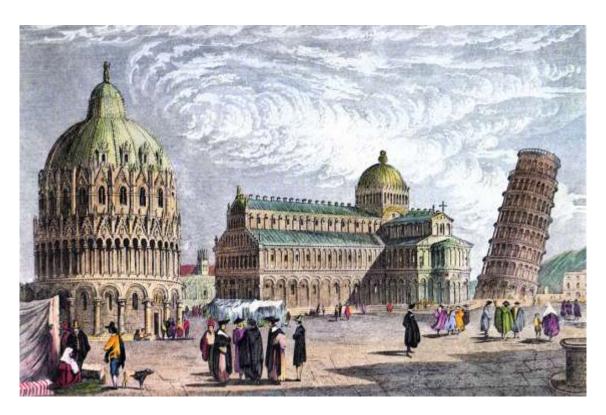

Pisa is located in Tuscany, close to the coast and just 80 km from Florence. It is a university city with a population of nearly 100,000. Once a Marine Republic, Pisa stretches along the shores of the Arno River, and occupies a place of honour amongst the most exclusive of art cities. Its glorious past offers authentic wonders to the tourist, and there is a lot more to see than just the leaning Tower, its most popular monument.

Ada-Europe 2016 provides a unique opportunity for dialogue and collaboration between academics and industrial practitioners interested in reliable software.

# OVERVIEW OF THE WEEK

|                                                        | Morning                                                                                      | Late Morning                               | After Lunch                                                                    | Afternoon                               |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------|

| Monday                                                 | W. Bail A Semi-formal Approach to Software Development                                       |                                            | W. Bail<br>Software Test and Verification Techniques for<br>Dependable Systems |                                         |

| Monday<br>June 13th<br>Tutorials                       | P. Rogers  Embedded ARM Programming with Ada 2012                                            |                                            |                                                                                |                                         |

|                                                        | J. Sparre-Andersen  Ada 2012 (Sub)types and Subprogram Contracts in  Practice                |                                            | J. Lelli<br>Towards Energy Awareness and Predictability in the<br>Linux Kernel |                                         |

| Tuesday<br>June 14th<br>Sessions &<br>Exhibition       | Keynote Talk: Alan Burns (University of York, UK)                                            | Regular Session  Concurrency & Parallelism | Vendor Session                                                                 | Special Session  Ada & Parallelism      |

| Wednesday<br>June 15th<br>Sessions &<br>Exhibition     | Keynote Talk:<br>Valerio Giorgetta<br>(Magneti Marelli, Italy)                               | Industrial Session  Uses of Ada            | Presentations Session                                                          | Regular Session  Testing & Verification |

| Thursday June 16th Sessions & Exhibition               | Keynote Talk:<br>Marc Duranton<br>(CEA, France)                                              | Industrial Session  Reliable Software      | Regular Session  Program Correctness & Robustness                              | Regular Session  Real-Time Systems      |

| Friday                                                 | J.P. Rosen Access Types and Memory Management in Ada 2012                                    |                                            | J.P. Rosen<br>Using Gnoga for Desktop/Mobile GUI and Web<br>development in Ada |                                         |

| <b>June 17<sup>th</sup></b><br>Tutorials &<br>Workshop | B. Moore, S. Michell Parallelism in Ada, C, Java and C#, Today and Tomorrow                  |                                            |                                                                                |                                         |

|                                                        | Workshop Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering |                                            |                                                                                |                                         |

The information in this document is still preliminary - please refer to the conference website for the latest details.

### KEYNOTE SPEAKERS

Why the Expressive Power of Languages such as Ada is needed for Future Cyber Physical Systems

Alan Burns University of York, UK

(Tuesday 14th)

If Cyber Physical Systems (CPS) are to be built with efficient resource utilisation it is imperative that they exploit the wealth of scheduling theory available.

Many forms of real-time scheduling, and its associated analysis, are applicable to CPS, but it is not clear how the system developer/programmer can gain access to this theory when real CPS are being constructed. The aim of the presentation is to show that Ada provides most of the programming abstractions needed to deliver future CPS.

#### Presenter

Professor Alan Burns is a member of the Department of Computer Science, University of York, U.K. His research interests cover a number of aspects of real-time systems including the assessment of languages for use in the real-time domain, distributed operating systems, the formal specification of scheduling algorithms and implementation strategies, and the design of dependable user interfaces to real-time applications. Professor Burns has authored/co-authored over 500 papers/reports and books. Most of these are in the real-time area. His teaching activities include courses in Operating Systems and Real-time Systems. In 2009 Professor Burns was elected a Fellow of the Royal Academy of Engineering. In 2012 he was elected a Fellow of the IEEE.

# Challenges for the Automotive Platform of the Future

Valerio Giorgetta Magneti Marelli, Italy

(Wednesday 15th)

This talk will describe what a vehicle once was, and what it will be in the future. From the point of view as Tierl, we will show how the same concept of "car" will be impacted by those technologies currently in development, like introduction of increasingly invasive ADAS (advanced driver assistance systems); the strong drive to realise autonomous vehicles; the growing focus on Functional Safety and Reliability; increasing availability and affordability of low-power high-performance computing also in automotive; integration of many more functions in single, more powerful, general-purpose ECUs; the trend towards distributed development; the needs of SW reusability and portability. All these topics will have to be considered in the future evolution of the current, universally-accepted automotive platform: AUTOSAR.

#### The HiPEAC Vision

Marc Duranton, CEA, France

(Thursday 16th)

The HiPEAC vision is a biannual document produced by the European Network on High Performance and Embedded Architecture and

Compilation (HiPEAC). It presents the upcoming challenges in computing systems. The last release presents its recommendations for Horizon 2020 based on an analysis of market trends, a discussion of technology constraints and opportunities, and a review of Europe's strengths and weaknesses in the field of computing systems. The HiPEAC roadmap calls particular attention to the EU's position as it poises to enter a new phase of scientific innovation. The vision document is the result a wide consultation among the 1500 members of the HiPEAC network.

#### Presenter

Dr. Marc Duranton is a senior member of a department common to Leti and List, both part of the Research and Technology Department of CEA (French Atomic Energy Commission). He previously spent more than 23 years in Philips, Philips Semiconductors and NXP Semiconductors. He has two MSc degrees, in electrical engineering and in computer science, from ENSERG and from ENSIMAG, both in Grenoble and a PhD in signal

and image processing from Institut National Polytechnique de Grenoble. He is currently working on projects related to IoT and High Performance Computing, and on architectures for Neural Network. He worked within Philips Semiconductors in California on several video coprocessors for the VLIW processor TriMedia and for various Nexperia platforms. His research interests include parallel and

high performance architectures for real-time processing, domain specific architectures, accelerators for Neural-Network models of computation, compiler technology and emerging paradigms for computing systems. He has published several articles and book chapters, and more than 30 patents. He is in charge of the roadmap activity in the HiPEAC Network of Excellence.

### **SPECIAL SESSION**

### **Ada and Parallelism**

(Tuesday 14th)

Moderator: Jeff Cousins (BAE Systems, UK, and ARG rapporteur)

#### **Presentations:**

- Brad Moore (Gran Dynamics, Canada): Paraffin: A parallelism library for Ada

- S. Tucker Taft (AdaCore, USA): Ada Container Iterators for Parallelism and Map/Reduce

Followed by open floor discussion

Ada has been a language which has always excelled with its advanced high-level concurrency support. In the last 20 years, Ada has steadily extended its wealth of concurrency features and capabilities to a considerable extent, yet within the bounds of a sequential task reasoning. With the advances in processor, and in particular the move into a parallel world, it is time to discuss how Ada should be evolved into supporting in the language the notion of fine-grained parallelism. The session will include presentations by two Ada experts, followed by a general discussion on the evolution of the language.

# Proven Test Solutions for Ada Development

### **TUTORIALS**

# T1 - A Semi-formal Approach to Software Development

William Bail, The MITRE Corporation

(Monday June 13th, morning)

This tutorial will describe an approach to software development that is strongly

based in theory but that allows construction without the need to fully apply the theory - the "hidden guiding hand". It starts with an overview of the history and experience of various development techniques, emphasizing previous formal approaches. It then describes the core activities, starting with requirements development using the enumeration technique. Based on the requirements, the design and code are generated, driven by the underlying theory (Kleene's Theorem). Subsequently, the resulting state machines are transformed into predefined code templates, resulting in the code that conforms to the requirements. Each step is accompanied with a proof of consistency, ensuring that the semantics of the requirements are preserved. Finally, the resulting code is verified using autogenerated test cases defined in accordance with the expected operational profiles to be applied to the system once placed into service.

#### Level

Intermediate. The target audience are those who are responsible for verifying systems at various levels, including testing as well as quality control. Target audience also includes those who are managing such activities.

#### Reasons for attending

This tutorial will provide the attendee with the basic understanding of an effective semi-formal development technique. The perspective gained can be directly applied to development efforts that are not necessarily using formal techniques, resulting in a higher quality product and a more predictable development experience.

#### Presenter

Since 1990, Dr. Bail has worked for The MITRE Corporation in McLean VA as a Computer Scientist in the Software Engineering Center (SWEC). MITRE is a not-for-profit corporation chartered to provide

systems engineering services to the U.S. Government agencies, primarily the DoD, the FAA, and the IRS. Within MITRE, the SWEC focuses on supporting various programs with consultation, particularly transitioning emerging technologies into practice. Dr. Bail's technical areas of focus include dependable software design and assessment, error handling policies, techniques for software specification development, design methodologies, metric definition and application, and verification and validation. Prior to 1990, Dr. Bail worked at Intermetrics Inc. in Bethesda MD. From 1989 to 2011, he served as a part-time Adjunct Professor at the University of Maryland University College where he develops instructional materials and teaches courses in software engineering, in topics such as Software Requirements, Verification and Validation, Software Software Engineering, Tolerant Design, Fault Software, and others. Previously, Dr. Bail taught part-time at The University of Maryland from 1983-1986 in the Computer Science Department for undergraduate courses in discrete mathematics, computer architecture, and programming language theory. Dr. Bail has presented tutorials on Cleanroom Software Engineering, Semi-Formal Development Techniques, Statistical Testing, and Requirements Engineering for Dependable Systems at SIGAda, Ada-Europe, NDIA Systems Engineering Conference, and other conferences. Dr. Bail received a BS in Mathematics from Carnegie Institute of Technology, and an MS and Ph.D. in Computer Science from the University of Maryland.

# **T2 - Software Test and Verification Techniques** for Dependable Systems

# William Bail, The MITRE Corporation

(Monday June 13th, afternoon)

The practice of testing is a key aspect of any software development effort, and is tightly intertwined with the construction of the software. In this tutorial we examine the nature of testing as applied to software systems with high expectations of dependability, and present techniques that have been shown to increase quality and dependability. We emphasize that test as a form of verification is more than just a "testing" activity, and includes practices that include testing as well as other valuable techniques, such as reviews,

inspections, and audits. We describe these practices, point out their individual strengths and weaknesses, and provide advice on how to select the appropriate practices based on the nature of the system under development. A key aspect of this selection process is correlating the techniques to the different types of requirements, recognizing that the requirements define the desired attributes of the system. We describe some challenges in applying test, and describe how to approach these challenges to improve the results.

#### Level

Intermediate. The target audience are those who are responsible for verifying systems at various levels, including testing as well as quality control. Target audience also includes are those who are managing such activities.

#### Reasons for attending

This tutorial will provide the attendee with the basic understanding of different test techniques, and advice on how to select and apply them based on the system to be developed. This information will assist in planning for complex systems development by providing a framework of test practices that will balance cost efficiency with the need to demonstrate that systems are able to deliver their required high levels of dependability.

T3 - Embedded ARM Programming with Ada 2012

Patrick Rogers, AdaCore (Monday 13th, full day)

We present both a tutorial and a developer workshop based on the tutorial

material. The workshop will constitute approximately half of the total time.

The tutorial covers the use of Ada in programming embedded systems. We focus on the facilities provided to developers for use at the application level. Hence there are four major sections: the language facilities for embedded systems programming, exploration of selected application-level packages and pragmas defined in the Real-Time Annex for applications with hard deadlines, an overview of the Ravenscar Profile, and the workshop itself. The focus is on the rationale and expected usage of the facilities, with extensive examples.

The developer workshop allows the student to put some of the material learned in the tutorial section into practice using an ARM-based embedded target platform providing a Ravenscar-compliant run-time environment. AdaCore will provide an Ada 2012 toolchain and several ARM-based target boards. Students may keep both the tools and ARM board at the end of the day, if they wish. (Students must provide their own computers having at least one USB port and the ability to run Windows or Linux. Instructions will be provided to attendees for tools installation prior to the conference.)

#### Level

This tutorial is intended for developers familiar with some of the more advanced features of Ada, including tasking and access types. Hence it is an upper-intermediate to advanced tutorial. Prior experience in the realtime and embedded programming domains is not required but is obviously helpful.

#### Reasons for attending

Developers will understand the unmatched embedded programming facilities provided by Ada. The low-level programming facilities, so often misunderstood, are covered in detail. In addition, overviews of the Ada realtime programming features corresponding to the target environment typically provided by vendors - including that which is used in the workshop - are included. The hands-on developer's workshop will make these facilities concrete.

#### Presenter

Patrick Rogers is product manager for bare-board systems and a Senior Member of the Technical Staff with Ada Core Technologies, specializing in highintegrity and real-time application support. A computing professional since 1975 and an Ada developer since 1980, he has extensive experience in real-time applications in both embedded bare-board and POSIX-based environments. An experienced lecturer and trainer since 1981, he has provided tutorials and courses in real-time programming, software fault tolerance, hard realschedulability time analysis, object-oriented programming, and the Ada programming language. He holds B.S. and M.S. degrees in computer science from the University of Houston and a Ph.D. in computer science from the University of York, England, as a member of the Real-Time Systems Research Group.

# T4 - Ada 2012 (Sub)types and Subprogram Contracts in Practice

Jacob Sparre Andersen, JSA Research & Innovation (Monday 13th, morning)

One of the important, new features in Ada 2012 is a streamlined support for contract-based programming with "contract aspects". They allow the

programmer to specify even more details about types and subprograms in a formal and testable form. If used carefully, they can make package specifications easier to read, and help identifying use and implementation errors faster.

To really make sense, it is important that the contract aspects are applied in a consistent way. The goal of this tutorial is to help the programmer in that direction. It is organised in three sections: An introduction to Ada 2012 contract aspects. Guidance on how one can ensure a consistent application of contract aspects across a whole package. And finally a guided, practical exercise in applying contract aspects.

#### Level

The tutorial is intended to be on an intermediate level. The intended audience is software engineers, who already know Ada, but have not yet used the new "programming by contract" aspects added in Ada 2012. It is advised that the attendees bring laptops (with an Ada 2012 compiler installed) along for the tutorial, even if the practical exercises can be worked through with pen and paper.

#### Reasons for attending

The tutorial will give the participants guidance and practical exercises in applying contract aspects consistently across a set of (sub)types and subprograms. The tutorial is intended to prepare existing Ada programmers for using Ada 2012 contract aspects in future projects.

#### Presenter

Jacob Sparre Andersen has previously given talks and tutorials on the use of Ada 2012 for contractprogramming Ada-Europe based at 2013, DANSAS'13, FOSDEM 2014, Ada-Europe 2014, Linux- Day/Cagliari 2014 and FOSDEM 2015. He has physics, previously taught on courses mathematics, statistics, software engineering and financial instruments.

Jacob Sparre Andersen runs his own consulting company in Hørsholm, Denmark. See http://www.jacob-sparre.dk/cv/ for a full curriculum vitae.

#### T5 - Towards Energy Awareness and Predictability in the Linux Kernel

J. Lelli, ARM Ltd. (Monday 13th, afternoon)

Today's widespread adoption of heterogeneous multiprocessor architectures for the mobile market is calling for integrated software solutions

that are able to meet always raising user quality of service requirements while still operating on battery constrained devices. Hence, such solutions have to necessarily work trading off energy savings for performance and predictability. This tutorial will present the design decisions, implementation details benchmark results of software solutions developed by ARM Ltd. in this context. For what concerns tasks scheduling two approaches will be discussed: the first one, named Heterogeneous MultiProcessing (HMP), has already been used in several products, but is not meant for upstream inclusion; the second one, named Energy Aware Scheduling (EAS), is currently well placed for both upstream and product adoption. Also, implementation of a real-time scheduler targeting applications that requires quality of service guarantees will be presented. Regarding CPU clock frequency selection, a high level description of the Linux kernel CPUFreq subsystem will be given and a proposed solution addressing shortcomings of the current implementation discussed. Open source tools used to evaluate the proposed solutions will be presented as well. Most of the material covered by this tutorial is currently proposed for acceptance in Linux; thus this tutorial is an opportunity to get a detailed update about the Linux kernel. Besides that, this tutorial works also as a gentle introduction to several Linux subsystems and how the Linux kernel development process works in general.

#### Level

Intermediate. No in depth previous knowledge of the topic is required. A general familiarity with some or all the presented subjects is however advised to make actively participating to the tutorial easier.

#### Reasons for attending

The audience will receive a general introduction to several subsystems of the Linux kernel and will also understand how the Linux kernel development works. These basic notions will be complemented with an indepth analysis of the challenges that heterogeneous systems pose concerning predictability and energy efficiency, and how those are addressed. Finally a set of open source tools that make development, analysis and sharing of results will be presented. At the end of the tutorial the audience will then have gained knowledge about such topics and about the tooling that is necessary to develop and understand new technology.

#### Presenter

The presenter has an academic background and hasg given presentations at both academic conferences and industry oriented gatherings. He has also been invited as a keynote speaker on occasions. The presenter is actively working on the topic as part of his role in ARM Ltd. On a daily basis he also interacts with the Linux community and he is known for his contributions to Linux. He already presented similar material to public audiences attending Linux focused conferences (e.g., Linux Plumbers).

**T6 - Access Types and Memory Management in Ada 2012**

J.P. Rosen, Adalog (Friday 17th, morning)

In most languages, pointers are either low-level (pure hardware addresses in C), or implicit (Java, C#).

Ada provides explicit pointers, but of a higher level of abstraction (hence the use of

the term "access"), disconnected from the hardware level, and as safe as possible. In addition, the language includes sophisticated features controlling memory allocation and deallocation. While this has great benefits, it may confuse those who are used to pointers in other languages. Proper usage also requires some difficult to grasp notions, like accessibility levels. This tutorial explains all the issues with Ada access types, from basic usage to sophisticated features like remote access types. Many practical examples demonstrate how to use them and how to control memory allocation, and special emphasis is provided for the latest features offered by Ada 2005 and 2012. A must-attend for all those using access types.

#### Level

Intermediate. Expected audience experience: Casual knowledge of Ada.

#### Reasons for attending

- Understand what makes Ada access types different from other languages' pointers

- Explore rarely taught issues, like accessibility levels, storage pools and subpools, remote access types...

- Learn when and how to use access types and when not to use them.

#### Presenter

JP Rosen is a professional teacher, teaching Ada (since 1979, it was preliminary Ada!), methods, and software engineering. He runs Adalog, a company specialized in providing training, consultancy, and services in all areas connected to the Ada language and software engineering. He is chairman of AFNOR's (French standardization body) Ada group, AFNOR's spokeperson at WG9, member of the Vulnerabilities group of WG9, and chairman of Ada-France.

# T7 - Using Gnoga for Desktop/Mobile GUI and Web development in Ada

#### J.P. Rosen, Adalog

(Friday 17th, afternoon)

Gnoga is a framework and associated tools for developing GUI and Web applications using the Ada language. Gnoga should not be confused with web development frameworks compensating for stateless client/server connections to attempt to create usable UIs, Gnoga uses a bidirectional websocket connection allowing the browser to function as a live rendering engine with instant real time responses for both desktop GUI applications on local machines or remotely over on the web. Gnoga's framework allows for rapid development of client server desktop, mobile and cloud applications and is far more capable for web application development than any existing framework regardless of language. Gnoga is open source under the "non-viral" GPLv3 with runtime exceptions and may be used for proprietary as well as free applications.

#### Level

Intermediate. Expected audience experience: Casual knowledge of Ada.

#### Reasons for attending

- Understand how to make GUI applications in Ada independently of the host system (Windows, Mac, Linux).

- Learn how to use the same tools and framework for desktop, mobile and web applications

# T8 - Parallelism in Ada, C, Java and C#, Today and Tomorrow

Brad Moore, General Dynamics Canada, and Stephen Michell, Maurya Software (Friday 17th, full day)

The tutorial covers the topic of parallelism, and how it can be applied to Ada, C, C#, C++ and Java today. The tutorial starts by showing trends for multicore technologies, how multicore is the direction of the future when it comes to increasing performance. systems become more complex, it will be imperative to make better use of the available hardware. A quick review of Ada tasking and threading concepts should bring everyone up to speed on how one could

apply course grained parallelism using tasks and threads. A simple tutorial example will show how this can be tedious and error prone. The example would also highlight missing features that more fine grained parallelism provides, such as load balancing, automatic dividing the problem to pieces of work suitable size for the available cores, and reverting to sequential behaviour if cores are already loaded, or if the code happens to be executing on a single core processor.

The tutorial will show that a library approach would be beneficial if it can eliminate a lot of the code needed to provide the fine grained parallelism so that the programmer can start with a sequential version of the code, and then make minimal changes to the code to introduce parallelism. A discussion of approaches from other frameworks such as Cilk and OpenMP will then be covered, followed by the introduction of the open source Paraffin libraries.

The notion of a tasklet in Ada, strands/tasks in CILK/OpenMP/C++/C#, and streams in Java is

introduced. The capabilities of Paraffin are described including capabilities for parallel loops, parallel recursion, and parallel blocks, as well as Paraffin load balancing strategies, Work Sharing, Work Stealing, and Work Seeking. The load balancing approaches of Paraffin will be compared with Cilk and OpenMP. Work Seeking is a strategy unique to Paraffin, which generally yields good results.

The tutorial then works through some simple examples of parallel loops, and parallel blocks.

Attendees will be able to experiment and determine the effects of overriding the control choices. Some of the parameters to experiment with include coming up with answers to the following questions:

- How does changing the number of executors affects the performance relative to the number of cores;

- Comparing and contrasting different model/approaches in Ada/Paraffin, OpenMP, CILK, Java, C, C++, and C#;

- The effect of lambdas (Java, C# and C++) on parallel system design and how to use them, compared to nested subprograms in Ada, (and supported in gcc C) and a possible design for lambdas in Ada;

- The possibility of adding lambda like capabilities to Ada will be considered and explored.

- How to use reductions and to preserve order when non-commutative reductions are needed.

- What differences are there between reductions involving reducer functions, vs reductions without such functions?

#### Level

The tutorial material is targeted for an intermediate level of understanding. The material should be of interest to anyone seeking to improve performance of their code on multicore platforms, and make better use of the available processing resources to solve problems. A knowledge of Ada or one or more of the other languages is recommended. Ada 2005 and Ada 2012 features will be used during the presentation but attendees will not need to be familiar with those features, since they are not fundamental to the concepts being presented.

#### Reasons for attending

The attendees will become familiar with divide and conquer parallelism, and how it can be applied in their Ada 2005 and Ada 2012 programs. Attendees will learn how to choose an optimal strategy for a given parallelism opportunity, and develop a better understanding of the effects of various controls and inputs to the parallelism.

#### **Presenters**

Brad Moore works as a software engineer at General Dynamics Canada developing communication systems for military use. A long time user of Ada, he became involved with ISO/IEC JTC1/SC22/WG9, the working group maintaining the Ada standard, during the Ada 2005 standardization process, when he also joined the Ada Rapporteur Group (ARG). Since then he has been involved with WG9 and the ARG in the work associated with producing the Ada 2012 version of the standard. He also has been involved in the real-time community for Ada and has participated in recent IRTAW workshops. In 2009, he happened to attend a parallelism conference where a paper was presented entitled "Reducers and other Cilk++ Hyperobjects". This presentation ignited an interest in parallelism, which led to the development of the Paraffin libraries for Ada. Since then, Brad has been involved in several papers and presentations on the topic of parallelism in Ada. Brad and Steve form part of the gang of four currently developing parallelism proposals to be considered for a future revision of the Ada, standard informally known as Ada 202x. Brad holds a BSc from the University of Calgary, Canada.

Stephen Michell has been a contributing member of the Ada community for more than 30 years. He has concentrated on the safety, security and concurrency aspects of Ada through most of this time. He implemented Ada 83 on a multiprocessor platform, was a distinguished reviewer for Ada 9X, authored the initial Guidance for the use of Ada in high integrity systems, helped to develop the Ravenscar Tasking Profile, and is developing proposals for parallelism in Ada. Stephen is also deeply involved in the standardization of programming languages at the international level, chairing the Canadian mirror committee to ISO/IEC/JTC 1/SC 22 Programming Languages subcommittee and convening ISO/IEC/ JTC 1/SC 22/WG 23 Programming Language Vulnerabilities working group. Stephen holds a B Mathematics from the University of Waterloo, Canada, and a MSc in Mathematics and Systems Engineering from Carleton University, Canada.

Morning tutorial sessions run from 09:30 to 13:00, with a break 11:00-11:30. Afternoon tutorial sessions run from 14:00 to 17:30 with a break 15:30-16:00.

# Supporting the Ada community for over 20 years.

# **VENDOR SESSIONS AND EXHIBITION**

The conference will feature an exhibition in the patio where coffee breaks and lunches will be served. Exhibitors and vendors will also deliver technical presentations in a dedicated session on Tuesday.

# **CONFERENCE VENUE**

Pisa is located in Tuscany, close to the coast and just 80 km from Florence. It is a university city with a population of nearly 100,000. Once a Marine Republic, Pisa stretches along the shores of the Arno River, and occupies a place of honour amongst the most exclusive of art

cities. Its glorious past offers authentic wonders to the tourist, and there is a lot more to see than just the leaning Tower of Pisa, its most popular 'product'.

June is full of events in Pisa, including in the conference week the Saint Patron's festivities (San Ranieri) with the Luminara on the night of June 16. This is definitely worth seeing! Book your hotel in advance - highly recommended as hotels will be in short supply.

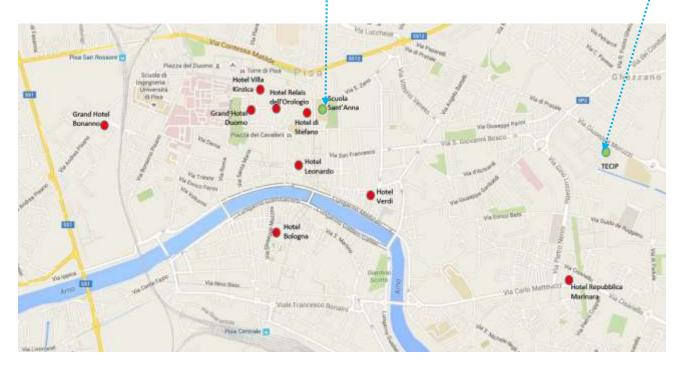

The main conference will be hosted at the Scuola Superiore Sant'Anna, located in the heart of Pisa, just a walk away from Campo dei Miracoli. The events scheduled on Monday and Friday (tutorials and workshop) will be hosted at the TECIP institute. More information on the venue and getting around in Pisa is available at the conference website.

# **CO-LOCATED WORKSHOP**

The conference week features the third International Workshop on Challenges and new Approaches for Dependable and Cyber-Physical Systems Engineering (De-CPS 2016), following the success of the inaugural workshop in 2014 and of its second edition in Madrid in 2015. More information at the workshop website at <a href="http://de-cps-2016.softeam-rd.eu/">http://de-cps-2016.softeam-rd.eu/</a>.

The workshop will take place Friday, June 17th, from 09:30 to 17:30.

### ACCOMMODATION

Hotels in the inner part of Pisa are usually small ones, while in the surrounding areas larger and more modern hotels can be found. Also, hotels in the very centre of the city are typically hosted in old/historic buildings, where rooms and bathrooms might be quite small.

Please note that in the conference week takes place the Saint Patron's festivities (San Ranieri) with the <u>Luminara</u> on the night of June 16. We therefore recommend to make reservations as soon as possible.

The conference website provides a short list of possible comfortable accommodations in Pisa (you can check their location in the pisa map of page 13). As prices vary considerably, we recommend to check the price with the hotel as well as your favourite online booking system.

#### **About PTC**

The PTC Developer Tools Group is part of PTC, Inc. (Nasdaq: PTC), a global provider of technology platforms and solutions that transform how companies create, operate, and service the "things" in the Internet of Things (IoT). The PTC Developer Tools Group provides software engineers with tools to build and execute business and mission-critical applications.

#### PTC ApexAda

PTC ApexAda Developer Enterprise Edition provides a single scalable host deployment environment for Unix and Linux systems that

integrates design, implementation, testing, configuration management, and process management for even the largest application development projects. PTC ApexAda Embedded Developer provides support for cross compilation to PowerPC and Intel processors for several RTOSs and bare metal execution

#### PTC ObjectAda

PTC ObjectAda native products provide host development and execution support for the most popular environments including Windows, Linux and various UNIX operating systems. PTC ObjectAda Real-Time products provide cross development tools on Windows, Linux or UNIX systems which target PowerPC and Intel target processors in support of "bare" hardware execution or in conjunction with popular RTOSs.

To learn more, please visit: www.ptc.com/developer-tools

### REGISTRATION

#### **Conference Registration**

The registration fee for the three days of the technical program (June 14<sup>th</sup> - June 16<sup>th</sup>) includes one copy of the proceedings, coffee breaks, lunches, reception and banquet. The registration fee for a single day of the technical program includes one copy of the proceedings, coffee breaks, and lunch for the day of the registration.

|                                           | Member of Ada-Europe or ACM<br>SIGAda, SIGBED, SIGPLAN |          | Non-member   |          | Student |

|-------------------------------------------|--------------------------------------------------------|----------|--------------|----------|---------|

|                                           | Non academia                                           | Academia | Non academia | Academia |         |

| Early registration<br>(by May 9th)        | 660 €                                                  | 600 €    | 720 €        | 660 €    | 480 €   |

| Late/on-site registration (after May 9th) | 720 €                                                  |          | 780 €        |          | 520 €   |

| Individual registration (per day) 360 €   |                                                        | 390 €    |              | N/A      |         |

#### **Tutorial Registration**

The fee is per tutorial, including tutorial notes and coffee breaks. Lunches are only included when registered for a full day tutorial or two half day tutorials on the same day.

|                                              | Full day or two<br>half days on the<br>same day | Half day |

|----------------------------------------------|-------------------------------------------------|----------|

| Early registration<br>(by May 7th)           | 270 €                                           | 135 €    |

| Late/on-site registration<br>(after May 7th) | 300 €                                           | 150 €    |

#### Workshop Registration

There is a registration fee of 75 € for the De-CPS 2016 workshop, which includes coffee-breaks and lunch on Friday.

#### **Payment and Canceling Information**

Registration may be paid by bank transfer or credit card. Please note that a surcharge of 3% will be added to credit card payments. No registration request will be confirmed until the payment has been processed. To save on administrative costs and postage, receipts will be given out at the conference. Cancellations must be given in writing. A cancellation fee of 5% will be applied to all cancellations. No refunds will be given for cancellations received after the  $22^{nd}$  of May. Substitutions will be accepted.

Student discount: The conference offers a limited amount of passes under the "student discount" category. This scheme provides full access to all of the conference program, including lunches, banquet, and complimentary proceedings. Access to the tutorials may also be requested. Applicants for this discount should contact the conference chair by email, providing a copy of a valid student ID. Students that are co-authors of papers accepted for the conference program are eligible for this discount scheme only if at least one other co-author has registered in full.

Student waiver program: The conference features a novel scheme that allows students to access the conference program for free, but strictly without any other benefit. Applicants for this student waiver program should contact the conference chair by email, providing a copy of a valid student ID. Contingent on logistics, students will be allowed to also apply for this discount scheme directly at the registration desk during the conference, also showing their student ID.

For latest information see the web page at http://www.ada-europe.org/conference2016. For additional information, please contact the Ada-Europe 2016 Chair: Giorgio Buttazzo, E-mail: giorgio@sssup.it.

#### Registration

Please access the registration system at the conference web page: http://www.ada-europe.org/conference2016.

# **CONFERENCE SCHEDULE**

|               | Tuesday 14th                                                                                                                                     | Wednesday 15th                                                                                                                                                  | Thursday 16th                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 9:00 - 9:30   | Welcome & Opening                                                                                                                                |                                                                                                                                                                 |                                                                                                                                        |

| 9:30 - 10:30  | Keynote Talk:  Why the Expressive Power of Languages such as Ada is needed for Future Cyber Physical Systems  Alan Burns, University of York, UK | Keynote Talk:  Challenges for the Automotive Platform of the Future  Valerio Giorgetta, Magneti Marelli, Italy                                                  | Keynote Talk:  The HiPEAC Vision  Marc Duranton, CEA, France                                                                           |

| 10:30 - 11:30 | Coffee & Exhibition                                                                                                                              | Coffee & Exhibition                                                                                                                                             | Coffee & Exhibition                                                                                                                    |

|               | Concurrency & Parallelism                                                                                                                        | Industrial Session: Uses of Ada                                                                                                                                 | Industrial Session: Reliable Software                                                                                                  |

| 11:30 - 12:00 | Modeling and Analysis of Data Flow Graphs using the Digraph<br>Real-Time Task Model<br>Morteza Mohaqeqi, Syed Md Jakaria Abdullah and Wang Yi    | What has the ARG been up to? - Recent and future changes to Ada 2012  Jeff Cousins                                                                              | An update on Programming Language Vulnerabilities<br>Stephen Michell                                                                   |

| 12:00 - 12:30 | Eliminating Data Race Warnings Using CSP  Martin Wittiger                                                                                        | Using Ada's Visibility Rules and Static Analysis to Enforce<br>Segregation of Safety Critical Components<br>Jean-Pierre Rosen and Jean-Christophe Van-Den-Hende | Middleware for distributed and redundant software  Vincent Monfort                                                                     |

| 12:30 - 13:00 | Real-Time Stream Processing in Java  Haitao Mei, Ian Gray and Andy Wellings                                                                      | Automated Testing of SPARK Ada Contracts (AUTOSAC) Christopher Bryan                                                                                            | Model-based design and schedulability analysis for avionic applications on multicore platforms  Wenceslas Godard and Geoffrey Nelissen |

|               |                                                                                                                                                  | Ada Usage in HMI for Onboard Safety Critical Applications Clara María Arcones-Gabriel, Enrique Chicharro-López and Ismael Lafoz-Pastor                          | Fitting the CONCERTO component model approach to AUTOSAR development flow  Andrea Russino, Stefano Puri and Alessandro Zovi            |

| 13:00 - 14:30 | Lunch & Exhibition                                                                                                                               | Lunch & Exhibition                                                                                                                                              | Lunch & Exhibition                                                                                                                     |

|               | Tuesday 14th                                                                      | Wednesday 15th                                                                                                                           | Thursday 16th                                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Vendor Session                                                                    | Presentation Session                                                                                                                     | Program Correctness & Robustness                                                                                                                                      |

| 14:30 - 15:00 | Presentations from conference exhibitors: $\label{eq:AdaCore} A da \textit{Core}$ |                                                                                                                                          | Lessons Learned in a Journey Toward Correct-by-Construction<br>Model-Based Development<br>Laura Baracchi, Silvia Mazzini, Stefano Puri and Tullio<br>Vardanega        |

| 15:00 - 15:30 | Ansys/Esterel PTC                                                                 | ITS EASY Post Graduate School  Projects & Initiatives                                                                                    | Extension of the Ocarina Tool Suite to support Reliable<br>Replication-Based Fault-Tolerance<br>Wafa Gabsi, Bechir Zalila and Mohamed Jmaiel                          |

| 15:30 - 16:00 | Rapita Systems  Vector Software                                                   |                                                                                                                                          | Kronecker Algebra for Static Analysis of Barriers in Ada<br>Robert Mittermayr and Johann Blieberger                                                                   |

| 16:00 - 16:30 |                                                                                   |                                                                                                                                          | Coffee & Exhibition                                                                                                                                                   |

| 16:30 - 17:00 | Coffee & Exhibition                                                               | Coffee, Exhibition & Posters                                                                                                             | An Empirical Investigation of Eager and Lazy                                                                                                                          |

|               | Special Session                                                                   | Testing & Verification                                                                                                                   | Preemption Approaches in Global Limited Preemptive<br>Scheduling                                                                                                      |

|               |                                                                                   | -                                                                                                                                        | Abhilash Thekkilakattil, Kaiqian Zhu, Yonggao Nie, Radu<br>Dobrin and Sasikumar Punnekkat                                                                             |

| 17:00 – 17:30 | Ada and Parallelism  Moderator  Jeff Cousins                                      | Addressing the Regression Test Problem with Change<br>Impact Analysis for Ada<br>Andrew Vaughan Jones                                    | The Polling Effect on the Schedulability of Distributed<br>Real-Time Systems<br>Héctor Pérez, J. Javier Gutiérrez, Michael González Harbour<br>and J. Carlos Palencia |

| 17:30 – 18:00 | Presenters<br>Brad Moore and S. Tucker Taft                                       | Test Case Prioritization Using Online Fault Detection<br>Mohsen Laali, Huai Liu, Margaret Hamilton, Maria<br>Spichkova and Heinz Schmidt | Combining Time-Triggered Plans with Priority Scheduled<br>Task Sets<br>Jorge Real, Sergio Sáez and Alfons Crespo                                                      |

| 18:00 – 18:30 | Open floor discussion                                                             | An Experience in Ada Multicore Programming: Parallelisation of a Model Checking Engine Franco Mazzanti                                   | Closing Best Presentation Award Presentation of future related events                                                                                                 |

| 18:30         | Ada-Europe General Assembly                                                       |                                                                                                                                          |                                                                                                                                                                       |

Welcome Reception

Banquet and Best Paper Award

# **ORGANIZATION**

**Conference Chair**

Giorgio Buttazzo Scuola Superiore Sant'Anna

**Program Co-Chairs**

Marko Bertogna Univ. of Modena and Reggio Emilia

Luís Miguel Pinho CISTER/INESC-TEC, ISEP

**Special Session Chair**

Eduardo Quiñones

Barcelona Supercomputing Center

**Tutorial and Workshop Chair**

Jorge Real Universitat Politècnica de València

**Industrial Co-Chairs**

Marco Di Natale Scuola Superiore Sant'Anna Tullio Vardanega Università di Padova

**Publication Chair**

Geoffrey Nelissen CISTER Research Centre/ISEP **Exhibition Co-Chairs**

Paolo Gai Evidence Srl Ahlan Marriott White Elephant GmbH

**Publicity Co-Chairs**

Mauro Marinoni Scuola Superiore Sant'Anna

Dirk Craeynest Ada-Belgium & KU Leuven

Local Chair

Ettore Ricciardi

ISTI-CNR, Pisa

#### **Program Committee**

Mario Aldea (Universidad de Cantabria), Ted Baker (NSF), Marko Bertogna (University of Modena and Reggio Emilia), Johann Blieberger, (Technische Universität Wien), Bernd Burgstaller (Yonsei University), Albert Cohen (INRIA), Juan A. de la Puente (Universidad Politécnica de Madrid), Michael González Harbour (Universidad de Cantabria), J. Javier Gutiérrez (Universidad de Cantabria), Jérôme Hugues (ISAE), Raimund Kirner (University of Hertfordshire), Albert Llemosí (Universitat de les Illes Balears), Franco Mazzanti (ISTI-CNR), Stephen Michell (Maurya Software), Jürgen Mottok (Regensburg University of Applied Sciences), Laurent Pautet (Telecom ParisTech), Luís Miguel Pinho (CISTER/ISEP), Erhard Plödereder (University of Stuttgart), Eduardo Quinoñes (Barcelona Supercomputing Center), Jorge Real (Universitat Politècnica de València), Christine Rochange (IRIT/University of Toulouse), José Ruiz (AdaCore), Sergio Sáez (Universitat Politècnica de Valencia), Martin Schoeberl (Technical University of Denmark), Tucker Taft (AdaCore), Theodor Tempelmeier (University of Applied Sciences Rosenheim), Elena Troubitsyna (Åbo Akademi), Santiago Urueña (GMV), Tullio Vardanega (Università di Padova).

#### **Industrial Committee**

Ian Broster (Rapita Systems), Jørgen Bundgaard (Ramboll), Dirk Craeynest (Ada-Belgium & KU Leuven), Arne Hamann (Bosch), Ismael Lafoz (Airbus Defence & Space), Ahlan Marriott (White Elephant), Paolo Panaroni (Intecs), Paul Parkinson (Wind River), Eric Perlade (AdaCore), Jean-Pierre Rosen (Adalog), Jacob Sparre Andersen (JSA Consulting), Claus Stellwag (Elektrobit AG), Jean-Loup Terraillon (European Space Agency), Sergey Tverdyshev (SysGO), Rod White (MBDA).

# **SPONSORS**

Springer Verlag publishes the proceedings of the conference, in the Lecture Notes in Computer Science series (LNCS 9695)

Cover Photo Baptistry, Duomo and Leaning Tower at Pisa, around 1830. Artist: Rauschenfels von Steinberg.